차세대 AI 컴퓨팅 성장: 고려해야 할 전력 공급 트레이드오프

자료제공/텍사스 인스트루먼트

IT 랙 전력은 향후 2 ~ 3년 내에 1MW를 넘어설 것으로 예상된다. AI 서버에서 더 높은 전력 밀도를 달성해야 할 필요성이 커지면서, 기존의 48V 또는 54V 버스에서 800V DC의 고전압 DC 버스로 전환하는 흐름이 나타나고 있다. 800V DC로의 전환은 시스템 차원에서 높은 효율과 높은 전력 밀도의 에너지 변환을 구현하는 데 있어 여러 도전 과제를 동반하지만, 동시에 IT 서버 랙 내부의 전력 전달 아키텍처를 재검토할 수 있는 기회도 제공한다.

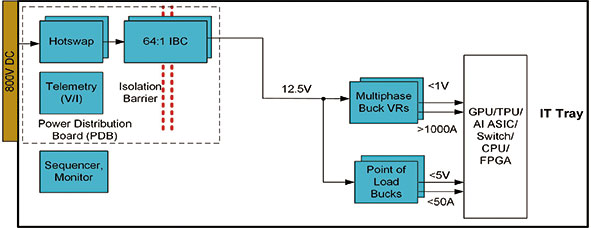

그림 1에 나타난 것처럼, 800V DC로의 전환은 전력 전달 아키텍처 자체를 변화시킨다. 이제 IT 트레이의 입력은 800V DC가 되며, 이에 따라 돌입 전류를 제어하고 고전압 버스에 대한 안전한 연결을 관리하기 위한 고전압 핫스왑 회로가 필요하다. 전력 분배 보드에는 고변환비 중간 버스 컨버터(IBC)가 배치되어 800V DC의 에너지를 더 낮은 중간 버스 전압으로 변환한다. 이 시스템에서는 강화 절연(reinforced isolation)을 갖춘 절연 장벽을 통해 고전압 시스템과 저전압 시스템을 분리할 수도 있다.

이후의 전력 아키텍처는 48V DC 기반의 AI 컴퓨팅 트레이와 유사한 구조와 특성을 가지게 되지만, 여러 가지 변형이 가능하다. 한 가지 옵션은 800V에서 50V로 변환하는 IBC를 사용한 뒤, 다시 50V에서 12.5V 또는 6.25V로 변환하는 IBC를 단계적으로 구성하는 방식이다.

데이터센터 운영자의 주요 목표 중 하나는 종단 간(end-to-end) 에너지 변환 효율을 극대화하는 것이다. 이는 데이터센터의 운영 비용을 절감하고, 전력 손실로 인해 발생하는 열과 그에 따른 냉난방(HVAC) 부담을 줄이며, 에너지 소비를 AI 가속기나 프로세서 및 기타 지원 회로와 같은 실제 부하에 집중시키는 데 기여한다. 이와 함께 중요한 목표로는 전력 부품을 위한 회로 기판 공간이 제한된 상황에서의 소형화, 높은 신뢰성, 그리고 다상 전압 레귤레이터와 포인트-오브-로드(point-of-load) 벅 컨버터의 과도 응답 특성과 같은 성능 요구 사항을 충족하는 것이 있다.

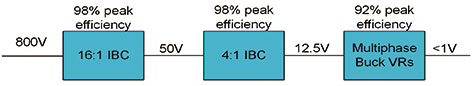

한 가지 접근 방식은 기존의 48V 전력 아키텍처에 고전압 IBC를 단순히 추가하는 것이다. 그림 2는 이러한 3단 변환 아키텍처를 보여준다. 이 방식의 장점은 기존 48V 기반 전력 아키텍처 설계의 대부분을 재사용할 수 있다는 점이다. 예를 들어, 전압 변환 비가 16:1인 고전압 IBC(즉, 출력 48V)를 가정해 보자. 이때 16:1 IBC의 최대 효율이 98%, 50V에서 12.5V로 변환하는 4:1 IBC의 최대 효율이 98%, 그리고 12.5V에서 코어 전압으로 변환하는 다상 전압 레귤레이터의 효율이 92%라고 가정하면, 800V DC에서 코어 전압까지의 전체 최대 변환 효율은 약 88% 수준이 된다.

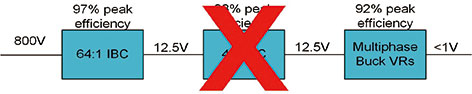

더 낮은 전압 레귤레이터 입력 전압을 선택했을 때의 장점은 더 높은 스위칭 주파수로 동작할 수 있다는 점이다. 이는 전력단의 크기를 줄이고, 과도 응답 성능을 개선하며, 백사이드(후면) 실장(수직 전력 전달, VPD)을 가능하게 하는 데 기여할 수 있다. 여기서 “왜 변환 단계를 3단이나 두어야 하지? 고효율·고변환비 IBC와 고성능 전압 레귤레이터, 2단으로 단순화할 수는 없을까?”라는 질문이 나올 수 있다. 이제 그림 3에 제시된 것처럼, 그 2단 아키텍처를 살펴보자.

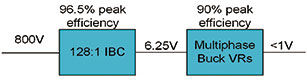

이 접근 방식은 더 이상 4:1 IBC가 필요 없기 때문에, 시스템 크기를 줄이고 비용을 최소화할 수 있는 잠재적인 장점을 제공한다. 그림 4는 이러한 가능성을 갖는 전력 아키텍처를 보여준다.

이 아키텍처의 가장 큰 과제는 128:1 IBC의 출력 전류가 매우 크다는 점이다. 시스템이 약 15kW ~ 20kW의 전력을 전달한다고 가정하면, 6.25V에서의 전류는 약 2.4kA ~ 3.2kA에 달한다. 6.25V 중간 버스에서의 회로 기판 손실을 합리적인 수준(1 ~ 2% 미만)으로 억제하려면, 버스바와 같은 매우 굵은 도체가 필요하다. 또한 이러한 전류 수준을 충족하기 위해서는 128:1 IBC를 여러 개 병렬로 구성해야 할 가능성이 크다.

[그림 5] 128:1 IBC를 적용한 800V 2단 변환 아키텍처

결론

800V DC 전력 아키텍처로의 전환은 전체 변환 효율, 크기, 성능 간의 트레이드오프를 고려한 전력 전달 설계 방식에 대해 다시 한 번 논의하게 만든다. 텍사스 인스트루먼트(TI)는 갈륨 나이트라이드(GaN) 전력 스테이지, 디지털 전력 컨트롤러, 다상 벅 전압 레귤레이터, DC/DC 포인트-오브-로드 벅 컨버터, 핫스왑 컨트롤러, 절연 게이트 드라이버 등 폭넓은 포트폴리오를 통해 업계가 이러한 전환을 원활히 추진할 수 있도록 지원하고 있다.

엔비디아(NVIDIA)와의 협업을 통해 800V DC 아키텍처를 지원하는 전력 관리 솔루션을 개발함으로써, TI의 제품들은 전력 아키텍처의 핵심 지점에서 신뢰성 높은 전압 변환을 보장한다. 동시에 48V 및 800V 전력 생태계에 필요한 보호, 모니터링, 텔레메트리 기능을 제공하며, 전력망에서 AI 가속기까지 이르는 구간 전반에 걸쳐 고효율·고전력 밀도의 전력 변환을 구현한다.

기사입력 : 2026-02-03

에지 AI 가속 Arm® Cortex®-M0+ MCU가 전자 기기에 더 많은 지능을 제공...

작성자 : 텍사스 인스트루먼트

이더넷이 소프트웨어 정의 차량으로의 전환을 가속화하는 방법

작성자 : Madison Ecklund 외 1인

차세대 AI 컴퓨팅 성장: 고려해야 할 전력 공급 트레이드오프

작성자 : 텍사스 인스트루먼트

TOLL GaN으로 태양광 에너지 시스템의 한계를 확장하다

작성자 : Sai Madhav 외 1인

스마트 전력 분배: 자동차 기술의 미래를 형성하다

작성자 : David Martinez

초음파를 이용한 가스 유량 감지

작성자 : 레오나르도 에스테베즈 외 1인

GaN FET 기반의 10kW 단상 스트링 인버터의 설계 고려 사항

작성자 : Riccardo Ruffo 외 1인

새로운 접지 레벨 트랜스레이터로 오프셋 문제를 해결하는 방법

작성자 : TI 코리아

LiDAR의 도약: 정밀한 장거리 감지 기능으로 더 안전한 차량 개발

작성자 : Anthony Vaughan

작지만 강력한 성능의 MCU를 최적화하는 방법

작성자 : Alex Grudzinski