SERDES 디자인을 위한 더 효율적인 솔루션이 있을까요?

글/Neil Fernandes, Mentor, A Siemens Business

서론

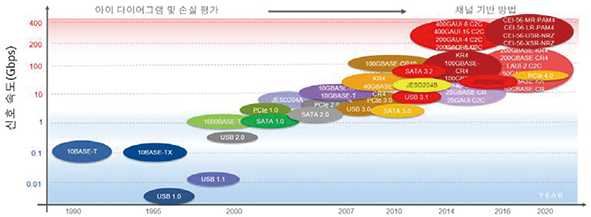

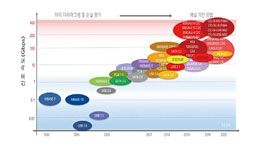

직렬화-역직렬화(SERDES) 채널을 설계하는 복잡한 작업은 최근 몇 년 동안 더 어려워졌다. 예를 들어 PCIe(PCI Express) 4세대 및 USB(Universal Serial Bus) 3.1과 같은 산업 프로토콜은 단일 기술 세대에서 신호 속도가 두 배로 증가했다(그림 1). 데이터 속도가 향상됨에 따라 업계는 인터페이스 분석을 위해 채널 운영 마진과 같은 새로운 방법을 채택해야 했다. 그러나 비용을 최소화하기 위해 보드 소재는 이전 세대의 기술과 동일하게 유지되었다.

DDRx(Double Data Rate) 기술의 발전과는 달리, SERDES 기술의 발전은 매우 빠르게 이루어졌다(그림 1). Signal Integrity Academy 학장 겸 Teledyne LeCroy Front Range Signal Integrity Lab 소장인 Eric Bogatin은 “오늘날의 신호 속도에는 초고속 설계를 위해 신호 무결성 분석을 수행하는 채널 기반 프로토콜 방법이 필요하다. 하지만 이러한 방법에는 높은 수준의 전문성이 필요하기 때문에 조직 병목 현상이 발생하게 된다”라고 말했다. 이러한 변화가 하드웨어 설계 엔지니어에게 어떤 영향을 미쳤을까?

[그림 1] 직렬화-역직렬화(SERDES) 프로토콜의 발전

오늘날 고속 SERDES의 당면 과제

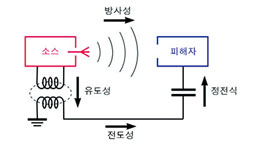

하드웨어 엔지니어(그림 2)는 다음과 같은 산업 관련 문제에 직면해 있다. 새로운 SERDES 사양을 이해하는 것이 점점 더 복잡해지고 있다. PCI Express 4세대와 같은 기술의 사양은 1,000페이지가 넘는다.

[그림 2] 업계 관련 문제에도 불구하고 고속 상호 연결을 설계

프로토콜 사양의 세부 사항을 정확하게 이해하려면 SERDES 전용 교육이 필요하다. 이 교육은 받기 어려울 수 있으며, 무료로 제공되지 않는다. 5Gbps 이상의 채널에 사용되는 IBIS-AMI 버퍼 모델이 거의 없다. 사용 가능한 모델은 IBIS 위원회의 승인을 받지 않은 사양에 따라 만들어진 것이다. 예를 들어 Xilinx에서 수행한 테스트에 따르면 동일한 IBIS-AMI 모델이 서로 다른 EDA 도구에서 서로 다른 시뮬레이션 결과를 반환했다. 어떤 결과가 올바른 것일까?

① SERDES 채널 분석 및 설계에는 EM(전자기) 전문성이 필요하다. 일부 설계팀은 사내에 SI 또는 EM 전문가를 보유하고 있지 않는다. 따라서 PCB 설계를 정확하게 나타내는 S-파라미터 모델을 생성해야 하는 추가적인 부담이 하드웨어 설계 엔지니어에게 가중된다.

② SERDES 사양은 규정 준수 기관에 의해 작성되며 프로토콜 간에 일치하지 않는다. 예를 들어 지터는 PCI Express 사양과 IBIS-AMI 사양에서 서로 다른 방식으로 지정된다.

③ 여러 SERDES 프로토콜이 동일 PCB(인쇄 회로 기판) 설계에 존재한다. 프로토콜 간 지식 이전이 거의 없을 경우에는 모든 프로토콜에 대해 상호 연결 분석을 처음부터 시작해야 한다.

④ 설계 주기가 단축되면서 하드웨어 엔지니어는 때로 모호하게 작성된 사양을 읽을 시간이 없다.

⑤ SERDES 사양은 무료가 아니며 쉽게 액세스할 수도 없다.

SERDES 채널 분석

하드웨어 엔지니어는 업계 관련 문제에 마주치는 것 외에도 여러 소프트웨어 도구를 사용하여 SERDES 채널을 수동으로 추출, 모델링, 분석해야 한다. 이 프로세스는 세부적인 내용에 대한 높은 주의가 요구되므로 시간이 오래 걸리고 오류가 발생하기 쉽다. 단계는 다음과 같다.

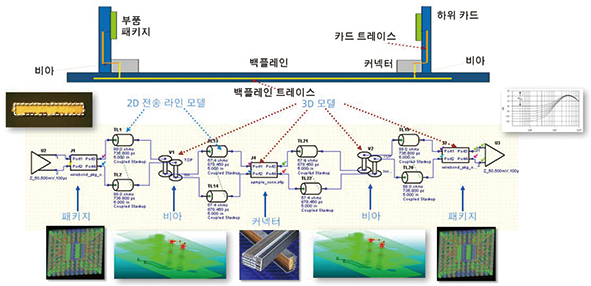

① 상호 연결을 3D 및 2D 필드 솔버로 각각 모델링해야 하는 섹션으로 나눔

② 3D 필드 솔버를 사용하여 모델링된 섹션의 S파라미터 모델을 생성

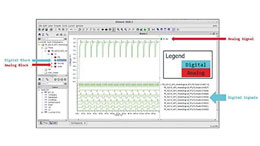

③ 3D 필드 솔버의 S-파라미터 모델을 2D 필드 솔버 모델링 섹션과 다시 연결하여 전체 상호 연결 표시(그림 3)

④ 주파수 도메인 분석 또는 규정 준수 확인을 위해 전체 상호 연결의 S-파라미터 모델을 내보냄

[그림 3] SERDES 채널 분해 및 모델링

또한 SERDES 채널 분석에는 최종 모델(위의 2단계)이 정확한지 확인하기 위한 깊이 있는 EM(전자기) 전문성이 필요하다. 예를 들어, 귀환 경로가 어디에 있는지를 이해하지 못한 상태에서 상호 연결을 적극적으로 분할하거나 잘라내면(1단계) 부정확한 S-파라미터 모델이 생성된다(2단계). 반대로, 상호 연결을 보수적으로 잘라낼 경우에는 시뮬레이션 실행 시간과 메모리 소비가 증가한다. 또한 매우 높은 주파수까지 유효한 포트를 생성하고(2단계), 잘라낸 가장자리의 반사를 억제하는 데 필요한 적절한 경계 조건을 지정하는 것(2단계)은 간단한 작업이 아니다.

더 나은 SERDES 솔루션이 있을까?

기술 및 업계 관련 문제는 제품 안정성 향상, 비용 절감, 출시 기간 단축 등의 비즈니스 과제와 더불어 하드웨어 설계 엔지니어에게 엄청난 부담을 준다. 시뮬레이션 범위를 늘리고 설계 주기 시간을 단축하면서 하드웨어 엔지니어의 부담을 완화할 수 있다면 어떨까?

HyperLynxⓇ에는 다음과 같은 SERDES 전용 기능이 포함되어 있다.

① 지능형 자동 채널 추출과 내장된 EM 전문성

② 인터페이스 레벨 채널 규정 준수 확인

③ 레이아웃 전 설계 살펴보기

이러한 기능들이 합쳐져서 SERDES 채널 분석을 자동화한다. 각 채널을 분석하는 데 소요되는 시간을 대폭 단축하여 설계를 더욱 신속하게 재회전하거나 제작하고 완제품을 더 빨리 출시할 수 있다. 설계 문제를 식별하고 제품 신뢰성을 향상시키는 데 필요한 EM 및 프로토콜별 전문성을 제공한다. 또한 매우 높은 주파수 상호 연결을 분석하는 데 필요한 높은 정확도를 제공한다.

지능형 자동 채널 추출과 EM 전문성

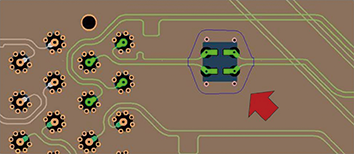

HyperLynx에서는 버튼을 누르는 것만으로 SERDES 채널 추출 및 모델링의 전체 프로세스를 자동으로 수행할 수 있다. 우선, 설계 레이아웃을 기반으로 신호넷의 어떤 부분을 3D 필드 솔버에서 모델링해야 하는지 식별한다(그림 4). 3D 영역은 귀환 경로 연속성과 최종 S-파라미터 모델의 정확성을 보장하기 위해 생성된다.

[그림 4] 설계 및 라우팅을 기반으로 3D 모델링을 위해 자동 식별된 영역

부적절한 포트 생성 또는 잘못된 경계 조건은 물리적/실제 설계 행동을 반영하지 않는 결과 또는 눈에 잘 띄지 않는 인위적 효과를 생성할 수 있기 때문에 HyperLynx는 도구 내에서 직접 문제를 정확하게 모델링하는 데 필요한 EM 전문성을 내장하고 있다. 포트 생성, 경계 조건, 메싱 설정 등은 모두 해결 중인 문제의 클래스에 따라 지정된다. HyperLynx에서는 내장된 EM 전문성이 시뮬레이션 결과의 신뢰성을 보장하므로 전자기 전문가를 고용할 필요가 없다.

견고한 레퍼런스 동박 형태와 인접한 신호넷 부분에서는 HyperLynx 2.5D 필드 솔버의 전송 라인 모델로도 충분하다. 3D 필드 솔버의 S-파라미터 모델이 2.5D 전송 라인 모델과 자동으로 연결되며, 3D S-파라미터 모델에 포함된 트레이스 세그먼트를 고려하여 트레이스 세그먼트가 이중으로 계산되는 것을 방지한다.

수동으로 수행할 경우, 이 프로세스는 시간이 오래 소요된다. 중요한 채널을 S-파라미터 모델로 쉽게 내보내 추가적인 주파수 도메인 분석을 수행하거나, 프로토콜 규정 준수 확인을 위해 HyperLynx SERDES 마법사에 자동으로 입력할 수 있다(다음 섹션).

설계에 따라, 3D 필드 솔버가 S-파라미터 모델을 생성하는 데 많은 시간과 메모리가 필요할 수 있다. 속도를 높이기 위해 HyperLynx는 동일한 라우팅 패턴을 여러 번 사용하는 설계를 검색할 수 있다. 따라서 3D 필드 솔버에서 생성된 S-파라미터 모델을 후속 분석에 재사용할 수 있다. 라우팅 패턴은 일반적으로 SERDES 채널에서 재사용되기 때문에 설계에서 모든 SERDES 채널의 분석 속도를 크게 향상시킵니다.

인터페이스 레벨 채널 규정 준수 확인

SERDES 사양은 해석하기 어려우며, 점점 단축되는 설계 주기는 기술 사양을 읽는 데 사용할 수 있는 시간을 줄였다. 하지만 채널 규정 준수를 위해서는 이러한 사양을 이해하는 것이 매우 중요하다.

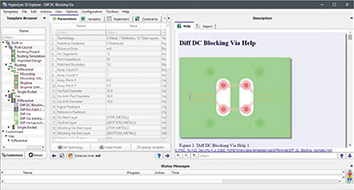

HyperLynx는 도구 내에서 직접 채널을 평가하는 데 필요한 프로토콜별 정보가 내장되어 있다. 간단하고 직관적인 마법사에서 시뮬레이션 결과 기반 측정이 가능하다. 분석할 디퍼렌셜 페어를 선택하고 설계에서 준수해야 하는 프로토콜을 선택하기만 하면 된다(그림 5). HyperLynx는 필요한 모든 분석을 수행하고, 시뮬레이션 결과를 측정하고, 동료와 공유할 수 있는 통과/실패 HTML 보고서를 생성한다.

[그림 5] 내장된 인터페이스 레벨 채널 규정 준수 확인

HyperLynx를 사용하면 하드웨어 엔지니어가 프로토콜을 읽고 특정 측정 및 분석을 위해 채널을 설정하고 시뮬레이션하는 데 소요되는 시간을 절약할 수 있다. 또한 SERDES 프로토콜의 잘못 해석할 가능성을 방지한다. OIF-CEI, PCI Express, IEEE 802.3, USB 등 25개 이상의 SERDES 프로토콜을 지원하는 HyperLynx 규정 준수 마법사는 동일한 설계의 여러 SERDES 프로토콜에서 빠르고 쉽게 사용할 수 있다.

IBIS-AMI 벤더-버퍼 모델은 일반적으로 5Gbps 이상의 채널을 검증하는 데 사용된다. IBIS-AMI 모델은 종종 찾기가 어렵거나 설계 주기의 극후반에만 사용할 수 있다. 버퍼 모델을 사용할 수 없는 경우 하드웨어 설계 엔지니어는 내장된 프로토콜 규격 버퍼 및 패키지 모델을 HyperLynx 안에 있는 채널과 연결할 수 있다.

부품 제조업체에서 프로토콜 규격 부품을 공급하는 한, 참조 버퍼 및 패키지 모델을 사용하여 전체 채널이 프로토콜을 준수하는지 확인할 수 있다. Behavioral 모델을 사용하면 IBIS-AMI 모델을 사용할 때보다 훨씬 더 빠르게 채널 규정 준수를 확인할 수 있다.

SERDES 버퍼에는 아이 오프닝(Eye Opening)을 최대로 하기 위해 사용되는 프리커서와 포스트커서 균등화 탭을 내장하고 있다. 최적의 탭 설정을 찾는 것은 각 탭에서 여러 번의 시행착오 시뮬레이션을 반복해야 하고 각 탭에서 나올 수 있는 다양한 값을 고려해야 하므로 힘든 프로세스이다. 예를 들어 각각 6개의 사용 가능한 값이 있는 5개의 탭 버퍼는 최적의 탭 값을 찾기 위해 7,700개 이상의 시뮬레이션을 평가해야 한다.

HyperLynx는 프로토콜 참조 아키텍처와 DFE(Decision Feedback Equalization), CTLE(Continuous Time Linear Equalization) 등의 제약 조건을 기반으로 최적의 균등화 설정을 식별할 수 있게 도와준다. 채널을 분석하는 데 소요되는 시간을 단축하는 동시에 설계 신뢰도를 높이기 위해 아이 다이어그램(eye diagram)을 생성한다. 채널 최적화는 레이아웃 전후 심사 단계 모두에서 수행될 수 있다.

레이아웃 전 설계 탐색 및 최적화

대부분의 SERDES 채널 분석은 일반적으로 PCB 설계 주기의 레이아웃 전 단계에서 수행된다. 여기에는 기본 지오메트리/구성(예: 비아 패턴용)을 생성한 후에 이를 수정하여 구조를 최적화하는 것이 포함된다. 편집할 수 있는 3D 구조의 파라미터 수와 여기에서 나올 수 있는 다양한 값을 고려할 때 토폴로지 구성의 수는 무한한다.

토폴로지를 설정하고 시뮬레이션 결과를 생성하는 데 걸리는 시간 때문에 대부분의 하드웨어 엔지니어는 솔루션 공간을 철저히 탐색하지 않는다. 이전에 통과한(또는 거의 통과한) 결과를 생성한 토폴로지를 사용하거나, 구성을 초과 설계한다. 이는 설계 제조 비용을 증가시키고 제품 신뢰성에 영향을 미칠 수 있다.

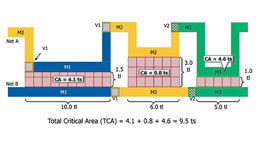

HyperLynx는 하드웨어 엔지니어가 특정 설계 지오메트리를 최적화하는 데 도움이 되는 템플릿 기반 접근 방식을 사용한다(그림 6). 디퍼런셜 비아, BGA(Ball Grid Array) 브레이크아웃 및 브레이크인, 직렬 차단 캐패시터 마운팅 등의 구조에 대한 템플릿과 관련 파라미터를 수정할 수 있다. 파라미터 값은 ‘실험 시스템’에서 다양한 조합으로 스위프될 수 있으며, 측정 제약 조건을 적용하여 특정 기준에 부합하는 구성을 식별하고 설계 마진을 극대화할 수 있다.

[그림 6] 디퍼런셜 DC 차단 비아 구성을 위한 템플릿

최종 구성 및 관련 S-파라미터 모델을 추가 시간-도메인 또는 주파수-도메인 분석에 사용할 수 있다. 또한 최종 S-파라미터 모델을 스위프하여 중요한 상호 연결을 최적화할 수 있다.

결론 및 고객 검증

HyperLynx는 최신 SERDES 상호 연결을 종합적으로 분석할 수 있는 업계 최초의 엔드 투 엔드 자동 솔루션을 하드웨어 엔지니어에게 제공한다. 이전에는 하드웨어 엔지니어가 설계 주기 부담과 전체 보드 레벨 SERDES 분석을 가능하게 하는 기술의 부족으로 인해 수십 개의 신호넷만 분석했다.

HyperLynx는 지능형 자동 채널 추출, 인터페이스 레벨 채널 규정 준수 확인, 레이아웃 전 탐색 및 최적화를 통해 설계에서 모든 SERDES 채널을 빠르고 정확하게 분석할 수 있다. 또한 HyperLynx를 사용하면 솔루션 공간을 적시에 탐색하여 설계 파라미터를 최적화하고 마진을 극대화할 수 있다.

Signal Integrity Journal 편집자, University of Colorado - Boulder 겸임교수이자 Teledyne LeCroy Signal Integrity Academy 학장인 Eric Bogatin은 이렇게 말했다. “고속 직렬 링크의 데이터 속도가 증가함에 따라 프로토콜 범위 내에서 균등화 설정에 의해 제한을 받으면서 허용 가능한 비트 오류 비율의 채널을 설계하려면 높은 수준의 전문성이 필요하다. Mentor의 새로운 자동 채널 분석기는 마치 전문가를 얻은 것과 같다. 사인오프 전에 설계 분석을 실행하면 많은 재료, 비아 및 전송 라인 문제가 최종 설계에 들어가기 전에 발견된다. 그리고 최종 채널에 대해 새로운 규정 준수 분석기는 프로토콜의 제약 조건을 충족할 수 있는 최적화된 균등화 설정을 권장한다. 이러한 혁신은 모든 하드웨어 엔지니어가 밤에 숙면을 취할 수 있게 도와줄 것이다.”

EM 및 프로토콜별 전문성이 내장된 HyperLynx는 설계팀에 전자기 전문가가 없어서 낭패를 보는 일이 없도록 만든다. 하드웨어 설계 엔지니어는 불명확한 사양을 읽고 해석하는 데 시간을 낭비하지 않고 상호 연결 설계에 집중할 수 있다. 또한 HyperLynx에 내장된 프로토콜 규격 버퍼 및 패키지 모델 덕분에 적절한 IBIS-AMI 버퍼 모델을 찾느라 또는 설계 주기에 너무 늦게 모델을 찾음으로써 발생하는 스트레스도 해소된다.

Sintecs B.V.의 상무이사 Hans Klos는 이에 동의하며 “우리는 HyperLynx를 사용하여 dReDBox 프로젝트를 위한 고속 PCIe SERDES 인터페이스를 처음으로 제대로 구현하는 데 성공했다. 우리 회사의 하드웨어 설계자들은 SERDES 규정 준수 마법사를 사용하여 인터페이스 설계 최적화 중에 최종 인터페이스 규정 준수 확인을 위해 신속하게 작업을 반복한다”라고 말했다.

아날로그 설계를 위한 EDA 툴은 어떻게 진화하고 있는가?

조회수 821회 / Siemens EDA

전자제품 인터페이스의 설계 라이프사이클

조회수 599회 / David Wiens

전기 디자인 룰 체크(DRC)를 자동화하는 방법

조회수 1260회 /

지멘스EDA 수석부사장.jpg)

2022년 시스템 및 설계 툴, 방법론의 시장 전망

조회수 1250회 / 지멘스

임계 영역을 이용한 자동차 IC의 테스트 품질 향상

조회수 1683회 / RON PRESS

SERDES 디자인을 위한 더 효율적인 솔루션이 있을까요?

조회수 1756회 / Neil Fernandes

지멘스 EDA 포럼 2021 열려, ‘Silicon to Systems’ 주제로 최신 설계 방...

조회수 1152회 / Joseph Sawicki

자동화된 EMC 분석을 PCB 레이아웃에 추가

조회수 1232회 / SIEMENS

DFT를 향한 성능 저하 없는 상향식 접근방식

조회수 2555회 / Geir Eide

PDF 다운로드

회원 정보 수정