차세대 IC 패키징에 필요한 차세대 설계 솔루션 ④

글/KEITH FELTON, MENTOR A SIEMENS BUSINESS

서론

멀티 다이 이종 및 단일 패키징은 변함없이 ‘모어 댄 무어(More than Moore)’ 방식에서 전망이 밝은 ‘그 이상(more)’을 의미하며 폼팩터와 기능성 개선을 위한 새로운 방식으로 활용되고 있고, 여러 가지 기술 노드를 사용하여 제조된 멀티 다이에 적합한 통합 수단으로서 자리매김하고 있다. 여러 장치를 단일 패키지로의 이종 및 동종 통합은 장치 기능성 보강, 출시 기간 단축 및 실리콘 수율 복원성과 같은 목표를 달성하도록 지원한다.

이 연작의 첫 번째 글에서는 고급 IC 패키징과 함께 나타난 새로운 난제에 관해 알아보고 이종 멀티 다이 및 복수 기판 설계, 검증과 사인오프에 적합한 검증된 설계 방법론으로서 시스템 레벨 디지털 트윈 프로토타이핑 방식이 주목받는 이유를 설명하였다. 두 번째 글에서는 디지털 트윈 방법론으로 지원되는 멀티 도메인 및 교차 도메인 통합을 중점적으로 다룬다. 세 번째 글에서는 현행 및 향후의 고급 IC 패키지를 다루기 위해 필요한 솔루션의 확장성과 범위에 대해 설명하고 예측 가능한 정밀 제조 전달을 위해서는 정확히 무엇이 필요한지 알아보았다.

이 글 에서는 이상적인 사인오프를 더욱 효율적이고 빠르게 달성할 수 있도록 하는 여러 가지 방법, 동급 최고의 툴과 모범 사례를 소개한다.

이상적인 사인오프

이상적인 사인오프란 설계자가 파운드리나 아웃소싱 반도체 어셈블리 및 테스트(OSAT) 제공업체에서 승인한 사인오프 디자인 룰 검사(DRC) 툴 및 제공된 PDK/PADK는 물론 설계 규칙 매뉴얼(DRM)과 같은 다른 사인오프 관련 문서를 사용하는 것을 말한다. 이 경우 일반적으로 제조되는 기판(인터포저, 패키지)의 제조 사인오프만 달성할 수 있다.

고급 IC 패키지의 경우 이상적인 사인오프를 이루려면 보다 종합적인 일련의 검사를 거쳐야 한다. 그렇지 않으면 조립된 장치의 총 수율이 목표와 일치하지 않고, 예상 어셈블리 및 테스트 원가를 초과하게 된다. 종합적인 이상적 사인오프에는 최소 요건으로 물리적 검증, 연결 검사(즉 LVS)와 이종 어셈블리 레벨 검증(즉 LVL)이 포함되어야 한다. 이와 같은 종합적인 사인오프 검사 프로세스를 거치면 재작업이 필요한 많은 문제점을 드러낼 수 있다.

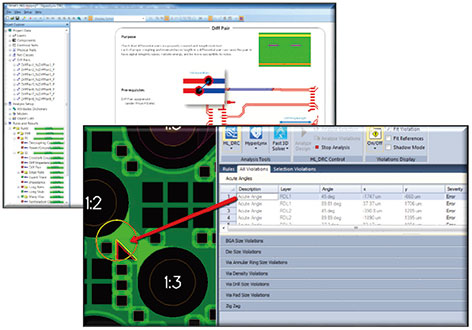

이러한 문제가 제대로 감지되지 않으면 프로젝트 지연, 원가 인상으로 이어지기 쉽고 제조 일정을 놓치게 될 수도 있다. 이를 방지하는 한 가지 방법으로는 ‘초기 검증’ 설계 플로우를 구현하는 것이다. 설계 내에서 이 플로우를 실행하여 명백한 사인오프 오류를 초기에 찾아내 제거하는 것이다. 이런 방법론을 사용하면 전체 사인오프 오류의 80% 이상을 제거하여 사인오프 병목 현상과 지연을 예방할 수 있다.

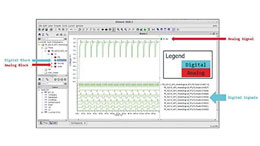

[그림 1] 통합된 설계 내 지오메트리 기반 DRC를 이용하면 과도한 사인오프 오류를 예방할 수 있다.

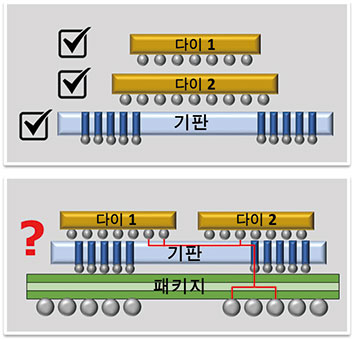

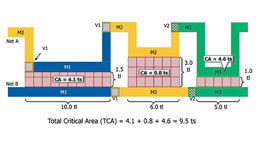

[그림 2] 각 다이와 기판을 검증하는 것만으로는 충분하지 않다. 잘못 정렬된 장치로 인해 발생한 개방, 단락 또는 주변부 연결 문제를 찾아내려면 어셈블리 전체의 LVL/LVS만이 유일한 해법이다.

물리적 검증

IC 검증의 대표적인 특징은 한 가지 프레임워크 내에서 여러 가지 전문 EDA 툴을 사용함으로써 설계자가 매우 다양한 검증 프로세스를 수행할 수 있다는 점이었다. 이종 패키지 어셈블리 검증을 자동화할 때도 추구하는 목표는 같다. 이종 검증은 각각의 다이를 이미 대상 파운드리 규칙에 비교하여 검사했다는 것을 전제로 대폭 간소화된 프로세스이다. 이때 설계와 검증 환경 사이의 독립성을 유지하여 검증 결과의 진실성을 보장하는 것도 매우 중요하다.

검증에는 DRC가 포함되어 다이 구성요소(간격, 피처 크기 등) 간 상호작용을 검증하며 각 다이 내의 여러 레이어를 추출하여 그러한 상호작용을 직접 확인할 수도 있다. 물리적 검증에는 기판 사이의 정렬, 스케일링 또는 보상 요인을 검사하고 패드 중심점이나 중첩을 확인하기 위한 LVL(layout-versus-layout) 검사도 포함된다.

EDA 툴은 다이당 적층과 배치당 적층의 차이를 구분할 수 있어야 한다. Mentor의 Calibre™ 3DSTACK은 가상 모델(디지털 트윈) 데이터를 사용하여 올바른 어셈블리 표현형을 자동으로 추출해 DRC 및 LVL 검사를 실행함으로써 설계가 모든 물리적 요구사항에 부합하는지 확인한다.

연결 검사(LVS)

IC에서 LVS 검사를 실행하면 물리적 레이아웃 데이터에서 도출한 서로 연결된 형태와 핀 위치를 살펴보고 물리적 netlist를 만든다. 이것을 이상적인 회로도 netlist와 비교하여 연결성이 우수한지 검증하는 것이다. 연결 검사는 각 기판 레벨에서, 그리고 여러 기판에 걸쳐 수행한다. 아주 단순한 형태의 자동 패키지 LVS 플로우는 인터포저 및 패키지 GDSII가 다이 간(멀티 다이 시스템의 경우) 또는 다이-C4/BGA 범프(싱글 다이 및 멀티 다이 시스템 모두)를 설계자가 의도한 대로 올바로 연결하도록 보장해야 한다. [3]

이종 패키지 어셈블리의 경우, 이러한 연결 대상이 다이와 인터포저일 수도 있고 다이, 인터포저와 패키지이거나 다이, 인터포저, 패키지와 PCB일 수도 있다. 어떤 구성이든 모두 시스템 netlist를 만들어 관리하는 기능부터 시작한다. 시스템 netlist는 앞서 언급한 것과 같이 전체 어셈블리의 가상 모델(디지털 트윈)로부터 컴파일된다.

이 시스템 netlist 또는 이상적인 netlist를 Calibre 3DST-ACK에서 GDS와 같은 제조 데이터에서 도출한 물리적 설계 연결에 비교하는 것이다. 경고나 위반 사항은 가상 모델에서 강조 표시되며, 여기에서 Xpedition Substrate Integrator 기능을 사용하면 오류를 추적하여 디버깅할 수 있다.

이종 어셈블리 레벨 검증

2.5 및 3D 이종 패키지에는 일반적으로 시스템 스케일링과 성능에 필요한 솔루션을 제공하기 위해 여러 개의 장치와 여러 개의 기판이 포함되어 있다. 다이와 기판 간의 구별이 줄어들면서 이러한 요소들이 서로 가까이 붙어 있다는 사실 때문에 칩-패키지 상호작용이 크게 강화되고, 따라서 하나로 통일된 통합 설계 플로우가 필요해진다. 고속 인터페이스나 전력 제공과 같은 중요한 요소의 경우, 기판 하나에 대하여 내린 결정이 인접한 기판이나 시스템 전체에 영향을 미치는 파급 효과를 가져올 수 있다.

설계자는 하나의 환경에서 여러 개의 기판을 관리할 방법을 찾아내야 한다. 이를 위해 여러 설계자가 지리적 위치나 부서를 걸쳐 공동 작업을 해야 하는 경우가 많으며, 이때 기판의 배선성, 전기 및 열 성능과 테스트 등을 평가하기 위해 쾌속 프로토타이핑과 통합 설계 등의 방식을 활용한다. 적절한 균형 지점과 최적의 솔루션을 찾아내려면 반복 작업을 계속 되풀이해야 할 수 있다.

이종 어셈블리의 물리적인 검증은 매우 광범위하게 논의된 사안이며, 자동 솔루션도 도입되었다. [1, 2] 그간 어셈블리 레벨 LVS 검증 요구사항에 대한 분석도 나왔다. 어셈블리 레벨 LVS 프로세스에 적합한 모범 사례를 알아보고 필수적인 입력 요소(데이터, 형식 등)와 발생 가능한 장애물도 제기되었다. 심지어 이러한 어셈블리에서 기생을 추출하는 방법에 관한 논의도 진행되었다. [3, 4]

방법론과 플로우가 발달하면서 시스템 레벨 설계자는 패키지 DRC, LVL 검증(다이-패키지 정렬, 스케일링, 방향 등)과 어셈블리 레벨 LVS만으로 이종 어셈블리의 올바른 기능성과 제조 성공을 보장할 수 있는지 알아야 한다.

아직 다뤄지지 않은 문제는 설계자가 이러한 모든 프로세스를 효율적이고 반복 가능하며 자동화된 플로우에서 관리할 수 있도록 하는 하나의 환경이 필요하다는 것이다. 이종 설계 및 검증에서는 설계자가 하나의 환경에서 여러 개의 기판(설계 데이터베이스)을 조정하고 관리할 수 있어야 한다. 하나의 환경에서 전체적인 그림(다이, 인터포저, 패키지, PCB)을 모두 파악할 수 있으면 설계자가 발생 가능한 다운스트림 문제를 예측하고 제거하기 쉬워지며 트레이드오프와 설계 가상 시나리오를 효과적으로 수행하여 평가할 수 있고, 결정한 사항을 이해관계자에게 명확하게 전달할 수도 있다.

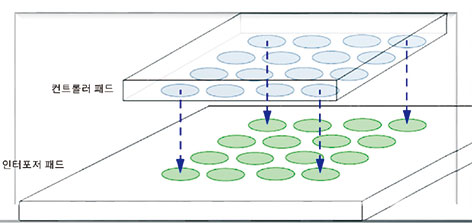

[그림 3] 정렬, 스케일링 및 변환 중첩

테스트

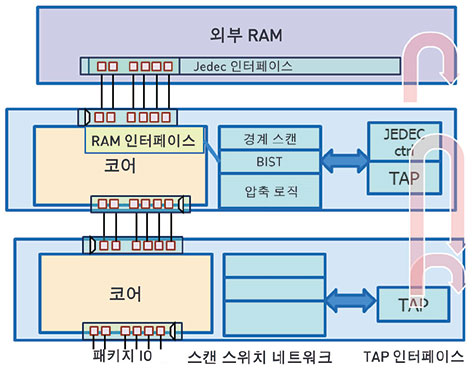

알려진 우수한 다이(KGD)는 2D 및 3D 이종 어셈블리에서 적층에 앞서 효과적인 테스트를 성공시키는 데 핵심적인 의미를 지닌다. 패키지 레벨 테스트 생성도 중요하다. 테스트 팀에서는 다이 레벨, 내장 자체 테스트(BIST) 및 스캔 패턴을 패키지 레벨로 매핑하여 다시 사용하는 것이 좋다. 패키지 상호연결 구조의 경계 스캔 테스트를 실시하면 IO가 실제로 연결되어 있는지 확인할 수 있고 기판 제조 또는 조립 문제가 있는지 알아볼 수도 있다. 부분적 스택 테스트의 경우 새 프로세스 또는 수율이 불량한 것으로 알려지거나 그럴 것으로 예상되는 프로세스를 대상으로만 실시한다.

다만 수준 높은 웨이퍼 테스트와 KGD를 거친다 해도 어셈블리에는 정전기 방전 손상 또는 웨이퍼 테스트 중에 누락된 핀으로 인해 결함이 발생할 수 있다. 멀티 다이 패키징의 경우, 조립을 마친 부품의 목표 수율을 그대로 유지하고자 한다면 웨이퍼 테스트의 수준과 깊이가 매우 중요하다.

Mentor의 Tessent™ 로직 테스트 툴을 사용하면 이종 패키지 테스트에 다양한 ‘모범 사례’ 테스트 기능을 이용할 수 있다. 예를 들면 다음과 같다.

• 다이 레벨 테스트 패턴 재사용

• 모든 기판 레벨에 대하여 공용 테스트 액세스 포트(TAP) 인터페이스 사용

• IJTAG를 사용해 테스트 패턴의 모드를 제어하여 유연성 지원

• 다이 레벨 테스트 패턴을 패키지 기판의 다른 레벨로 다시 매핑

[그림 4] 효율적이고 효과적인 테스트에서는 JTAG, TAP, 스캔 테스트 및 다이 간 상호 연결에 대한 IJTAG를 사용한다.

결론

지금까지 본 것과 같이, 오늘날의 신호 속도와 데이터 속도에 전력 사용량을 줄이고 발열량을 낮추려면 메모리를 SoC/ASIC와 같은 패키지에 함께 배치해야 한다. 여러 개의 장치를 한 개의 패키지에 통합하면 시스템 스케일링 수요를 지원하고 시스템 규모를 줄이며 제조 원가를 낮추는 동시에 품질과 신뢰성이 강화되는 경우가 많다.

이와 같은 차세대 패키징 솔루션은 물리적, 전기, 열 및 제조 성능을 판단하기 위한 검증된 자동 사인오프를 하나의 환경에서 해결하여 설계자가 이 모든 프로세스를 효율적이고 반복 가능하며 자동화된 플로우에서 관리할 수 있도록 해야 한다.

참고 문헌

[1] Tarek Ramadan, “Crossing the chasm: Bringing SoC and package verification together with Calibre 3DSTACK,” Mentor, a Siemens business. January 2017. https://go.mentor.com/4QLSO

[2] Dusan Petranovic and Karen Chow, “3D-IC system verification methodology: solutions and challenges.” Electronic Design Process Symposium, April 2011. https://www.researchgate.net/publication/268208901_3D-IC_System_Verification_Methodology_Solutions_and_Challenges

[3] Tarek Ramadan, “Package designers need assembly-level LVS for HDAP verification,” Mentor, a Siemensbusiness. December 2017. https://go.mentor.com/4WDVj

[4] Christian Decoin and Vassilis Kourkoulos, “Fast and accurate extraction of 3D-IC layout structures,” Mentor, a Siemens business. July 2012.

[5] Tony Mastroianni, “eSilicon tackles the challenges of advanced IC package design using Xpedition Substrate Integrator and Calibre 3DSTACK” May 2019. https://go.mentor.com/58xrP

[6] Amkor Delivers Industry’s First Package Assembly Design Kit to Support Mentor’s High-Density Advanced Packaging Tools July 2018. https://ir.amkor.com/news-releases/news-release-details/amkor-delivers-industrys-first-package-assembly-design-kit

아날로그 설계를 위한 EDA 툴은 어떻게 진화하고 있는가?

조회수 816회 / Siemens EDA

전자제품 인터페이스의 설계 라이프사이클

조회수 598회 / David Wiens

전기 디자인 룰 체크(DRC)를 자동화하는 방법

조회수 1259회 /

지멘스EDA 수석부사장.jpg)

2022년 시스템 및 설계 툴, 방법론의 시장 전망

조회수 1248회 / 지멘스

임계 영역을 이용한 자동차 IC의 테스트 품질 향상

조회수 1682회 / RON PRESS

SERDES 디자인을 위한 더 효율적인 솔루션이 있을까요?

조회수 1755회 / Neil Fernandes

지멘스 EDA 포럼 2021 열려, ‘Silicon to Systems’ 주제로 최신 설계 방...

조회수 1150회 / Joseph Sawicki

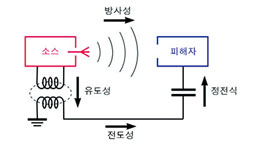

자동화된 EMC 분석을 PCB 레이아웃에 추가

조회수 1231회 / SIEMENS

DFT를 향한 성능 저하 없는 상향식 접근방식

조회수 2553회 / Geir Eide

PDF 다운로드

회원 정보 수정