자일링스의 단일 FPGA로 수백 개의 신호를 디지털화하는 방법

글/윌리엄 리차드(William D. Richard) 워싱턴대학 부교수, 미첼 마나(Mitchell Manar), 제레미 탱(Jeremy Tang) 워싱턴대학 학생

최신 자일링스(XilinxⓇ) FPGA는 LVDS(Low-Voltage Differential Signaling) 입력을 이용해 단하나의 레지스터와 하나의 커패시터만 있으면 아날로그 입력 신호를 디지털화할 수 있다. 최신 자일링스 디바이스에는 수백 개의 LVDS 입력이 존재하기 때문에, 이론상 단일 FPGA로 수백 개의 아날로그 신호를 디지털화하는 것이 가능하다.

최근 우리 팀은 3.75MHz 중심 주파수와 5bit의 분해능으로 대역-제한 입력 신호를 디지털화할 수 있는 디자인 영역에 대한 연구를 진행했으며, 더불어 128-element 선형 초음파 어레이 변환기의 신호를 디지털화하기 위한 옵션에 대해서도 조사했다. 이 데모 프로젝트를 자세히 살펴보도록 하겠다.

2009년에 자일링스는 LogiCORETM 소프트 IP 코어를 발표했는데, 이는 외부의 비교기와 하나의 레지스터, 하나의 커패시터를 이용해 최고 1.205kHz 주파수로 입력을 디지털화할 수 있는 ADC(Analog-to-Digital Converter)를 구현할 수 있다.[1]

외부 비교기 대신 FPGA의 LVDS 입력과 함께 델타 변조기 ADC 아키텍처를 이용하면, 단 하나의 레지스터와 하나의 커패시터 만으로 훨씬 높은 주파수로 아날로그 입력 신호를 디지털화할 수 있다.

ADC 토폴로지 및 실험용 플랫폼

그림 1은 자일링스 FPGA 상의 LVDS 입력을 이용해 구현한 1-채널 델타 변조기 ADC[2] 블록 다이어그램을 나타낸 것이다. 여기에서 아날로그 입력은 비인버텅 LVDS_33 버퍼 입력을 드라이브하며, 입력 신호 범위는 기본적으로 0~3.3V이다. LVDS_33 버퍼의 출력은 입력 아날로그 신호 주파수 보다 훨씬 높은 클럭 주파수로 샘플링되며, LVCMOS33 출력 버퍼와 외부의 1차 RC 필터를 통해 인버팅 LVDS_33 버퍼 입력으로 피드백된다. 이 회로에서는 적절하게 선택된 클럭 주파수(F), 저항(R), 커패시턴스(C)로 정해진 피드백 신호가 입력 아날로그 신호를 추적하게 된다.

예를 들어 그림 2를 보면, F= 240MHz, R= 2K, C= 47pF인 경우 노랑색(채널 1)은 입력 신호, 파랑색(채널 2)은 피드백 신호를 보여준다. 입력 신호는 애질런트(Agilent) 33250A 펑션 제너레이터의 200MHz, 12bit, 임의 출력 함수 기능을 이용해 생성된 것이다. 텍트로닉스(Tektronix) DPO 3054 오실레이터를 이용해 계산된 입력 신호의 푸리에 변환(Fourier Transform)은 빨강색(채널 M)으로 나타나 있다. 이러한 주파수에서 오실로스코프 프로브의 입력 커패시턴스(그라운드 이슈 포함)는 오실로스코프 트레이스에서 보여진 피드백 신호의 무결성을 저하시켰지만, 그림 2는 회로의 동작을 볼 수 있다.

블랙맨-누탈(Blackman-Nuttall) 윈도우를 적용해 그림 2에 나타낸 대역-제한 입력 신호는 1-Vpp 3.75MHz 사인파로 정의했다. 이론적으로 윈도우상의 신호와 관련된 노이즈 플로어는 중심 주파수 관련 진폭보다 낮은 거의 100dB이지만, 200MHz 샘플 주파수, 12bit 분해능의 애질런트 33250A 펑션 제너레이터의 결과는 가장 이상적인 데모 신호를 나타냈다. 중심 주파수가 거의 3.75MHz에 이르는 대부분의 초음파 변환기로 생성된 출력신호는 변환기의 기계적 특성상 대역-제한 신호이기 때문에 이 방식에 사용하기에 이상적인 신호 소스다.

8개의 R/C 네트워크와 입력 커넥터를 갖춘 자체 제작한 소형의 PCB 상에 탑재된 자일링스의 스파르탄-6(SpartanⓇ-6) XC6SLX4 FPGA와 Digilent Cmod S6 개발 모듈[3]을 이용해 그림 2의 플롯을 얻었으며, 이 프로토타입 시스템은 최고 8개의 신호를 동시에 디지털화할 수 있다. 각 채널은 신호 생성기에서 동축 케이블로 적절하게 종단되도록 그라운드로 50ohms으로 병렬로 종단된다. 이러한 성능을 달성하기 위해 LVCMOS33 버퍼의 드라이브 강도는 24mA로, 슬루 레이트는 FAST로 설정했다는 것을 유의해야 하며, 이 VHDL 소스 예제는 그림 5에 정리했다.

또한 이 자체 제작한 프로토타입 보드는 분석을 위해 호스트 PC로 패킷화된 직렬 비트스트림을 전송하는데 사용한 FTDI FT2232H USB 2.0 Mini-Module[4]을 지원한다. 그림 3은 그림 2의 아날로그 신호를 공급할 때 프로토타입 보드에서 생성된 푸리에 변환 비트스트림의 강도를 보여주고 있다. 240MHz 저조파 샘플링 주파수 관련 피크와 입력 신호 관련 3.75MHz에서의 피크 또한 분명하게 확인할 수 있다...(중략)

알베오 U55C의 출시로 HPC 업계에 많은 가치 제공할 것

조회수 814회 / Nathan Chang

엣지 센서에서 CPU 가속기까지 ‘버설 AI 엣지 시리즈’

조회수 1020회 / Rehan Tahir

적응형 컴퓨팅, 포스트-무어의 법칙 시대에서 성장을 주도하다

조회수 1364회 / Victor Peng

데이터센터 혁신을 위한 장벽 없는 FPGA 솔루션

조회수 1005회 / Kartik Srinivasan 외 2인

자동차 시장의 혁신을 선도하는 자일링스의 DNA

조회수 741회 / Yousef Khalilollahi

CXL, CCIX 기반 PCIe 5와 SmartNIC은 어떻게 가속 솔루션을 혁신하고 있...

조회수 6822회 / Scott Schweitzer

대규모 5G 무선 구축을 위한 혁신적인 징크 RFSoC DFE

조회수 1499회 / Gilles Garcia

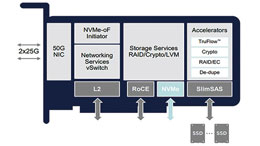

SmartNIC 아키텍처: 가속기로의 이행, 그리고 FPGA가 우위를 점하는 이유

조회수 4486회 / Scott Schweitzer

SmartNIC이 일반 NIC보다 뛰어난 이유는?

조회수 1874회 / Scott Schweitzer

PDF 다운로드

회원 정보 수정