SmartNIC 아키텍처: 가속기로의 이행, 그리고 FPGA가 우위를 점하는 이유

글/스캇 슈바이처(Scott Schweitzer)

일반적인 네트워크 인터페이스 카드(NIC)는 이더넷 컨트롤러로 설계된 단일 ASIC (Application Specific Integrated Circuit)을 기반으로 구현된다. 대표적인 예로는 멜라녹스(MellanoxⓇ)의 커넥트X(ConnectXⓇ) 라인과 브로드컴(BroadcomⓇ)의 넥스트림(NetXtremeⓇ), 또는 자일링스(XilinxⓇ)의 익스트림스케일(XtremeScale™) 등을 들 수 있다. 이러한 칩은 종종 두 번째 설계에서 더욱 최적화되는데, 예를 들어, 커넥트X 라인은 인피니밴드(Infiniband)를 지원하고 있으며, 익스트림스케일은 커널 바이패스에 중점을 두고 있다. 이러한 컨트롤러는 수행능력이 탁월하고, 업계에서 가장 우수한 것으로 꼽히고 있지만, 엄밀히 말해서 SmartNIC은 아니다. 이 글에서는 NIC을 구입한 후 새로운 기능을 추가하거나 다른 기능을 지원하기 위해 일부 지점에 추가 소프트웨어를 로드할 수 있는 NIC을 SmartNIC으로 정의하고 있다. 이는 스마트폰을 구입한 후 해당 공급업체의 앱스토어를 통해 앱을 설치하는 것과 매우 유사하다.

NIC에 추후 코드를 로드할 수 있는 기능이 있어야만, SmartNIC이 된다. 이는 일반 NIC에서는 찾을 수 없는 추가 컴퓨팅 성능과 온보드 메모리가 요구된다. 대부분의 SmartNIC 접근방식은 실리콘 칩이나 펌웨어 또는 어댑터 상의 별도 칩을 이용해 기본 이더넷 컨트롤러를 구현하는 방식으로 시작된다. 그런 다음 아래의 세 가지 접근방식 중 하나를 사용하여 컴퓨팅 성능을 높임으로써 일반적인 NIC을 스마트하게 만든다.

• 다수의 Arm 코어 병합. 일부는 이를 클러스터 기법이라고도 하고, 다른 사람들은 그리드 또는 타일이라는 용어를 사용한다.

• 맞춤 설계된 네트워크 프로세서인 FPC(Flow Processing Core). 주로 P4

• 프로그래머블 로직인 FPGA(Field Programmable Gate Array)

이러한 SmartNIC의 대부분은 NIC 내의 컨트롤 플레인 관리를 위해 하나 이상의 Arm 코어를 사용하는 경우가 많다. 일부는 수정된 리눅스 커널을 이러한 코어 중 하나에 로드할 수도 있다. Arm 코어는 일반적으로 SmartNIC의 상태 및 구성을 감시하고, 다른 프로세싱 요소에 코드를 로드하고, 통계 및 로그를 수집하는데 사용된다. 네트워크 패킷을 전혀 건드리지 않고, 종종 대역외(Out-of-Band)로 실행되기 때문에 ‘일반(Normal)’ 네트워크 인터페이스나 PCIe 명령을 통해 액세스할 수 없다. 또한 이전의 안전한 보안 인터페이스를 통해 정식 서명된 펌웨어 번들만 허용된다. 이러한 컨트롤 제어 플레인 Arm 코어는 별도의 연결작업이 필요한 요소이기 때문에 아키텍처 차원에서만 언급할 것이다. 일반적으로 Arm 코어 자체가 SmartNIC이 제공하는 기능 세트의 가치를 향상시키는 것은 아니다.

SmartNIC이 일반 NIC과 어떻게 다른지 이해하기 위해 전세계에서 가장 큰 4개의 NIC 회사의 선도적인 SmartNIC 제품을 자세히 알아보고, 두 개의 신생기업이 개선한 사항에 대해서도 살펴보고자 한다. 선정된 6개 기업은 브로드컴, 인텔, 엔비디아(Nvidia, 이전의 멜라녹스), 네트로놈(Netronome), 펜산도(Pensando), 자일링스 등이다. 또한 스텔스 프로젝트인 펀저블(Fungible)에 대해서도 간단히 살펴볼 것이다.

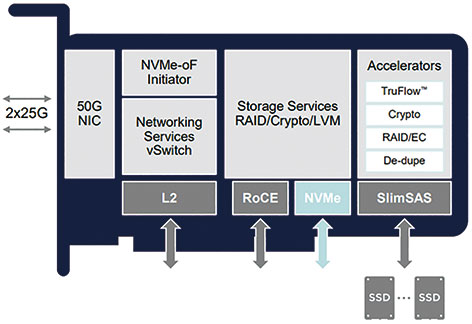

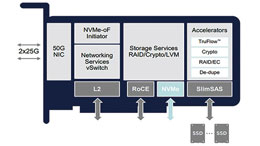

브로드컴은 상용 이더넷 NIC 컨트롤러 시장의 대표적인 선두주자이다. 브로드컴은 스팅레이(Stingray) SmartNIC을 조립하고, 시장에 진입하면서 단일 칩 접근방식을 사용했다. 단일 칩 SmartNIC 솔루션은 보드 상에 많은 칩을 사용하는 다른 경쟁사에 비해 보드 레벨의 생산 비용을 항시 절감할 수 있다. 브로드컴은 넥스트림 E 시리즈 컨트롤러의 로직을 기반으로 스팅레이의 핵심 칩인 넥스트림-S BCM58800을 설계했다. 그런 다음 클러스터 구성으로 3GHz 클럭 속도를 제공하는 8개의 Arm v8 A72 코어를 배치했다. 3GHz는 아마도 가장 빠른 SmartNIC Arm 코어일 것이다. 또한 스팅레이는 최대 16GB의 DDR4 메모리 구성도 지원한다. 다음으로 브로드컴은 최대 90Gbps로 암호화를 오프로드하고, 이레이저 코딩(Erasure Coding) 및 RAID와 같은 스토리지 프로세싱을 오프로드하기 위해 일부 로직을 혼합했다. 마지막으로 브로드컴은 트루플로우(TruFlowⓇ) 기술을 추가했는데, 이는 완전히 공개되지 않았다. 이는 일반적인 네트워크 플로우 프로세스를 하드웨어로 이동시키기 위한 플로우 가속기인데, P4 프로세서를 사용할 것으로 판단하고 있다. 이를 통해 Arm 코어가 플로우 및 패킷 레벨에서 컴퓨팅 집약적 작업에 집중할 수 있도록 해준다. 공개된 자료를 보면, 트루플로우는 하드웨어에서 OvS(Open vSwitch)와 같은 작업을 오프로드하는 것으로 알려져 있다. 브로드컴은 트루플로우가 하드웨어의 분류 및 매칭, 실행동작과 같은 전통적인 여러 SDN(Software Defined Networking) 개념을 구현한다고 주장한다. 스팅레이는 2개의 프로그램이 가능한 컴포넌트와 트루플로우, 그리고 4개의 3GHz 듀얼 코어 Arm v8 A72 복합 클러스터로 구성되어 있다. 브로드컴은 올해 여름, 스팅레이를 7nm 공정으로 전환하여 8개의 코어에서 12개의 코어로 확장할 수 있도록 준비하고 있다고 밝혔다. 또한 브로드컴은 자신들이 제공하는 제품의 복잡성을 고려하여 SmartNIC 애플리케이션 및 스토리지 컨트롤러 개발을 위한 스팅레이 개발 키트도 제공하고 있다. 이러한 키트를 제공하는 것이 일반적이지는 않지만, 이는 완벽한 SmartNIC 제품 공급을 위한 필수적인 구성요소이다.

[그림 1] 브로드컴이 2019년 SDC에서 발표한 브로드컴 스팅레이(Stingray) 아키텍처

GPU(Graphical Processing Unit)의 정의를 수립한 엔비디아는 이제 고성능 컴퓨팅(HPC: High-Performance Computing)에서 가장 널리 사용되는 가속기가 되었다. 올해 초 엔비디아는 70억 달러에 멜라녹스 인수를 완료했다. 엔비디아는 HPC 시장을 더욱 확장하기 위해 HPC 고객들에게 완벽한 솔루션을 제공할 수 있는 최고의 인피니밴드 인터커넥트 업체를 선택했다. 이는 과거에 크레이(Cray)가 시도했던 방식과 유사하다. 또한 엔비디아는 오픈소스 이더넷 스위치 OS 분야의 리더인 큐물러스 네트웍스(Cumulus Networks)를 최근 인수했다. 소프트웨어는 항상 멜라녹스의 약점으로 지적되어 왔는데, 엔비디아가 이를 조기에 인식하고 대응한 것이다. SmartNIC과 관련하여, 엔비디아는 멜라녹스 인수를 통해 흥미로운 이스터 에그(Easter Egg)까지 얻게 되었다.

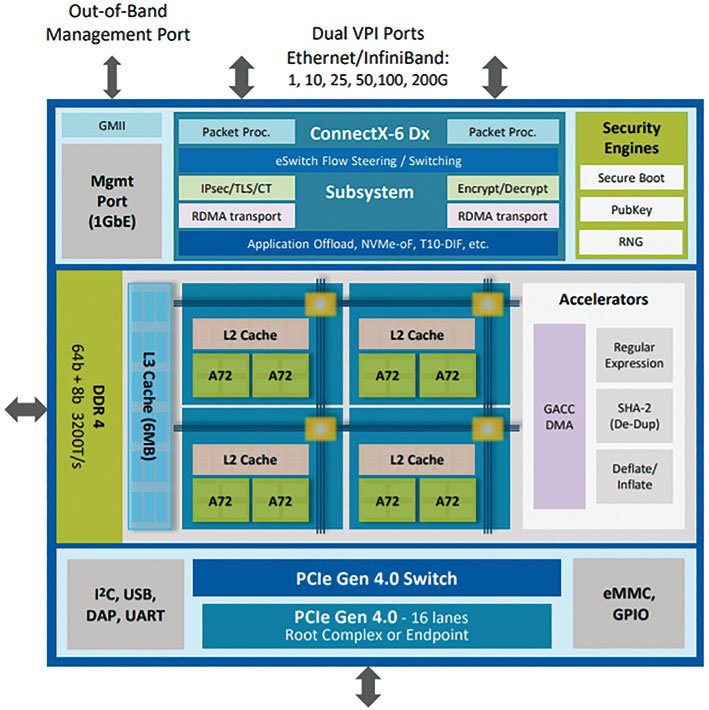

멜라녹스는 SmartNIC 분야에서 가장 오래된 기업 중 하나이지만, 이는 인수를 통해 이뤄졌다. 현재의 블루필드 2(Bluefield 2) 솔루션은 2015년 이지칩(EZchip)을 인수를 통해 흡수된 틸레라(Tilera) 기술을 기반으로 구현되었다. 틸레라는 최초로 고도의 병렬 SmartNIC을 구현한 업체 중 하나로, 오래 전 MIT 연구 프로젝트에서 발전한 IP(Intellectual Property)를 사용했다. 기본적으로 틸레라는 프로세싱 코어를 칩 상에 타일 형태로 배열하고, 각 코어는 주변의 4개 코어에 대한 고속 버스를 가지고 있다. 2013년의 주력 제품은 최대 72개의 MIPS 코어와 메모리 컨트롤러, 암호화 모듈 및 PCIe 블록과 SFP+ 커넥터가 있는 여러 MAC용 채널 모음인 mPipe를 지원했다. 멜라녹스는 코어를 Arm으로 교체하고, 커넥트X 로직용으로 mPipe를 교체하면서 이를 개선했다. 현재 코어 수는 브로드컴과 마찬가지로 8개의 Arm v8 A72이지만, 클럭 속도는 2.4GHz이다. 이는 클러스터 방식으로 4개의 듀얼 코어 Arm을 배열했다. 블루필드는 현재 아바고(Avago)의 16nm 공정을 사용하고 있지만, 브로드컴과 마찬가지로 올 여름에 7nm로 전환하여 8개의 코어에서 12개의 코어로 확장할 예정이라고 밝혔다. 이러한 접근방식은 브로드컴의 스팅레이와 매우 유사하지만, 브로드컴 아키텍처의 핵심인 병렬 P4 프로세서는 없다. P4는 모두가 지향하고 있지만, 언급만 있을 뿐 아직 갖춰진 것은 아니다. 브로드컴과 자일링스, 펜산도 모두 공개적으로 P4에 주력하고 있다고 밝히고 있다. 반면 큐물러스 네트웍스는 P4 프로그래밍에 대한 경험이 있다. 따라서 엔비디아가 미래의 블루필드 제품을 선도하기 위해 P4 패킷 프로세싱 엔진을 만드는 것은 놀라운 일이 아니다.

[그림 2] 제품 데이터시트에 나와 있는 멜라녹스의 블루필드 2(Bluefield 2) 아키텍처

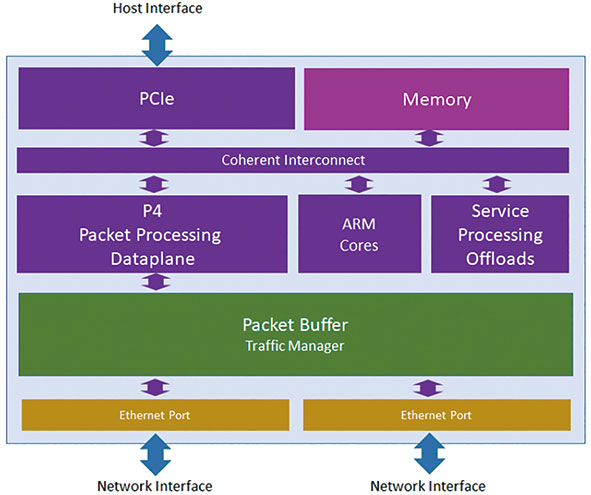

가장 최근의 SmartNIC 스타트업인 펜산도는 시스코(Cisco)의 전임 CEO인 존 챔버스(John Chambers)가 설립한 회사다. 존은 이전 시스코 직원 6명으로 드림팀을 구성하고, 새로운 벤처회사에 도전했다. 이들은 모두 과거에 자신의 회사가 시스코에 인수된 경험을 가지고 있는 사람들이다. 따라서 이들에 대한 평가와 이전의 경험을 감안할 때, 펜산도가 일부 주요 고객들을 통해 자사의 기술을 입증한 다음, 이를 패키지로 만들어 시스코와 합병을 추진할 것이라는 의견이 설득력을 얻고 있다. 시스코는 몇 가지 일반적인 NIC 기술을 보유하고 있고, 여러 내부 SmartNIC 프로젝트를 추진하고 있지만, 시장에서는 아직 빛을 보지 못하고 있기 때문에 펜산도가 분명히 이 공백을 채우는데 주력할 것으로 예상된다. 펜산도는 원래 두 가지 제품을 가지고 있었지만, 최근에는 시스코 제품명과 유사한 분산형 서비스 카드인 DSC-25 단일 제품으로 재정립했다. 이 제품은 단일 P4 프로세서 칩과 일부 보조 프로세싱을 위한 Arm을 갖추고 있으며, 데이터시트에 따르면 두 칩 모두 최대 4GB의 온보드 메모리를 지원하는 것으로 보인다. 이 프로세서는 카프리(Capri)라고 불리며, 여러 병렬 스테이지가 있는 P4 프로그래머블 유닛이다. 그러나 패킷 성능 및 지연시간, 지터 등이 공개되지 않았기 때문에 정확한 병렬 프로세싱 성능 수준은 알 수 없다. 펜산도는 P4 애플리케이션을 유지하기 위해 카프리 캐시를 내부에 남겨두고 있는데, 명령어를 위한 메모리 패치로 인해 캐시 미스(Cache Miss)가 발생하면 모든 지표에서 성능이 저하된다. 서비스 프로세싱 오프로드(Service Processing Offload)라고 하는 다른 추가 컴퓨팅 장치가 암호화, 스토리지 프로세싱 및 기타 작업을 처리한다. 펜산도는 카프리가 유선 속도의 성능을 제공할 수 있다고 주장하고 있다.

[그림 3] P4.org 블로그에 포스팅(2020년 2월 24일)된 펜산도의 DPU 아키텍처

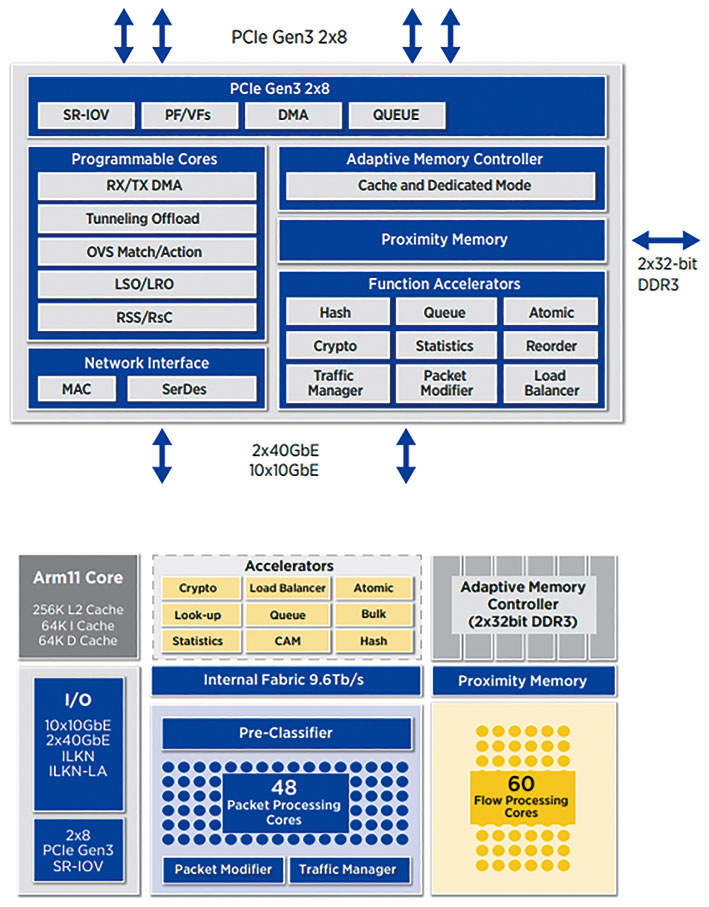

네트로놈은 2003년에 이 분야에 진입한 상당히 오래된 스타트업으로 지금까지 5번에 걸쳐 총 7,300만 달러의 투자금을 유치했다. 이 회사는 P4 기술을 활용한 첫 번째 SmartNIC 데모를 선보인 지난 2015년부터 적극적으로 P4를 추진해 왔다. 이후 상당한 진전을 이뤘지만, 최근에는 이 회사가 어려움을 겪으면서 시장을 떠날 것이라는 소문이 일고 있다. 그림 4는 현재의 NFP4000 플로우 프로세서(Flow Processor)에 대한 아키텍처이다. 네트로놈은 단일 P4 프로세싱 엔진 대신 두 가지 클래스의 프로그래머블 로직과 48개의 패킷 프로세싱 코어 및 60개의 플로우 프로세싱 코어를 활용하고 있다. 또한 분류 및 수정, 관리를 위한 전용 실리콘이 추가로 제공된다. 이러한 모든 코어는 P4에서 프로그램이 가능하다. 이를 통해 네트로놈은 초당 1억 4,800만 개의 패킷을 처리할 수 있는 유선 속도급의 단일 100Gbps 링크를 유지할 수 있고, 수백만 개의 매칭 정확도와 와일드 카드(Wild Card) 플로우를 지원한다고 밝혔다. 또한 캡슐화가 필요한 10만개 이상의 터널 연결을 지원할 수 있다. 네트로놈은 자사 기술이 지원할 수 있는 주요 애플리케이션 분야로 IDS(Intrusion Detection System), IPS(Intrusion Prevention System), NGFW(Next Generation Firewall), 라우터, 로드밸런서(Load Balancer), 패킷 브로커(Packet Broker), SDN, NFV를 비롯해 다른 애플리케이션에 대한 전반적인 호스트 기능 등 방대한 목록을 언급하고 있다.

[그림 4] 네트로놈 NFP4000 제품 개요에 소개된 NFP4000 플로우 프로세서 아키텍처

펀저블은 P4 분야에서 아직 두각을 드러내고 있지는 않지만, 잠재력이 매우 높은 것으로 평가되고 있다. 이들은 지난해 C라운드의 소프트뱅크 비전(Softbank Vision)에서 유치한 2억 달러를 포함해 총 3번에 걸쳐 약 3억 달러에 달하는 투자금을 조달했으며, 곧 제품을 발표할 예정이다. 현재는 180여명의 직원을 제외하고, 제품도 없고, 매출도 없으며, 실질적인 고객도 없다. 펀저블은 DPU(Data Processing Unit)를 만들고 있다고 주장하지만, 실제 아키텍처와 구성은 불분명하다. 그들은 그림 5의 다이어그램을 공개했는데, 이는 아키텍처 다이어그램이라고 하기에는 무의미할 만큼 모호하다. 여러 기사에서 펀저블의 제품이 올 여름 출시될 것이라는 언급이 있었는데, 현재로서는 실제로 확인할 수 없었다. 수석 설계자겸 창립멤버 중 한 사람은 스토리지 중심 이더넷 NIC 전문기업인 첼시오 커뮤니케이션즈(Chelsio Communications)에서 10년 동안 근무한 전문가이며, 소프트웨어 및 펌웨어 엔지니어링 부사장 또한 첼시오 출신이다. 과거에 첼시오는 13년 동안 ASIC을 주도했지만, 요즘에는 최첨단 SmartNIC 이더넷 컨트롤러 ASIC을 처음부터 만들기 위해서는 5천만 달러 이상의 귀중한 자금이 쉽게 소비될 수 있다. 따라서 업계에서는 펀저블이 플랫폼의 비밀 소스인 ASIC 설계를 기반으로 초기 제품에는 FPGA 플랫폼을 활용함으로써 수익을 달성할 때까지 가장 손쉬운 방법을 선택할 것으로 추측하고 있다. 하지만 이들이 고객과 수익을 따라가는 동안 디자인이 달라질 수도 있다. FPGA에 설계를 로드하면, 펀저블은 쉽게 설계 결함을 수정하고, 신속하게 고객 중심의 기능 개선을 지원할 수 있다. 오늘날의 FPGA는 엄청난 규모를 자랑하고 있으며, RISC-V와 같은 완전한 형태의 프로세서 아키텍처가 이러한 플랫폼에 로드되기 시작했다.

[그림 5] BlocksAndFiles.com 블로그에 포스팅(2020년 2월 11일)된 펀저블의 하이레벨 아키텍처

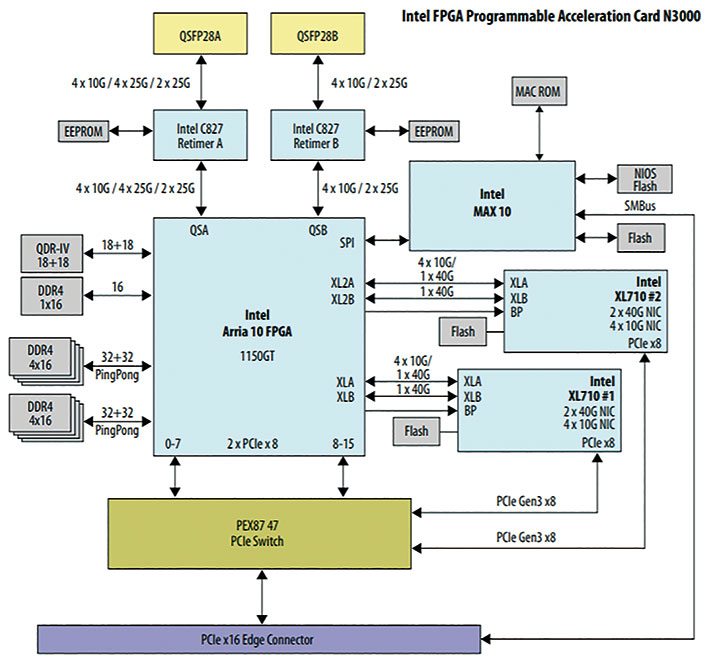

칩 회사 중 인텔 보다 큰 회사는 없을 것이다. 인텔은 10년 넘게 고성능 10GbE 이더넷 컨트롤러 라인을 지속적으로 유지해 왔다. XL710 플랫폼은 수백만 개의 유닛이 출하되었으며, 많은 데이터센터 서버의 주요 요소가 되었다. 새로운 N3000 SmartNIC의 경우, 인텔은 5개의 칩을 사용해 보드를 구현했다. 대부분의 공급업체들이 단일 칩 설계에 주력하고 있는 것과 비교하면, 이는 비용이 많이 드는 접근방식이다. 인텔은 한 쌍의 XL710 이더넷 컨트롤러와 아리아 10(Arria 10) FPGA를 통합하고, 48 레인 PEX8747 PCIe Gen 3 스위치 칩을 사용했다. 8개의 레인은 각 XL710을 지원하고, 16개의 레인은 아리아, 다른 16개의 레인은 PCIe 소켓과 연결된다. 다른 SmartNIC에서 컨트롤 플레인 관리를 처리하기 위해 Arm 코어가 사용되는 것처럼, 다섯 번째 칩은 FPGA를 관리하는 맥스 10(MAX 10Ⓡ) FPGA BMC(Baseboard Management Controller)이다. 이 보드는 FPGA와 바로 연결되는 듀얼 QSFP28 포트를 가지고 있다. 그런 다음, 10G 중 8개 레인은 이 FPGA에서 각 XL710으로 나간다. 이는 전통적인 유선 접근방식 중 하나로, XL710으로 전달되기 전에 FPGA가 패킷을 처리할 수 있다.

[그림 6] 제품 데이터시트에 게시된 인텔의 N3000 SmartNIC 아키텍처

상용 이더넷 컨트롤러와 FPGA를 사용하여 NIC을 구현하는 것은 새로운 방식이 아니다. 2012년에 솔라플레어 커뮤니케이션즈(Solarflare Communications)는 NIC 상의 두 개의 QSFP 포트와 이더넷 컨트롤러 사이에 FPGA를 배치한 AOE(Application Onload Engine) 플랫폼을 개발했다. 이는 인텔이 선택한 N3000 디자인의 원조에 해당한다. 당시 솔라플레어는 금융권 고객들에게 350ns의 인상적인 틱투트레이드(Tick-to-Trade) 결과를 제공했다. 약 8년이 지난 지금, 이 기록은 24.2ns에 이르고 있다. 인텔의 접근방식은 FPGA가 XL710 이전에 패킷 프로세싱을 수행하는 것이다. 인텔 FPGA는 115만개의 프로그래머블 LE(Logic Element)와 각각 4GB의 DDR4 메모리 뱅크 2개를 갖추고 있어 다음과 같은 SmartNIC 작업을 처리할 수 있는 충분한 성능을 제공한다.

• 가상 광대역 네트워크 게이트웨이(vBNG: Virtual Broadband Network Gateway)

• 계층적 서비스 품질(HQoS: Hierarchical Quality of Service)

• 패킷 분류 및 폴리싱(Policing), 스케쥴링, 쉐이핑(Shaping)

• vEPC(Virtualized Evolved Packet Core)

• 5G 차세대 코어 네트워크(NGCN: Next-Generation Core Network)

• 인터넷 프로토콜 보안(IPSec: Internet Protocol Security)

• IPv6를 위한 세그먼트 라우팅(SRv6: Segment routing for IPv6)

• 벡터 패킷 프로세싱(VPP: Vector Packet Processing)

• 가상 무선 액세스 네트워크(vRAN: Virtual Radio Access Network)

인텔은 N3000 플랫폼에 대해 위에서 언급한 작업부하를 목표로 삼았지만, 이 SmartNIC에서 이러한 각 애플리케이션을 오프로드하기 위해 필요한 모든 소프트웨어를 제공했는지 여부는 현재로서 확실하지 않다. SmartNIC 소비자는 소프트웨어에 악마가 있다는 것을 알게 될 것이며, 이러한 모든 회사들의 하드웨어는 탁월하지만, 소프트웨어 배포는 완전히 다른 분야이다.

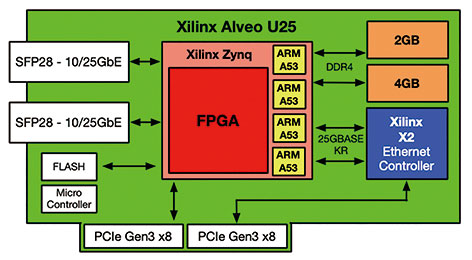

SmartNIC 분야의 또 다른 주목할만한 FPGA 업체는 1980년대 중반 FPGA를 최초로 상용화한 자일링스이다. 오늘날 자일링스는 FPGA 시장의 1위 기업이며, 인텔은 상당한 격차를 두고 2위를 기록하고 있다. 자일링스는 2019년 가을, 솔라플레어 커뮤니케이션즈를 인수했으며, 솔라플레어는 2012년부터 전자거래를 위한 ASIC 및 FPGA 기반 NIC을 구현해 왔다. 영국 캠브리지 출신의 솔라플레어 엔지니어링 팀은 그림 7에 나타낸 자일링스 알베오(Alveo) U25 SmartNIC 개발에 기여했다. 따라서 이 시장에서 거의 10년의 경험을 갖춘 팀의 노하우가 활용된 것이다. 알베오 U25는 듀얼 SFP28 포트를 징크(ZynqⓇ) 시리즈 칩과 직접 연결했다. 징크는 FPGA뿐만 아니라 패킷 프로세싱을 위한 쿼드 코어 Arm A53을 갖추고 있기 때문에 실제로는 SoC(System on Chip)이다. 또한 징크는 8레인 PCIe Gen 3를 통해 호스트 서버와 직접 연결되며, X2 이더넷 컨트롤러 칩과는 SerDes를 통해 연결된다. 또한 8레인 PCIe Gen 3를 통해 호스트와도 연결된다. 이러한 접근방식을 통해 징크는 패킷이 X2 칩으로 전달되기 전에 처리하거나 X2를 완전히 바이패스 시킨다. 또한 알베오 U25는 이 칩에서 실행되는 프로그램으로 징크 FPGA 및 Arm 코어에 액세스할 수 있도록 6GB의 DDR4 메모리를 포함하고 있다. 이 FPGA는 인텔이 제공하는 LE 수의 절반 수준인 52만 개를 지원하지만, 내장된 쿼드 코어 Arm은 줄어든 게이트 수 이상의 역할을 제공한다. 자일링스는 당초 OvS(Open Virtual Switch) 오프로드 기능을 필요로 하는 고객들을 위해 알베오 U25를 출시했다. 자일링스는 조만간 IPSec, 머신러닝, DPI(Deep Packet Inspection), 비디오 트랜스코딩 및 분석을 위한 오프로드 기능도 추가할 것이라고 밝혔다. 자일링스는 SmartNIC 분야에서 매우 다양한 기능을 제공하는 기업 중 하나일 것이다. 자일링스는 2년 전 솔라플레어 인수를 앞두고, 당시 파트너였던 솔라플레어와 함께 OCP 서밋에서 훨씬 큰 규모의 FPGA 내부에서 SoftNIC을 실행하는 익스트림스케일 X2 컨트롤러 로직을 공개적으로 시연한 바 있다.

[그림 7] 자일링스가 제공한 자일링스의 알베오(Alveo) U25 아키텍처 다이어그램

인텔과 마찬가지로 자일링스는 킨텍스(KintexⓇ), 버텍스(VirtexⓇ), 징크, 버설(VersalⓇ) 등 수익성이 뛰어난 여러 컴퓨팅 칩 제품 라인을 보유하고 있다. 킨텍스와 버텍스는 순수 FPGA로, 이 라인의 일부 모델은 약 3백만개에 이르는 엄청난 로직 셀(Logic Cell)을 갖추고 있으며, 이는 인텔 N3000에 사용된 것보다 거의 3배에 가깝다. 또한 자일링스는 실리콘 인터포저(Silicon Interposer)를 이용한 놀라운 작업을 통해 버텍스 칩에 최대 16GB의 HBM(High Bandwidth Memory)을 적층했다. 이 기술은 4개의 모든 칩 라인의 다른 제품에도 적용되고 있다. 징크는 FPGA 프로그래머블 로직과 함께 쿼드 코어 Arm, 실시간 Arm 코어 및 DDR 컨트롤러와 이더넷 및 PCI Express를 위한 커넥티비티 로직을 모두 통합한 SoC 칩 라인이다. 버설은 SoC를 넘어 7nm 기술로 구현된 적응형 컴퓨팅 가속화 플랫폼(ACAP: Adaptive Compute Acceleration Platform)이다. ACAP은 수백 개의 AI(Artificial Intelligence) 코어와 DSP(Digital Signal Processing Engine) 등을 추가하여 징크 아키텍처를 확장한 것이다. AI 코어는 다소 새로운 것이지만, 본질적으로 단일 정밀도 컴퓨팅 엔진이다. 결과적으로 자일링스는 공개적으로 입증된 버설 기반의 SoftNIC과 함께 SmartNIC 플랫폼에서도 독보적인 입지를 점하게 될 것이다.

네트로놈과 현재 자일링스로 인수된 솔라플레어 커뮤니케이션즈를 통해 알 수 있듯이 SmartNIC은 상당히 오래 전부터 출시되어 왔다. 구글 및 아마존과 같은 잠재력이 큰 규모의 고객은 자체 솔루션을 설계하고, 구현함으로써 이 시장에서 벗어나 있지만, 페이스북과 마이크로소프트는 업계 공급업체들의 빠른 대응으로 높은 수준의 아키텍처를 갖추고 있다. 이 모든 상황들이 정리되는 동안, SoC, 그리고 더 중요한 FPGA는 이제 SmartNIC의 기반 기술로 자리매김 할 정도로 성장했다. 10년 전 처음 하드웨어 가속화 기술이 큰 파장을 불러일으켰을 때, GPU 제품이 주목을 끌었다. 이제 3백만 이상의 로직 유닛으로 확장할 수 있는 FPGA를 통해 네트워킹, 메모리, 스토리지 및 컴퓨팅을 위한 다른 구성 가능한 프로세싱 블록까지 긴밀히 결합할 수 있게 되었다. 이 경우 컴퓨팅은 SoC 블록 또는 ACAP을 통한 온칩 코어 클러스터가 될 것이다. 이러한 발전으로 우리는 제 2의 하드웨어 가속 시대가 다가오고 있음을 알 수 있다. GPU가 이러한 플랫폼을 지원하기 위해서는 새로운 프로그래밍 API와 툴이 필요하며, FPGA도 마찬가지다. 그러나 차이점은 FPGA 기술은 35년 이상 진화해 왔으며, 이제 그 시대가 도래하고 있다는 점이다. 마침내 SmartNIC 시장이 등장함에 따라 가속화 시장에서 일련의 중첩지점을 형성하는 FPGA 기반 하드웨어 가속기의 새로운 흐름이 확산됨에 따라 엄청난 변화를 촉진하는 것은 물론, 향후 컴퓨팅에 대한 우리의 관점도 달라질 것이다.

SmartNIC은 컴퓨팅을 촉진시키고 네트워크 엣지를 가속화함으로써 서버의 CPU가 비즈니스에 중요한 복잡한 프로세싱에 집중하여 더 많은 솔루션을 처리할 수 있도록 해준다. 연구에 따르면, 고도로 가상화된 환경의 네트워킹은 호스트 CPU 사이클의 30% 이상이 OvS 트랜잭션과 같은 프로세싱 작업을 처리하는데 소비되는 것으로 나타났다. SmartNIC에서 스토리지 기능과 암호화, DPI 및 정교한 라우팅이 수행될 수 있다고 상상해 보자. 이는 잠재적으로 이러한 작업부하를 처리하는데 소요되는 CPU 사이클의 상당 부분을 호스트 CPU 복합체가 활용할 수 있도록 되돌려 줄 수 있다. 대기업들과의 경쟁에 앞서기 위해 펜산도와 펀저블과 같은 신생 기업들은 SmartNIC 시장에 혁신적인 기능과 성능을 지속적으로 도입해 나갈 것이다. 동시에 자일링스, 인텔, 브로드컴, 엔비디아와 같은 선도 기술 기업들은 컴퓨팅 코어 기반 기술과 특수 P4 프로세싱 엔진을 발전시켜 나갈 것이다. 조만간 흥미로운 시대가 펼쳐질 것이다.

알베오 U55C의 출시로 HPC 업계에 많은 가치 제공할 것

조회수 814회 / Nathan Chang

엣지 센서에서 CPU 가속기까지 ‘버설 AI 엣지 시리즈’

조회수 1020회 / Rehan Tahir

적응형 컴퓨팅, 포스트-무어의 법칙 시대에서 성장을 주도하다

조회수 1363회 / Victor Peng

데이터센터 혁신을 위한 장벽 없는 FPGA 솔루션

조회수 1005회 / Kartik Srinivasan 외 2인

자동차 시장의 혁신을 선도하는 자일링스의 DNA

조회수 741회 / Yousef Khalilollahi

CXL, CCIX 기반 PCIe 5와 SmartNIC은 어떻게 가속 솔루션을 혁신하고 있...

조회수 6813회 / Scott Schweitzer

대규모 5G 무선 구축을 위한 혁신적인 징크 RFSoC DFE

조회수 1496회 / Gilles Garcia

SmartNIC 아키텍처: 가속기로의 이행, 그리고 FPGA가 우위를 점하는 이유

조회수 4476회 / Scott Schweitzer

SmartNIC이 일반 NIC보다 뛰어난 이유는?

조회수 1871회 / Scott Schweitzer

PDF 다운로드

회원 정보 수정