열 저항 RthJC의 측정 방법과 사용법

자료제공/로옴코리아

정션에서 케이스까지의 열 저항이란?

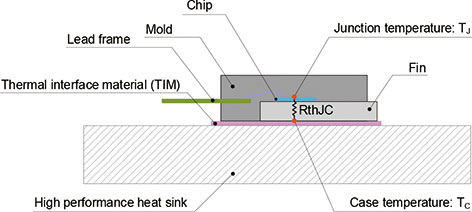

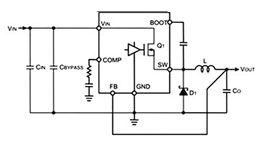

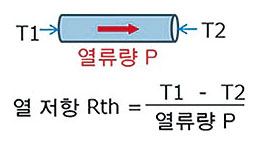

정션에서 케이스까지의 열 저항이란, JEDEC Standard JESD51에서는, 반도체 디바이스의 동작 부분에서 칩의 실장 영역에 가장 가까운 패키지(케이스)의 외주면(外周面)까지의 열 저항으로, 그 외주면이 적절하게 방열되고 있는 경우에 외주면과 히트싱크의 온도차가 최소한으로 억제된다고 정의하고 있다. 그림으로 나타내면 그림 1과 같다.

[그림 1] JESD51에서의 RthJC의 정의를 도표화한 예

이 규격에서는 반도체의 발열 정션에서 케이스 표면까지의 1차원 방열 경로를 지닌 반도체 디바이스의 정션에서 케이스까지의 열 저항을 재현할 수 있는 측정 방법과 규정을 명시하고 있다. 1차원이란, 열이 흐르는 방향이 선에 따르는 것을 의미한다. 그러나, 이러한 열이 흐르는 방향은 3차원으로 확산하는 능력을 지닌다.

정션에서 케이스까지의 열 저항은 반도체 디바이스의 중요한 열 특성의 하나이며, 이 면을 고성능 히트싱크에 접촉시킴으로써, 케이스 표면에서 가능한 최선의 냉각 조건에서의 열 성능 한계를 나타낸다. 이 값은 낮을수록 열 성능이 우수하다. 심볼은 RthJC 또는 Theta-JC이다. 그리스 문자를 사용하는 경우는 RθJC 또는 θJC이다. 로옴의 디스크리트 제품은 주로 RthJC와 RθJC를 사용하고 있다.

MIL-STD-883E의 테스트 방법

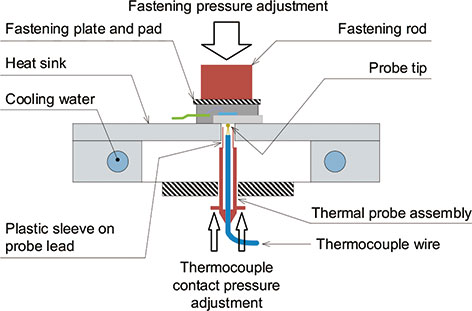

MIL-STD-883E의 METHOD 1012.1은 열 특성 테스트의 정의와 순서가 기재되어 있다. 정션에서 케이스까지의 열 저항에 대해서도 기재되어 있다. 이 표준은 1980년에 작성된 것으로, 현재로서는 문제점이 다수 포함되어 있다. 다음으로 테스트 방법에 대해 설명하겠다. 그림 2는 테스트 장치의 일례이다. 테스트하는 반도체 디바이스를 수냉식의 구리 히트싱크 위에 놓고, 접촉하는 케이스 표면 온도를 직접 열전대로 측정한다. 케이스가 히트싱크에 적절하게 접촉되도록 위에서 압력을 가한다. 히트싱크와 접촉된 케이스의 온도를 측정하기 위해 히트싱크에 구멍을 뚫어 열전대를 관통시킨다.

[그림 2] MIL-STD-883E METHOD 1012.1에서의 테스트 장치의 일례, 케이스 온도 측정

열전대의 앞쪽 끝부분은 용접하고, 도선은 전기적으로 절연되어 있어야 한다. 그림에서는 열 프로브 어셈블리 부분이다. 열전대의 앞쪽 끝부분은 케이스와 직접 기계적으로 접촉되어 있어야 하므로, 약간의 힘을 가해 접촉되도록 압력 조정 기구를 사용한다. 신뢰성이 높은 열 접촉을 실현하기 위해, 이러한 인터페이스에는 실리콘 그리스(silicone grease)가 사용되고 있다.

케이스 온도 TC의 측정 위치에 대해서는 케이스 온도란, 마이크로 전자 칩이 탑재되어 있는 패키지 상의 액세스 가능한 지정 기준점의 온도라고 정의되어 있다. 또한, 열전대는 디바이스 케이스의 아래쪽 중앙에 가능한 가까운 위치로, 칩 또는 서브 스트레이트(substrate)의 바로 밑에 장착한다고 기재되어 있다.

MIL-STD-883E 규격 테스트의 문제점

그럼, MIL-STD-883E 규격 테스트 방법의 문제점에 대해 설명하겠다. 열전대를 사용하는 케이스 온도의 측정은 에러가 발생되기 쉽기 때문에, 측정 결과의 재현성이 좋지 않다. 먼저, 케이스에는 온도 분포가 있으므로, 열전대와 케이스의 접점이 케이스의 최대 온도가 아닌 경우가 있다. 다음으로, 열 전대의 앞쪽 끝부분이 히트싱크에 대해 충분히 단열되어 있지 않아, 와이어 및 히트싱크로 인해 냉각되어, 케이스 온도의 측정치가 낮아질 가능성이 있다.

또한, 열전대를 관통시키기 위해 히트싱크에 뚫은 드릴 구멍으로 인해 영향을 받는다. 이러한 영향은 디바이스가 작을수록 커진다. 그 밖에도 사용하는 열전대 및 히트싱크의 성능으로 인해 측정 환경에 차이가 있으므로, 각 반도체 벤더에 따라 오차가 커지게 된다. 이 규격에서 설명하는 열전대 측정 시에는, 디바이스가 케이스에서 히트싱크로 적절하게 방열될 때, 정션 온도 TJ, 케이스 온도 TC, 및 가열 전력 손실 PH를 결정할 필요가 있다. 정션에서 케이스까지의 열 저항은 다음 식을 통해 계산한다. 케이스 온도의 측정 오차가 크므로, RthJC의 오차도 커지게 된다.

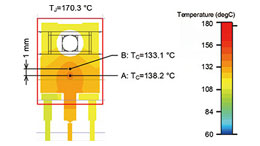

![]() (1)

(1)

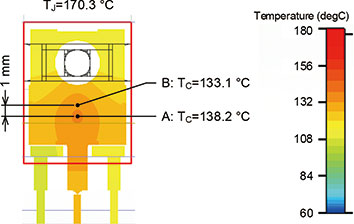

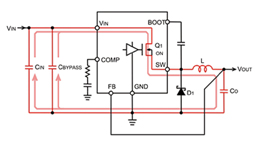

이러한 측정 방법은, 앞서 기술한 바와 같이 열전대를 사용하여 케이스 온도를 정확하게 측정하기 어려우며, 케이스의 표면은 히트싱크에 밀착되어 있다. 따라서, 측정 환경이 다른 경우에는 RthJC 값이 달라질 가능성이 있다. 그림 3은 측정 위치에서 오차가 발생하는 예를 나타낸 것이다. A 포인트와 B 포인트는 1mm 밖에 떨어져 있지 않지만, 5.1℃의 온도차가 발생한다.

[그림 3] 케이스 표면의 온도 분포 미세한 측정 위치 차이에도 온도차가 발생한다.

PH가 50W 일 때의 열 저항을 계산하면 다음과 같아진다.

A 포인트에서 측정 시,

![]()

B 포인트에서 측정 시,

![]()

이 예에서는 불과 1mm의 측정 위치 차이로 인해 열 저항에 16%의 오차가 생기므로, 측정 위치의 지정이 중요하다는 것을 알 수 있다.

JEDEC Standard의 테스트 방법

JEDEC Standard JESD51-14는 2010 년에 작성된 규격이다. Transient Dual Interface(TDI) 테스트 방법을 사용하여, 열전대를 통해 케이스 온도를 측정하지 않고도 정션에서 케이스까지의 열 저항 측정을 실현한다. 이에 따라, RthJC 측정의 재현성이 향상되어, 벤더에 따른 측정 데이터의 오차를 개선할 수 있다. 이는 현재 MIL-STD 를 대신하여 일반적으로 사용되는 방법이다. 먼저, 측정 원리의 개요에 대해 설명하겠다.

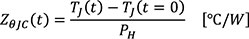

케이스 표면이 히트싱크(냉각판)를 통해 적절하게 냉각될 때, 시간 t=0 부터 시작되는 정전력 PH로 가열되는 반도체 디바이스의 열 임피던스 또는 Zth 함수 ZθJC(t)는 다음과 같이 정의할 수 있다.

(2)

(2)

즉, 열 임피던스는 정션 온도의 시간의존 변화 TJ(t)를 가열 전력 PH로 나눈 값과 동일해진다. 케이스의 냉각 조건이 변경되어도, 냉각판에 접촉되는 케이스에서 온도가 상승하기 시작할 때까지는, 열 임피던스에 영향을 미치지 않다. 단, 케이스와 냉각판 사이의 접촉 저항이 다른 경우에는, 정상 상태에서의 총 열 저항이 변화하므로 측정되는 임피던스 곡선이 달라진다. 이렇게 접촉 저항이 다른 2가지의 열 임피던스를 측정하고, 이러한 2가지 곡선 분리점에서의 누적 열 저항을 RthJC(RθJC, θJC)로 정의하고 있다.

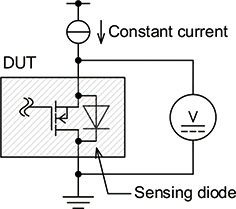

앞서 기술한 바와 같이, 냉각판과 케이스 표면 사이에서 상이한 접촉 저항(냉각 조건)을 사용하고, 정션 온도의 과도 측정에만 준거한다. 케이스 온도 TC의 열전대를 사용한 측정을 위한 테크닉이 필요하지 않으므로, 이와 관련된 모든 에러가 배제된다. 이 방법은 정션 온도의 측정에만 의존한다. 다음으로 테스트 방법의 순서에 대해 설명하겠다. 먼저 테스트 대상 디바이스(Device under test : DUT)의 정션 온도를 측정하기 위해, 사전에 DUT의 온도 파라미터를 취득한다. DUT가 MOSFET 인 경우에는, 그 Body 다이오드를 사용하고, 이를 센싱 다이오드로 한다.

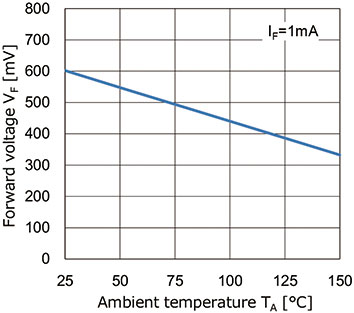

또한, 디바이스의 종류에 따라 측정하는 위치는 달라진다. pn 접합의 순방향 전압의 온도 특성이 대략 -2mV/℃로 변화하는 것을 이용하여, DUT 내부에 존재하는 pn 접합의 온도 특성을 사전에 측정함으로써 정션 온도를 측정할 수 있다. 그림 4는 측정 회로를 나타낸 것이다. 센싱 다이오드에 전류을 인가하여 순방향 전압을 측정한다. 발열원인 디바이스는 항온조 등의 온도 조절기를 사용하여, 25℃에서 디바이스의 최대 정션 온도까지 변화시키면서 각 온도에서의 순방향 전압을 측정한다.

[그림 4] DUT 내부 다이오드 소자의 순방향 전압 측정 회로

온도를 변화시킬 때, 칩(정션)에 열이 전달되기까지 시간이 걸리므로, 순방향 전압이 안정될 때까지 시간을 둔다. 이 측정 방법은 정션 을 비롯한 디바이스 전체의 온도가 동일하다는 것을 전제로 하고 있다.

그림 5는 측정 결과의 일례이다. 소자의 치수 및 재료가 다르면 다소 특성이 달라지지만, 온도 특성은 대략 -2mV/℃의 1차 함수 그래프를 나타냅니다. 이러한 기울기를 K 팩터라고 한다.

[그림 5] DUT 내부에 존재하는 다이오드 소자의 순방향 전압 온도 특성의 일례

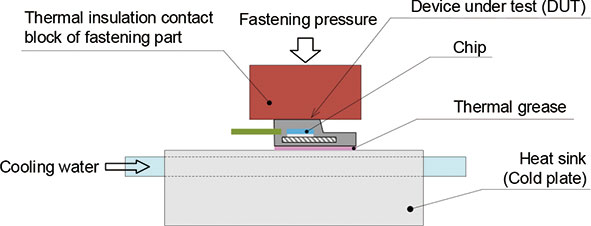

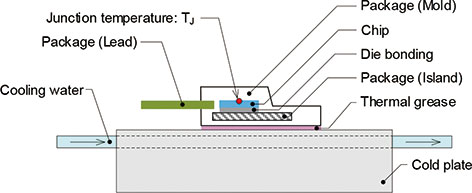

과도 열 측정 장치를 사용하여 열 임피던스를 측정한다. 그림 6은 테스트 환경의 일례이다. 냉각수로 온도를 관리하는 구리 냉각판 위에 DUT 를 장착한다.

[그림 6] TDI 방법의 테스트 환경 일례

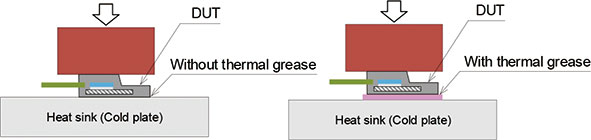

이때, 그림 7과 같이 DUT 와 냉각판 사이에 서멀 그리스(thermal grease)가 없는 경우와 있는 경우로 구분하여 측정한다.

[그림 7] DUT와 냉각판 사이에 서멀 그리스 유무로 구분하여 측정

열 임피던스의 측정 순서는 다음과 같다.

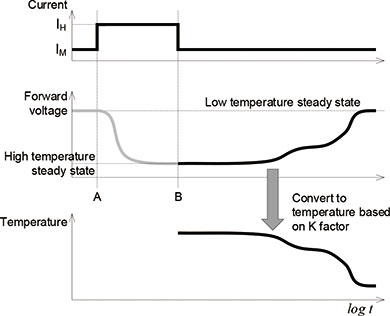

① DUT 내부의 가열 소자에 일정한 가열 전류 IH를 공급하여, 칩의 온도를 상승시킨다. 가열 소자는 MOSFET일 경우, Body 다이오드를 사용할 수 있다. 그림 8의 A 포인트가 가열 전류를 공급하기 시작하는 지점이다. 정션 온도가 일정해질 때까지 계속 가열하며, 정션 온도의 변화는 센싱 다이오드의 순방향 전압으로 모니터링한다.

② 정션 온도가 고온에서 안정되면, 가열 전류 IH의 공급을 중지하고, 순방향 전압 측정 전류 IM으로 신속하게 전환한다. 그림 8의 B 포인트가 전류를 전환한 지점이다. 여기에서부터 순방향 전압이 저온 정상 상태가 될 때까지 시계열로 데이터를 기록한다(그림 8의 중간 그래프).

[그림 8] 과도 냉각 곡선의 측정

③ 기록한 순방향 전압 데이터를 K 팩터에 준거하여, 온도로 변환한다(그림 8 아래쪽 그래프). 이것이 과도 냉각 곡선이다.

④ 과도 냉각 곡선의 데이터를 수치 연산하여 구조 함수로 변환한다.

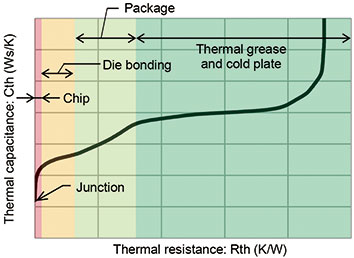

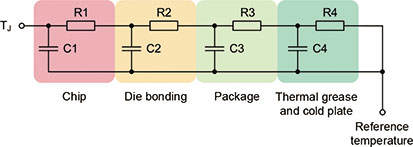

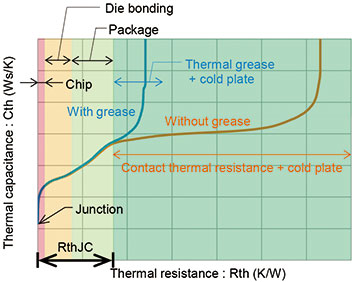

구조 함수는 디바이스 구조의 전열 경로를, 열 저항과 열 용량의 1차원 열 회로로 나타낸 것으로, 디바이스의 열 구조를 가시화할 수 있다. 그림 9는 구조 함수의 일례이며, 그림 10은 1차원 RC 열 회로망이다. 또한, 이때의 디바이스 구조를 그림 11로 나타내었다. 과도 열 측정 장치로 얻어진 구조 함수는 3차원 온도 분포의 영향이나 열 저항과 열 용량을 세분화한 네트워크로서 표현되었으므로, 그림 11의 디바이스 구조에 표시되어 있는 칩과 다이본딩 사이 등, 각각의 경계는 그다지 명확하지 않다.

[그림 9] 구조 함수의 일례

또한, 그림 10의 각 소자가 그림 11의 각 요소에 존재하는 열 저항과 열 용량에 1 대 1로 대응하는 것은 아니다. 그러나, 본 자료에서는 구조 함수의 이해를 위해 편의상 경계를 구분하여 설명하고 있다.

[그림 10] 1차원 RC 열 회로망

[그림 11] 디바이스 구조의 일례

이러한 측정 방법을 서멀 그리스가 없는 경우와 있는 경우로 구분하여 실시한다. 그림 12는 두가지 측정 결과를 구조 함수로 변환하여 합성한 것이다. 그리스가 없는 경우는 케이스와 냉각판 사이의 접촉 저항이 높다는 것을 알 수 있다. 이와 같이 그리스의 유무에 따라, 도중에 곡선이 분기된다(나누어진다). 분기 포인트는 케이스와 서멀 그리스의 계면을 나타내므로, 정션에서 분기 포인트까지의 열 저항이 RthJC가 된다.

[그림 12] 서멀 그리스가 없는 경우와 있는 경우의 구조 함수를 합성한 그래프

상기와 같이, 케이스 표면과 냉각판 사이에서 상이한 접촉 저항을 사용하고, 정션 온도의과도 측정에만 준거하므로, 케이스 표면 온도 TC는 열전대를 사용하여 측정하는 테크닉을 필요로 하지 않는다. 따라서, 이와 관련된 에러가 배제되므로, 이 방법을 사용하면 측정 정밀도가 높은 열 저항을 얻을 수 있다. 로옴의 디스크리트 제품은 JESD51-14 에 준거하여 RthJC 측정을 실시하고 있다.

RthJC의 사용법

RthJC는 다른 종류의 패키지에 대한 방열 성능 비교에 사용할 수 있다. 예를 들어, 어떤 기기에 실장되어 있는 디바이스를 호환성이 있는 다른 디바이스로 대체할 경우, 각각의 RthJC 값을 통해 정션 온도가 상대적으로 몇 ℃변화하는지를 구하는 용도로 사용한다. 잘못된 사용법으로는, 히트싱크와 접촉하는 패키지 표면 온도 TC를 열전대로 측정하고, 식 (3)을 사용하여 정션 온도를 구하는 방법이다.

![]() (3)

(3)

JESD51-14의 RthJC에서 정의하고 있는 TC에 상당하는 온도 측정점은 물리적으로 존재하지 않는다. 케이스의 적당한 위치를 TC로 하여 TJ를 구하는 방법으로, 식 (3)을 사용하지 않도록 주의하자.

[참고 자료]

[1] JESD51-1:1995, Integrated Circuit Thermal Measurement Method - Electrical Test Method

[2] JESD51-14:2010, Transient Dual Interface Test Method for the Measurement of the Thermal Resistance 정션 to Case of Semiconductor Devices with Heat Flow Through a Single Path

[3] MIL-STD-883E, METHOD 1012.1, Thermal Characteristics, 4 November 1980

범용 전원 IC로 전원 시퀀스를 실현하는 회로

조회수 875회 / 로옴코리아

열 설계와 기술 트렌드의 변화

조회수 1300회 / 로옴코리아

평활 후의 DC/DC 안정화 방식

조회수 1081회 / 로옴코리아

DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃 부품 배치 방법(2)

조회수 2459회 / ROHM

DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃의 대원칙(1)

조회수 1652회 / ROHM

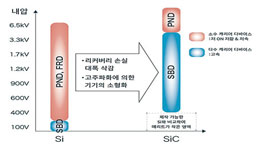

SiC 파워 디바이스란?

조회수 5312회 / ROHM

열 저항 RthJC의 측정 방법과 사용법

조회수 3335회 / 로옴코리아

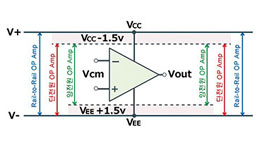

연산증폭기와 비교기란?

조회수 4448회 / ROHM

열 저항과 방열의 기본

조회수 11327회 / ROHM

PDF 다운로드

회원 정보 수정