연산증폭기와 비교기란?

자료제공/로옴코리아

연산증폭기란?

연산증폭기(Operational Amplifier)는 고입력 저항, 저출력 저항, 높은 개방 이득(오픈 루프 게인)이 특징이며, +입력단자와 -입력단자간 전압차를 증폭시키는 기능을 지닌 차동 증폭기이다.

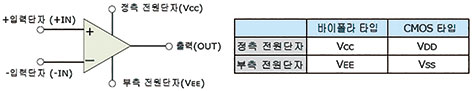

1회로당 정측 전원단자, 부측 전원단자, +입력단자, -입력단자, 출력단자의 5개 단자로 구성되어 있다(그림 1참조).

[그림 1] 연산 증폭기 기호도와 단자명

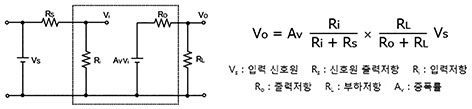

연산증폭기에 요구되는 기능으로서 높은 입력저항(임피던스), 낮은 출력저항이 있다. 그림 2에서 입력전압과 출력전압의 관계는 다음 식으로 나타낸다.

[그림 2] 전압 제어 전압원 증폭기 모델

신호전압 Vs, 신호원 저항 Rs와 연산증폭기의 입력저항 Ri에 의해 저항 분할되어 분압되므로 감쇄된 신호가 연산증폭기에 입력된다. 그러나, Rs보다 Ri가 충분히 크면(Ri = ∞), 식의 제1항은 1에 가까워지므로 Vs = Vi라고 생각할 수 있다.

다음 제2항에서 증폭된 입력전압 AvVi는 연산증폭기의 출력저항 Ro와 부하저항 RL로 분압되어 출력된다. 이 때, RL보다 Ro가 충분히 작으면(Ro = 0), 제2항은 1에 가까워지므로 신호가 감쇄되지 않고 출력됨을 알 수 있다. 이러한 연산증폭기를 이상적 연산증폭기라고 한다.

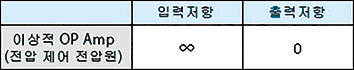

통상적 연산증폭기는 높은 입력저항, 낮은 출력저항이 요구되며, 회로 구성은 이상적 연산증폭기에 가까워지도록 설계한다(그림 3 참조).

[그림 3]

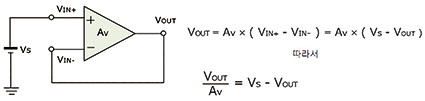

연산증폭기는 +입력단자와 -입력단자간 미세한 전압차를 증폭하여 출력한다. 따라서, 연산증폭기는 높은 증폭률이 요구된다. 그 이유는 그림 4를 사용하여 해설할 수 있다.

[그림 4] 전압 플로어 회로와 수식

전압 폴로어 회로란 입력전압과 출력전압이 같아지는 회로이다. 주로 전압 버퍼로서 사용되며, 높은 입력저항 및 낮은 출력저항의 특성을 살린 회로로서, 입력전압 Vs와 VOUT은 같아진다. 연산증폭기는 단자간 전압차를 연산증폭기의 증폭률로 증폭하므로, 출력전압은 다음과 같이 나타낸다.

연산증폭기의 개방 이득 Av가 충분히 커지면, 좌변은 0에 가까워지므로 Vs = VOUT이 된다. 이득이 낮은 경우, 식의 좌변은 0에 가까워지지 못하므로 출력전압에 오차가 발생한다. 연산증폭기에 대해 높은 개방 이득이 요구되는 것은 이 이득을 통해 출력전압 오차를 가능한 작게 하기 위함이다.

개방 이득이 크다는 점을 다르게 생각하면, +입력단자와 -입력단자의 전위차를 가능한 작게 한다는 의미이다. 즉, 개방 이득이 커질수록 VIN+ = VIN-의 관계가 성립한다. 이 +입력단자와 -입력단자의 전위가 거의 같아지는 관계를 virtual short, imaginary short 또는 가상 접지라고 한다. 부귀환 회로를 구성하여 사용할 경우에는 이러한 관계가 성립하므로, 가상 접지 특성을 이용하여 응용회로를 설계한다.

연산증폭기의 회로 구성

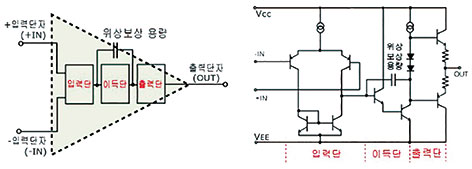

그림 5는 연산증폭기의 내부 회로 구성을 나타낸 것이다. 일반적으로입력단, 이득단, 출력단의 3단으로 구성되어 있다. 입력단은 차동 증폭단으로 구성되어 있으며, 2개의 단자간 전압차를 증폭시킨다. 또한, 동상 신호 성분(단자간 전위차가 없거나, 동등한 전압이 입력되어 있는 상태)은 증폭되지 않고 소거된다.

[그림 5] 일반적인 연산증폭기 내부회로와 BA4558 등가회로

이 차동 증폭 회로만으로는 이득이 불충분하므로, 이득단을 통해 연산증폭기의 개방 이득을 한층 더 증가시킨다. 일반적인 연산증폭기에서는 이득단 사이에 발진 방지용 위상보상 용량이 접속되어 있다. 출력단은 출력단자에 접속되는 저항 등 부하의 영향에 의해 연산증폭기의 특성이 변화되지 않도록 버퍼로서 접속되어 있다. 부하에 의한 출력의 특성 변화(왜곡, 전압 강하 등)는 주로 출력단의 회로 구성과 전류 능력에 의존한다.

출력단의 종류로서는 일반적으로 A급, B급, C급, AB급 출력회로가 있으며, 출력회로에 흐르는 드라이브 전류의 양(바이어스 전압의 차이)에 따라 분류된다. 드라이브 전류량의 차이에 따라 출력단에서 발생하는 왜곡의 레벨이 달라진다. 일반적으로 왜곡이 작은 순으로 회로를 나열하면 A급, AB급, B급, C급이다.

비교기의 회로 구성

그림 6은 비교기의 회로 구성이다. 회로 구성은 연산증폭기와 거의 동일하지만, 부귀환을 구성하여 사용하는 것은 고려되어 있지 않으므로, 발진 방지용 위상보상 용량은 내장되어 있지 않다. 위상보상 용량은 입출력간 동작 속도를 제한하기 때문에 응답 시간은 연산증폭기에 비해 매우 우수한다.

비교기의 출력회로 형식은 주로 오픈 콜렉터(오픈 드레인) 타입, 푸시-풀 타입으로 분류된다. BA10393의 내부 등가회로는 오픈 콜렉터 타입의 출력회로이다.

[그림 6] 일반적인 비교기의 내부회로와 BA10393 등가회로

연산 증폭기의 종류

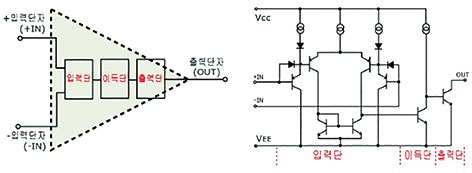

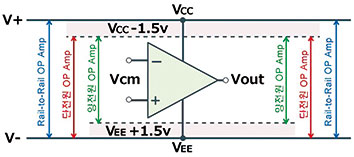

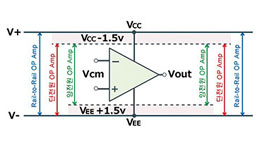

연산 증폭기의 종류는, 입출력 전압 범위에 따라 양전원 연산증폭기, 단전원 연산증폭기, Rail-to-Rail 연산증폭기로 크게 분류할 수 있다. 각 연산증폭기의 입출력 전압 범위는 그림 7을 참조한다.

[그림 7] 연산증폭기 입출력 전압 범위의 예

(1) 양전원 연산증폭기

연산증폭기는 일반적으로 0V에 가까운 미세 신호를 증폭시키는 경우가 많으므로, 양전원 연산증폭기에서 0V의 입력이 필요한 경우에는 VEE를 마이너스 1.5V 이하로 해야 한다. 이러한 이유에서 부전원을 사용하는 케이스가 대부분이며, 플러스·마이너스 전원이 모두 필요하므로, 양전원 연산증폭기라고 한다.

(2) 단전원 연산증폭기(그라운드 센스)

0V 부근의 신호를 입력하는 경우, 양전원(범용) 연산증폭기를 사용하면 부전압이 필요하지만, 부전압을 사용하지 않고도 입력 가능한 연산증폭기가 단전원 연산증폭기다. 그라운드 레벨의 입력 신호까지 동작 가능하므로 그라운드 센스 연산증폭기라고 한다.

(3) Rail-to-Rail 연산증폭기(입출력 풀 스윙)

저전력화가 중요시됨에 따라, 저전압으로 구동하는 세트가 많아지고 있다. 연산증폭기 역시 저전압 동작이 필요하지만, VCC 전압이 5V 부근까지 낮아지면, 단전원 연산증폭기의 경우 VCC보다 1.5V 낮은 전압까지 밖에 입력할 수 없어 불편한 상황이 생기게 된다. 이에 따라, 입력전압이 VEE에서 VCC까지 변동되어도 정상적으로 동작하는 Rail-to-Rail 연산증폭기가 등장하였다. 전원전압(VEE ~ VCC) 범위에서의 입출력이 가능하므로, 입출력 풀 스윙 연산증폭기라고 한다.

노이즈 특성

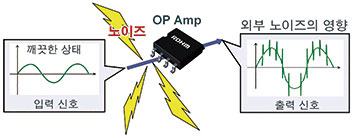

부품의 전자화, 고밀도화로 인해 노이즈 환경이 더욱 악화됨에 따라, 센서 등 미세한 신호를 증폭하는 연산증폭기에 있어서도 노이즈 대책이 큰 과제로서 중요시되고 있다. 최근에는 이러한 노이즈 과제에 대응하는 연산증폭기도 다수 라인업되고 있으며, 그 수요도 증가하고 있다. 그럼, 노이즈의 정의에 대해 설명하겠다.

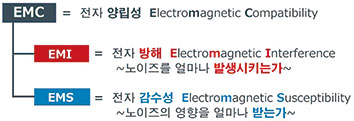

일반적으로 노이즈는 EMC(Electromagnetic Com-patibility/전자 양립성)라고 부르며, 다른 기기에 대해 노이즈로 인한 영향을 미치지 않고, 다른 기기로부터 노이즈의 영향을 받아도 본래의 성능을 유지한다는 두가지 성능을 의미한다. 그러나, 구체적으로 사용되는 경우에는, EMC에서 분류되는 EMI와 EMS라는 두가지 종류의 표현을 사용한다.

[그림 8] 노이즈의 정의

(1) EMI(전자 방해)

EMI는, 대상이 되는 제품의 동작으로 인해 노이즈가 얼마나 발생하여 주변의 IC나 시스템에 영향을 미치는지에 대한 지표로서 사용된다. EMI 특성이 좋다는 것은, 노이즈 발생이 적다는 것을 의미한다.

연산증폭기가 지닌 노이즈는 입력 환산 노이즈 전압이라고 불리우며, 회로·프로세스의 요인으로 인해 발생한다. 이러한 노이즈는 신호 증폭 시 오차 전압이 되어 증폭의 정밀도에 영향을 미치게 된다.

[그림 9] 연산증폭기에서 발생되는 노이즈의 영향

(2) EMS(전자 감수성)

외부 노이즈는 IC 및 세트 오동작의 원인이 된다. EMS는, 대상이 되는 제품이 외부 노이즈의 영향을 받아도 오동작을 일으키지 않는 능력·내성의 지표로서 사용된다. 따라서, EMS 특성이 좋다는 것은, 노이즈의 영향을 받지 않는다는 것을 의미한다.

연산증폭기 업계에서는 EMS 특성이 우수하여 노이즈의 영향을 받지 않는다는 것을, 외부 노이즈의 전자 방해(EMI)에 대해 높은 내성을 지닌다는 의미에서 높은 EMI 내량(내성)이라는 표현을 사용한다.

EMS 특성이 우수하다 = 높은 EMI 내량

즉, 높은 EMI 내량 연산증폭기란, 외부 노이즈의 영향을 받지 않는 연산증폭기라는 의미이다.

[그림 10] 외부 노이즈의 영향

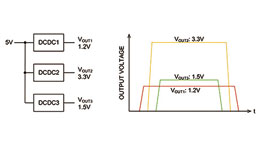

범용 전원 IC로 전원 시퀀스를 실현하는 회로

조회수 874회 / 로옴코리아

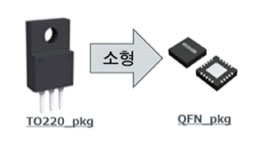

열 설계와 기술 트렌드의 변화

조회수 1300회 / 로옴코리아

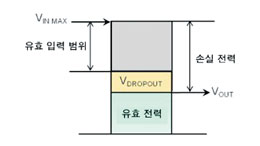

평활 후의 DC/DC 안정화 방식

조회수 1081회 / 로옴코리아

DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃 부품 배치 방법(2)

조회수 2457회 / ROHM

DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃의 대원칙(1)

조회수 1651회 / ROHM

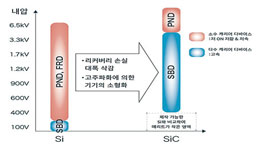

SiC 파워 디바이스란?

조회수 5309회 / ROHM

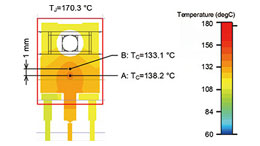

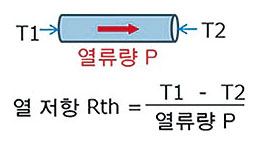

열 저항 RthJC의 측정 방법과 사용법

조회수 3331회 / 로옴코리아

연산증폭기와 비교기란?

조회수 4446회 / ROHM

열 저항과 방열의 기본

조회수 11317회 / ROHM

PDF 다운로드

회원 정보 수정