범용 전원 IC로 전원 시퀀스를 실현하는 회로

글/로옴코리아

FPGA나 DSP와 같이 복잡한 기능을 지닌 여러 개의 전원을 필요로 하는 IC나, 복수 계통의 전원을 필요로 하는 전자기기에서는 전원의 투입이나 차단의 순서가 사양으로 정해져 있는 경우가 있다. 이러한 사항을 지키지 않으면 정상적으로 기동하지 않을 뿐만 아니라, 경우에 따라서는 디바이스를 손상시키기도 한다.

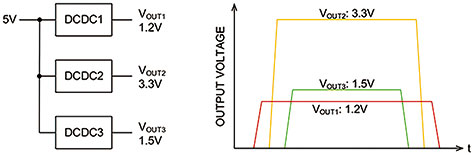

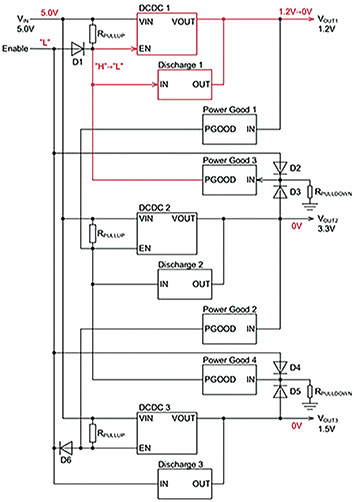

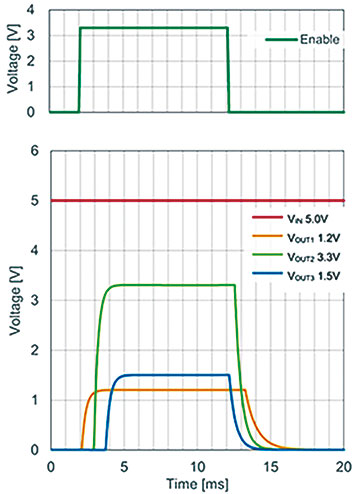

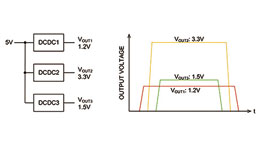

여러 개의 전원을 투입하거나 차단할 때의 순서를 전원 시퀀스라고 한다. 하기 그림 1은 3계통 전원에 관한 시퀀스 제어의 이미지이다.

(1) 전원 투입 시의 시퀀스 동작

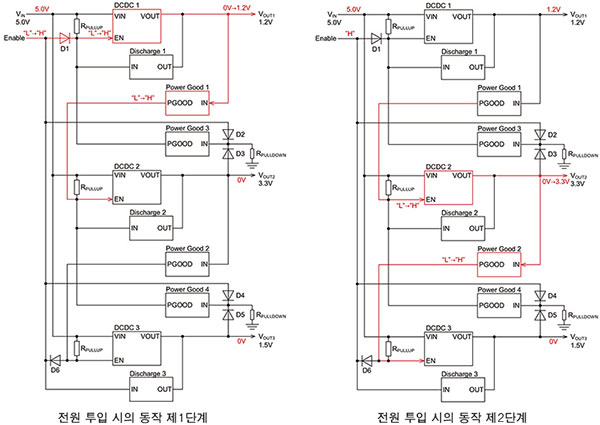

앞서 설명한 바와 같이 1.2V, 3.3V, 1.5V의 3계통 출력이 순서대로 투입되는 시퀀스이다. 이러한 시퀀스 동작을 순서에 따라 설명하겠다. 본 고에서는 1.2V 투입 동작을 제1단계, 3.3V 투입 동작을 제2단계, 1.5V 투입 동작을 제3단계, 3계통 모두가 투입된 상태를 전원 동작 시라고 표현하겠다. 각 단계의 그림에서는 설명에 해당되는 부분을 적색으로 표시하였다.

초기 상태는 Enable 단자가 “L” 레벨이고, 3개의 DC-DC 출력은 제로이다.

(2) 제1단계 전원 투입 시의 동작

1) 전원을 기동하기 위해 Enable 단자를 “H” 레벨로 한다.

2) 다이오드 D1을 통해 DC-DC 1의 EN 핀이 “H”가 되므로 DC-DC 1이 기동한다.

3) DC-DC 1의 출력전압이 0V에서 1.2V로 상승하면 Power Good 1의 출력이 “L”에서 “H” 레벨로 변화하여, 다음 단의 DC-DC 2의 EN 핀이 “H”가 된다.

4) Power Good 3과 Power Good 4의 IN 핀은 다이오드 D2 및 D4에 의해 “H” 레벨이 되므로, PGOOD 핀(출력)은 높은 임피던스를 유지한다.

[그림 2] 전원 투입시의 동작 제1단계(a), 전원 투입 시의 동작 제2단계(b)

(3) 제2단계 전원 투입 시의 동작

1) DC-DC 2의 EN 핀이 “H”가 되었으므로, DC-DC 2가 기동한다.

2) DC-DC 2의 출력전압이 0V에서 3.3V로 상승하면, Power Good 2의 출력이 “L”에서 “H”로 변화하고 후단의 DC-DC 3의 EN 핀이 “H”가 된다.

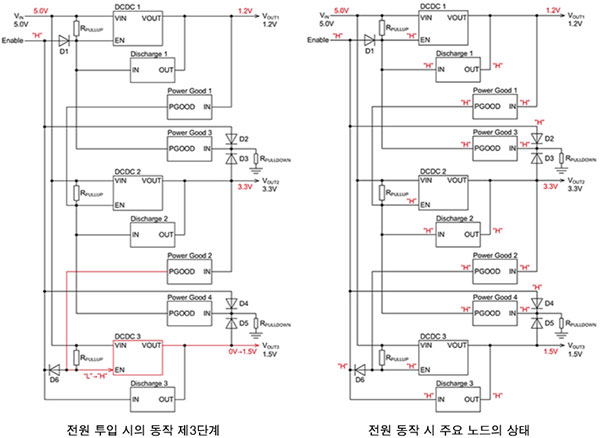

(4) 제3단계 전원 투입 시의 동작

1) DC-DC 3의 EN 핀이 “H”가 되었으므로 DC-DC 3이 기동한다.

2) DC-DC 3의 출력전압이 0V에서 1.5V로 상승하여, 3계통 모든 전원이 동작(전원 동작 시 주요 노드의 상태를 별도 그림으로 표시).

[그림 3] 전원 투입시의 동작 제3단계(a), 전원 동작 시 주요 노드의 상태(b)

전원 차단 시의 시퀀스 동작

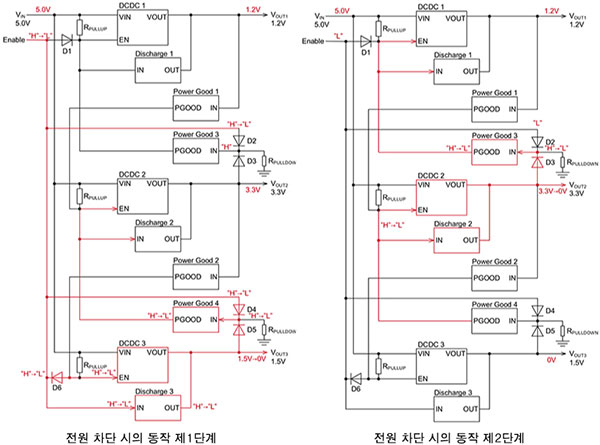

앞서 설명한 전원 투입 시의 시퀀스에 이어, 전원 차단 시의 시퀀스 동작에 대해 설명하겠다. 전원의 차단은 1.5V, 3.3V, 1.2V의 순서이다. 여기서는 1.5V 차단 동작을 제1단계, 3.3V 차단 동작을 제2단계, 1.2V 차단 동작을 제3단계로 하였다. 각 단계의 그림에서는 설명에 해당되는 부분을 적색으로 표시하였다.

(1) 제1단계 전원 차단 시의 동작

1) 전원을 차단하기 위해 Enable 단자를 “L” 레벨로 한다.

2) 다이오드 D6을 통해 DC-DC 3의 EN 핀이 “L”이 되므로 DC-DC 3이 차단된다.

3) 동시에 Discharge 3의 IN 핀도 “L”이 되므로, Discharge 3의 OUT 핀이 낮은 임피던스로 변화한다. 이에 따라 DC-DC 3의 출력전압은 빠르게 0V로 변한다.

4) DC-DC 3의 출력전압이 낮아지면, Power Good 4의 출력전압이 “H”에서 “L”로 변하므로, 전단의 DC-DC 2의 EN 핀 및 Discharge 2의 IN 핀이 “L”로 변한다.

[그림 4] 전원 차단 시의 동작 제1단계(a), 전원 차단 시의 동작 제2단계(b)

(2) 제2단계 전원 차단 시의 동작

1) DC-DC 2의 EN 핀이 “L”이 되므로 DC-DC 2가 차단된다.

2) 동시에 Discharge 2의 IN 핀도 “L”이 되므로, Discharge 2의 OUT 핀이 낮은 임피던스로 변화한다. 이에 따라 DC-DC 2의 출력전압은 빠르게 0V로 변한다.

3) DC-DC 2의 출력전압이 낮아지면, Power Good 3의 출력전압이 “H”에서 “L”로 변하므로, 전단의 DC-DC 1의 EN 핀 및 Discharge 1의 IN 핀이 “L”로 변한다.

(3) 제3단계 전원 차단 시의 동작

1) DC-DC 1의 EN 핀이 “L”이 되므로 DC-DC 1이 차단된다.

2) 동시에 Discharge 1의 IN 핀도 “L”이 되므로, Discharge 1의 OUT 핀이 낮은 임피던스로 변화한다. 이에 따라 DC-DC 1의 출력전압은 빠르게 0V로 변한다.

3) 이것으로 3계통 모든 전원의 차단이 종료된다.

[그림 5] 전원 차단 시의 동작 제3단계

회로와 정수 계산 예

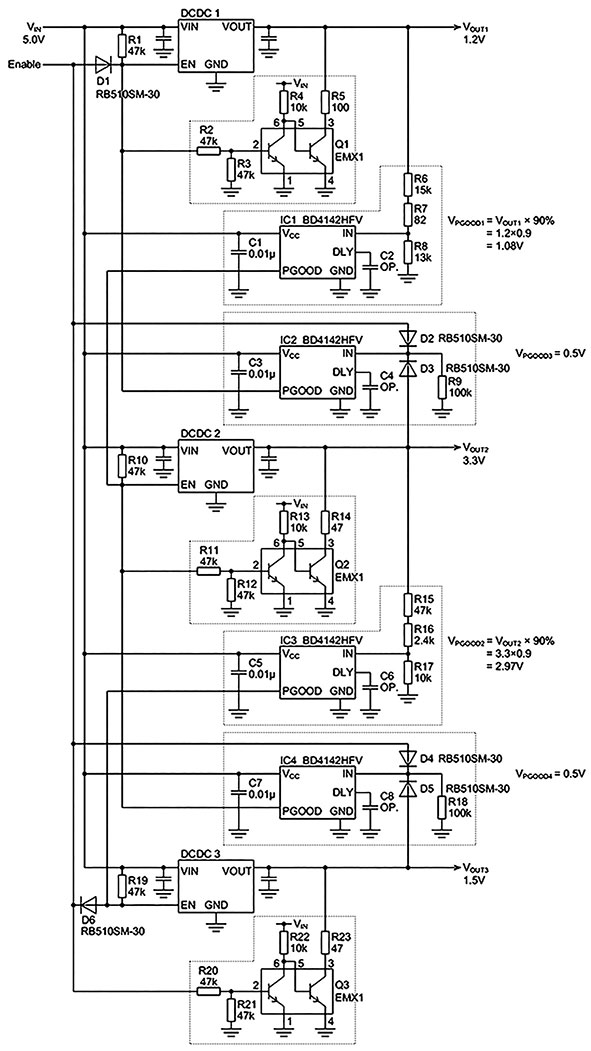

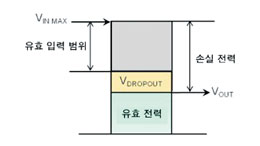

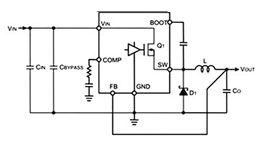

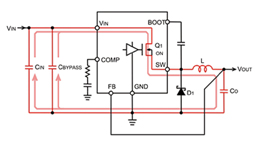

하기 그림 6은 전원 시퀀스를 실현하는 회로 예이다. 3계통의 DC-DC 1~3은 스위칭 레귤레이터 또는 리니어 레귤레이터(LDO)를 가정한 것이다. 각 DC-DC는 출력을 ON/OFF 할 수 있는 EN(Enable) 핀을 구비하고 있다.

[그림 6] 전원 시퀀스 ①을 실현하는 회로 예

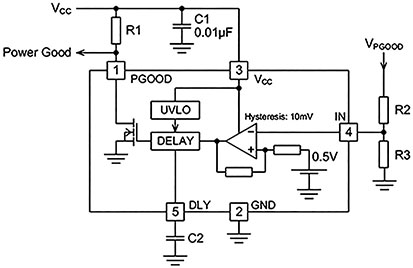

(1) Power Good 블록

Power Good 블록은 4개로, 전압 감시용 IC인 BD4142HFV를 사용하여 Power Good 기능을 실현하였다. IC 1과 IC 3은 전원 투입 시의 DC-DC 출력전압이 설정치에 도달한 것을 검출하는 용도, IC 2와 IC 4는 전원 차단 시의 강하 검출 용도이다. 하기 그림은 BD4142HFV의 내부 기능 블록을 포함한 Power Good 회로를 나타낸 것이다.

(2) BD4142HFV로 구성한 Power Good 기능

이 IC는 0.5V의 기준전압을 구비한 히스테리시스 탑재 콤퍼레이터를 내장하고 있으며(IC의 기능 블록 참조), 외장 분압 저항을 사용하여 검출하고자 하는 전압을 설정할 수 있다. DC-DC 출력전압의 기동을 검출하는 IC 1과 IC 3에는 DC-DC의 출력전압에 따라 이러한 설정이 필요한다. 검출전압 VPGOOD은 식 1과 같이 계산할 수 있다.

![]() (1)

(1)

시퀀스 회로 예의 VOUT1은 1.2V로, IC 1의 PGOOD은 출력전압의 90%에 도달한 시점에서 플래그를 출력하도록 설정되어 있다. 검출전압을 95%와 같이 지나치게 높게 하면, 부하 변동으로 인해 출력전압이 순간적으로 저하될 때 PGOOD 출력이 “L”이 되므로, 후단의 DC-DC가 순간적으로 차단되는 문제가 발생한다. 따라서, DC-DC의 부하 변동과 전압 저하(부하 응답)의 특성을 파악한 후에 검출전압을 결정해야 한다.

90%일 때, 검출전압은 1.2V × 0.9 = 1.08V가 된다. 식 1을 바탕으로 저항치를 구할 수 있다. 회로 예의 IC 1에는 계산된 저항치가 이미 제시되어 있다. 식 1의 R2에 해당하는 것은 R6 : 15kΩ+R7 : 82Ω, R3은 R8 : 13kΩ이다. 이를 대입하면 다음 식과 같아지며, 원하는 1.08V가 얻어지는 정수임을 알 수 있다.

![]()

식에서 알 수 있듯이, IN 단자에 인가되는 R2와 R3에 의한 분압 전압이 내부 기준 전압인 0.5V가 되도록 VPGOOD에 대해 저항치를 결정한다. 전압은 저항비로 결정되는데, 분압 저항도 DC-DC의 부하가 되므로, 10kΩ 대의 저항치로 구성하는 것이 적당하다. 단, R2와 R3의 합계는 300kΩ 이내가 된다.

이로써 기본 정수는 결정되지만, 설계로서는 설정치(검출전압)의 허용차를 확인해야 한다. BD4142HFV의 검출전압 허용차는 ±1.8%이다. 따라서, PGOOD의 범위는 88.4%(90%의 -1.8% = 90 × 0.982)에서 91.6%(90%의 +1.8%=90 ×1.018)가 된다.

그리고, 10mV의 히스테리시스가 있으므로, 검출 해제 전압은 90% × (0.5V - 10mV) ÷ 0.5V =88.2%가 되어, 범위는 88.2% × 0.982 = 86.6%에서 88.2% × 1.018 = 89.8%가 된다.

BD4142HFV는 PGOOD 플래그 출력에 지연 시간 tDELAY를 부여할 수 있다. 이 경우, DLY 단자에 콘덴서 C2를 접속한다. 지연 시간과 콘덴서 C2의 식은 식 2로 계산할 수 있다.

![]() (2)

(2)

전원 차단 시에 동작하는 PGOOD의 IC 2와 IC 4는 DC-DC의 출력전압이 약 0.5V 이하로 강하되면 검출 해제(PGOOD 출력이 “H”에서 “L”로 변화)된다. 이는 BD4142HFV에 기본적으로 설정되어 있는 검출전압을 그대로 이용한다.

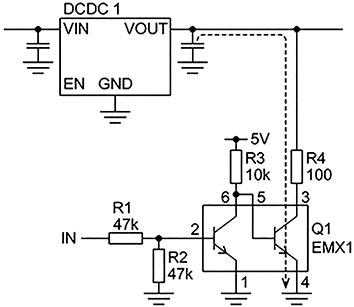

(3) 방전 회로

디스크리트로 구성된 방전 회로가 각 DC-DC에 접속되어 있다. 하기 그림 8과 같이 NPN 트랜지스터와 저항으로 구성되어 있다. 1단째의 트랜지스터는 단순한 인버터 회로, 2단째는 오픈 콜렉터의 스위치이다. 2단째가 ON되면, DC-DC 차단 시 주로 출력 콘덴서의 잔존 전하를 방전하여, 빠르게 VOUT을 강하시킨다. 2단째 트랜지스터의 콜렉터에 직렬로 접속되어 있는 저항(그림 8에서는 R4)의 값에 따라, 출력전압의 강하 시간을 조정한다.

[그림 8] 방전 회로

다이오드

시퀀스 회로 예 각 부분에 배치된 다이오드는 로직 동작을 담당한다. 다이오드의 순방향 전압 VF는 “L” 레벨의 신호 전압에 영향을 미치므로, “L” 레벨로서의 전압치를 확보하기 위해 VF가 낮은 쇼트키 배리어 다이오드를 사용한다.

실제의 동작 예

실제 동작 확인용으로 그림 6을 참조하면 된다. 다음으로, 실제의 동작 파형이다. VIN 5.0V가 인가된 상태에서, VOUT의 ON/OFF를 제어하는 Enable이 “H” 레벨이 되면, VOUT의 기동이 시작된다. 먼저 DC-DC 1에 의한 VOUT1 1.2V가 기동된다. 파형도에서는 황색 파형이다.

VOUT1이 Power Good 블록 IC 1에 설정한 임계치인 VOUT1의 90%에 해당하는 전압에 도달하면, PGOOD 출력이 DC-DC 2를 Enable하여, 2번째 출력 VOUT2 3.3V(황녹색)의 기동이 시작된다.

마찬가지로 VOUT2가 90%에 해당하는 전압에 도달하면, Power Good 블록 IC 3이 DC-DC 3을 Enable하여, 3번째 출력 VOUT3 1.5V(하늘색)의 기동이 시작된다.

이것이 기동 시의 시퀀스 동작이다. 차단 시에는 기동 시와 반대의 순서로 VOUT3부터 차단된다. Enable이 “L” 레벨이 되면, DC-DC 3이 직접 Disable되어 OFF되고, 동시에 Discharge 회로도 ON되어 VOUT3을 설정한 시간에 그라운드 레벨 근처까지 낮아진다.

지금까지 전원 시퀀스 사양의 전원 투입 시의 시퀀스 동작과 전원 차단 시의 시퀀스 동작에 대해 알아 보았다. 본 고에서 사용된 부품의 사양에 대해서는 로옴코리아로 문의 바란다.

범용 전원 IC로 전원 시퀀스를 실현하는 회로

조회수 876회 / 로옴코리아

열 설계와 기술 트렌드의 변화

조회수 1300회 / 로옴코리아

평활 후의 DC/DC 안정화 방식

조회수 1081회 / 로옴코리아

DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃 부품 배치 방법(2)

조회수 2460회 / ROHM

DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃의 대원칙(1)

조회수 1652회 / ROHM

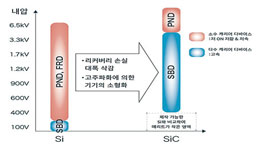

SiC 파워 디바이스란?

조회수 5312회 / ROHM

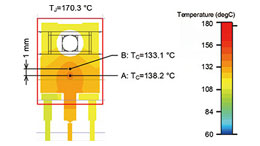

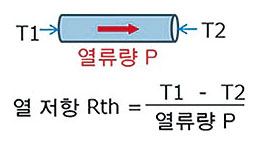

열 저항 RthJC의 측정 방법과 사용법

조회수 3335회 / 로옴코리아

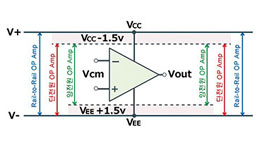

연산증폭기와 비교기란?

조회수 4448회 / ROHM

열 저항과 방열의 기본

조회수 11329회 / ROHM

PDF 다운로드

회원 정보 수정