레귤레이트 된 48V를 12V로 첫 번째 단의 효율을 대폭 향상시키는 결합 인덕터 활용법

글/알렉산드르 이크리아니코프(Alexandr Ikriannikov) 펠로우, 라즐로 립세이(Laszlo Lipcsei) 디렉터, 아나로그디바이스(Analog Devices, Inc.)

48V 전압 분배는 데이터센터와 통신 애플리케이션에서 많이 이용되며, 48V에서 중간 전압 레일로 스텝다운하기 위한 다양한 솔루션들이 제공되고 있다. 가장 간단한 방법으로는 벅 토폴로지를 들 수 있는데, 이 방법은 높은 성능을 제공할 수 있지만 전력 밀도가 부족한 경우가 많다. 결합 인덕터(coupled inductor, CL)로 다상 벅을 업그레이드하면 대대적인 성능 이점을 유지함과 동시에, 극적인 전력 밀도 향상을 달성할 수 있다. 다상 결합 인덕터는 권선 간 역 커플링이 생성되므로 각각의 위상 전류에서 전류 리플 제거가 가능하다. 이러한 이점은 효율이나 크기 축소 및 전력 밀도 향상 등과 맞바꿀 수 있다. 이 글에서는 부품의 크기와 무게를 4배 줄여 업계 표준 크기인 브릭의 1/8에서 98% 이상의 피크 효율로 1.2kW 솔루션을 구현하는 예를 살펴본다. 또한 결합 인덕터의 성능 지수(FOM)를 기반으로 48V 토폴로지를 최적화하는 방법도 중점적으로 다룬다. 이 글은 DC-DC 변환 분야를 담당하는 엔지니어에게 도움이 되는 정보를 제공할 것이다.

머리말

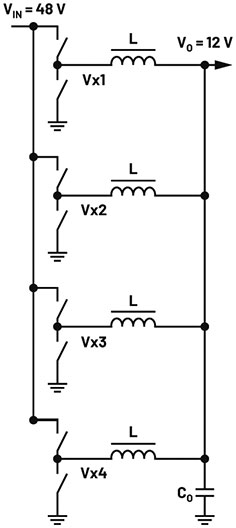

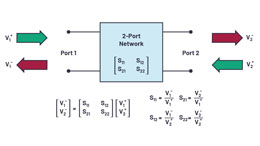

48V 분배 레일은 일반적으로 중간 전압인 12V 또는 그 이하로 스텝다운되며, 그런 다음 서로 다른 로컬 POL(point-of-load) 레귤레이터가 다양한 부하에 다양한 전압을 직접 제공한다. 48V ~ 12V 스텝다운 전압 레귤레이터를 위해 고려할 첫 번째 선택 중 하나는 다상 벅 컨버터이다(그림 1). 이 컨버터는 레귤레이트된 VO 및 빠른 과도 응답을 제공하는 솔루션으로, 구현하기 쉽고 비용도 저렴하다. 수백 와트에서 1kW 이상 전력 범위의 경우 4개의 병렬 위상을 고려할 수 있다. 하지만 주로 고효율이 우선시되므로, 12V 또는 더 낮은 5V 입력의 저전압 애플리케이션에 비해 48V와 같은 컨버터는 스위칭 손실을 낮게 유지하기 위해 스위칭 주파수가 비교적 낮은 경우가 많다. 이미 상당한 전압이 비교적 오랜 시간 인가되므로, 전압(V) x 시간(초)이라는 측면에서 자기 부품은 두 배의 손상을 입는다. 그 결과, 48V용 자기 부품은 저전압 애플리케이션에 비해 크게 증가한 전압 × 시간을 견딜 수 있도록 여러 번 감은 권선을 사용하기 때문에 대체로 부피가 큰 편이다. 48V 벅 컨버터에서도 여전히 고효율을 달성할 수 있지만, 일반적으로 전체 크기가 크며 인덕터가 대부분의 부피를 차지한다.

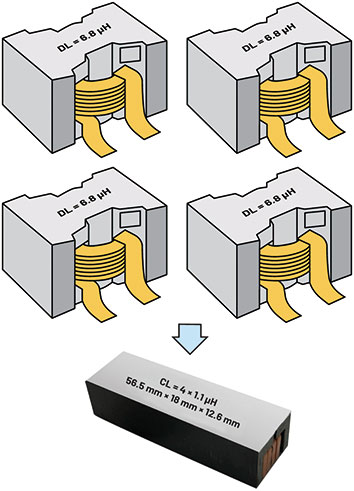

기본 48V에서 12V 전환의 1kW 이하 벅 컨버터는 6.8μH 디스크리트 인덕터들로 구성된 4개 위상을 가지며, 200kHz에서 스위칭한다. 이들 4개의 인덕터는 가장 크고 높이가 가장 높은 부품이며, 솔루션 부피의 대부분을 차지한다. 이 글의 목적은 이러한 초기 설계에서 달성된 높은 효율을 유지 또는 향상시키면서 자기 부품의 크기를 크게 줄이는 데 있다.

기존 벅의 각 위상에서 전류 리플은 공식 1로 구할 수 있다. 여기서 듀티 사이클은 D = VO/VIN이고, VO는 출력 전압, VIN은 입력 전압, L은 인덕턴스 값이며, FS는 스위칭 주파수이다.

![]()

[그림 1] 디스크리트 인덕터들로 구성된 4상 벅 컨버터

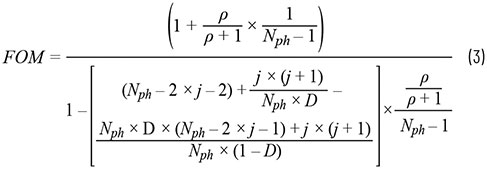

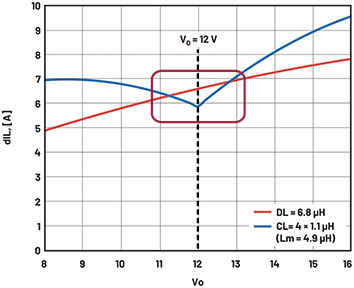

디스크리트 인덕터(DL)를 누설 인덕턴스 Lk와 상호 인덕턴스 Lm을 갖는 결합 인덕터로 대체하면[1~7] 결합 인덕터(coupled inductor, CL)의 전류 리플은 공식 2로 나타낼 수 있다[6]. FOM은 공식 3과 같이 나타낼 수 있으며, 여기서 Nph는 결합된 위상의 수이고, ρ는 결합 계수이며(공식 4), j는 실행 지수로 단지 듀티 사이클의 적용 가능한 간격을 정의한다(공식 5).

![]()

![]()

![]()

CL 고려사항

첫 번째 고려 사항은 결합 계수 Lm/Lk의 실질적으로 합리적인 여러 값을 알아보기 위해 Nph = 4에 대한 FOM을 그래프로 나타내는 것이다(그림 2). 빨간색 곡선 Lm/Lk = 0은 디스크리트 인덕터에 대한 FOM = 1 기준선을 나타낸다. 누설이 매우 낮은 노치 CL(notch CL, NCL) 구조는 일반적으로 매우 높은 Lm/Lk을 달성해 높은 값의 FOM을 얻을 수 있음을 알 수 있다[8,9]. 그러나 듀티 사이클은 이상적으로 첫 번째 노치 D = 12V/48V = 0.25에 있으므로, VIN과 VO에 대한 일부 범위를 고려할 필요가 있다. 경우에 따라, 공칭 VIN은 48V 또는 54V에 약간의 허용오차를 더한 값일 수 있으며, VO는 12V가 아닌 다른 값으로 조정될 수 있다. 만약 듀티 사이클이 일부 범위에서 D = 0.25를 중심으로 달라질 경우, 전류 리플을 억제하려면 여전히 높은 FOM 값을 갖는 NCL 대신 누설이 큰 일반적인 CL 설계를 선택한다. Lm/Lk > 4라고 가정하면, CL의 인덕턴스 값을 줄임으로써 그림 2의 FOM에서는 DL 기준선과 비교할 때 약 6배의 이점을 누릴 수 있는 것으로 고려할 수 있다. 에너지 저장량을 줄이는 것은 자기 부품의 크기를 결정하는 데 직접적인 영향을 미친다. 따라서 DL = 6.8μH 값을 CL = 1.1μH로 줄이면 크기 감소에 도움이 된다.

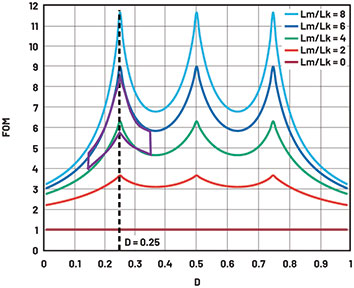

[그림 3] VO의 함수로서 VIN = 48V, Fs = 200kHz에서 DL = 6.8μH, CL = 4 × 1.1μH의 전류 리플. 관심 영역이 강조 표시되었다.

해당하는 전류 리플은 그림 3에 표시되어 있으며, VIN = 48V 및 FS = 200kHz 조건에서 기준선 설계 DL = 6.8μH와 제안된 4상 CL = 4 × 1.1μH(Lm = 4.9μH)를 비교하였다. 관심 영역에서 CL의 전류 리플은 DL의 전류 리플과 비슷하거나 작다. 이는 모든 회로 파형의 rms가 유사하며, 따라서 전도 손실도 유사하다는 것을 의미한다. 동일한 FS에서 동일한 리플 역시 동일한 스위칭 손실, 게이트 드라이브 손실 등을 의미하며, 이는 두 솔루션 간의 효율이 매우 유사하다는 것을 뜻한다(유일한 차이로서, DL 및 CL 인덕터 손실의 기여도가 비슷하다고 가정).

그림 4는 설계된 CL = 4 × 1.1μH를 보여주며, 이 인덕터는 4개의 DL = 6.8μH 인덕터를 대체한다[5]. 각 DL은 크기가 28mm × 28mm × 16mm이며, 서로 0.5mm 간격으로 배치된다고 가정할 때 56.5mm × 18mm × 12.6mm 크기의 4상 CL은 자기 부품의 크기를 4배 더 작게 만든다. 그림 5는 완전한 1.2kW 48V ~ 12V 레귤레이트 솔루션을 보여주는데, 단일 PCB 측 부품은 브릭의 1/4선 안쪽에 있다. CL 크기와 풋프린트는 업계 표준 브릭 크기의 1/4 안에 2개의 CL 부품이 들어가도록 의도적으로 설계되었다. PCB 하단에 모든 1mm 이하의 부품들(FET, 컨트롤러 IC, 세라믹 커패시터 등)을 배치하면 1.2kW 솔루션에서 브릭 크기의 1/8이 가능하다.

[그림 4] 4개의 DL = 6.8μH 인덕터(위쪽)를 CL = 4 × 1.1μH(아래쪽)으로 대체하면 크기가 4배 감소한다.

[그림 5] 48V - 12V 레귤레이트된 첫 번째 단. 부품들은 브릭의 1/4 아웃라인 안쪽 상단 PCB 측에 배치된다. 모든 1mm 이하의 부품들은 하단에 배치: 브릭 크기의 1/8

성능 이득

DL = 6.8μH 인덕터를 CL = 4 × 1.1μH로 변경했을 때 인덕터의 전류 슬루율 제한도 6배 향상되었으며, 이는 과도 응답 향상에 도움이 된다. 게다가 전체 자기 부품 크기가 4배 더 축소됐지만, 인덕터 포화 정격은 100℃에서 약 2배 향상되었다.

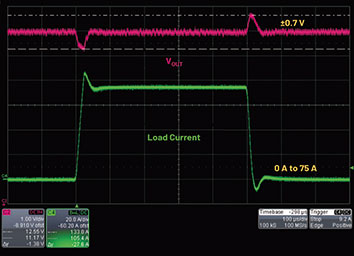

VO = 12V 출력에서 제안된 VIN = 48V 솔루션의 과도 응답 성능은 그림 6에 나와 있다. 예상한 것처럼, 피드백은 변화하는 부하 전류에 대해 출력 전압을 사전 설정된 값으로 조절하고, 입력 전압의 모든 변화도 보상한다.

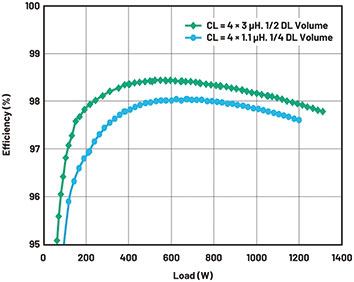

[그림 8] 결합 인덕터(CL)를 사용하는 제안된 48V - 12V 솔루션의 효율과 크기의 절충

결론

48V에서 12V로 전환 솔루션은 결합 인덕터의 이점을 활용하여 전체 자기 부품 크기를 기본 디스크리트 인덕터보다 4배 줄임으로써 업계 표준 브릭 크기의 1/8 폼팩터에서 1.2kW를 달성한다. 이 같은 자기 부품의 크기 4배 축소는 우수한 효율 성능을 유지하면서 과도 응답에서 인덕터 전류 슬루율은 6배, 인덕터 Isat 정격은 2배 높이면서 달성된 것이다.

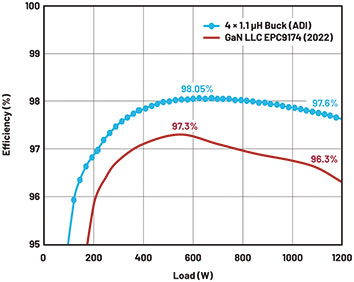

동일한 폼팩터의 산업용 첨단 48V ~ 12V 솔루션과 비교하면 최대 전력에서 약 1.6배의 손실 감소를 달성한다. 또한 자기 부품 크기의 축소폭을 줄이면 효율을 추가로 향상시킬 수 있는 것도 보여주었다.

제안된 솔루션은 완벽하게 제어되고, 고객의 메인보드에 직접 배치되며, 표준 실리콘 FET를 사용하여 비용을 더욱 최적화한다. 이는 많은 레이어, 민감한 레이아웃, 임베디드 매트릭스 트랜스포머의 전문적인 PCB를 탑재한 개별적인 모듈로 제작되는 전체 GaN FET의 레귤레이트되지 않은 4:1 LLC와 비교된다.

전반적인 성능 이득은 결합 인덕터에 대한 ADI의 특허 받은 IP의 이점을 보여주며, ADI는 DC-DC 애플리케이션 분야의 많은 고객들에게 이를 제공하고 있다.

[참고문헌]

[1] Aaron M. Schultz and Charles R. Sullivan. “Voltage Converter with Coupled Inductive Windings, and Associated Methods.” U.S. Patent 6,362,986, March 2001.

[2] Jieli Li. “Coupled Inductor Design in DC-DC Converters.” MS Thesis, 2001, Dartmouth College.

[3] Pit-Leong Wong, Peng Xu , P. Yang, and F. C. Lee. “Performance Improvements of Interleaving VRMs with Coupling Inductors.” IEEE Transactions on Power Electronics, Vol. 16, No. 4, July 2001.

[4] Yan Dong. “Investigation of Multiphase Coupled-Inductor Buck Converters in Point-of-Load Applications.” Ph.D. Thesis, 2009, Virginia Polytechnic Institute and State University, USA.

[5] Alexandr Ikriannikov. “Coupled Inductor with Improved Leakage Inductance Control.” U.S. Patent 8,102.233, January 2009.

[6] Alexandr Ikriannikov and Di Yao. “Addressing Core Loss in Coupled Inductors.” Electronic Design News, December 2016,

[7] Alexandr Ikriannikov. “Coupled Inductor Basics and Benefits.” Analog Devices, Inc., 2021.

[8] Alexandr Ikriannikov. “Evolution and Comparison of Magnetics for the Multiphase DC-DC Applications.” IEEE Applied Power Electronics Conference, March 2023.

[9] Alexandr Ikriannikov and Di Yao. “Converters with Multiphase Magnetics: TLVR vs CL and the Novel Optimized Structure.” PCIM Europe, May 2023.

[10] “EPC9174-Evaluation Board.” Efficient Power Conversion Corporation.

레귤레이트 된 48V를 12V로 첫 번째 단의 효율을 대폭 향상시키는 결합 ...

조회수 446회 / Alexandr Ikriannikov 외 1인

LTspice를 사용하여 복잡한 회로에 대한 통계학적 허용오차 분석 모델링...

조회수 1831회 / Steve Knudtsen

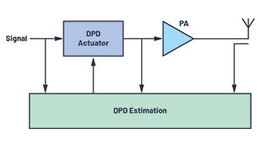

실제 유용한 디지털 전치왜곡 솔루션 설계 방법

조회수 1159회 / Steve Summerfield 외 1인

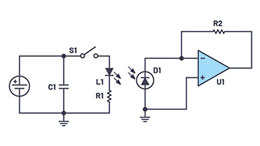

보다 우수한 성능의 산소포화도 측정기 설계 방법

조회수 8148회 / Robert Finnerty

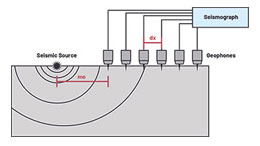

지진 탐사 및 에너지 탐사 애플리케이션용 저잡음 저전력 DAQ 솔루션

조회수 1212회 / David Guo

RF 신호 체인의 주요 특성 및 성능 지표

조회수 4679회 / Anton Patyuchenko

PCB 공간 제약 문제 해결하는 모놀리식 벅-부스트 컨버터 및 LED 드라이버

조회수 1662회 / Kyle Lawrence

퍼시비어런스 화성 탐사선과 극한환경을 위한 고신뢰성 기술

조회수 1352회 / Analog Devices

아나로그디바이스(ADI), 반도체 업계 ESG 경영 선도한다

조회수 1255회 / ADI

PDF 다운로드

회원 정보 수정