정밀 광대역폭 신호 체인용 프로그래머블 이득 계측 증폭기(PGIA) 설계 방법

글/마이틸 파쉬쉬가(Maithil Pachchigar), 시스템 애플리케이션 엔지니어

존 니코 가를리토스(John Neeko Garlitos), 제품 애플리케이션 엔지니어, 아나로그디바이스

이 글은 광대역폭 프로그래머블 이득 계측 증폭기(PGIA)를 설계하는 하드웨어 엔지니어를 돕기 위한 것으로서, 부품 선택과 성능 평가에서부터 하드웨어 설계 시간을 단축하고 반복 작업을 줄일 수 있는 방법에 이르기까지 제반 사항을 설명한다. 이 글에서 설명하는 PGIA 아키텍처는 고정밀 SAR 아키텍처 기반 신호 체인을 위한 것이다.

머리말

정밀 데이터 수집 서브시스템은 측정과 보호, 컨디셔닝과 수집, 또는 합성과 구동을 위한 여러 신호 체인 블록들로 이루어진다. 이러한 데이터 수집 신호 체인을 위해서는 다양한 유형의 센서에 곧바로 인터페이스 할 수 있도록 통상적으로 높은 입력 임피던스가 요구된다. 이러한 경우, 다양한 공통 모드 전압을 가진 유니폴라와 바이폴라, 싱글 엔디드 또는 차동 같이 다양한 입력 신호 수준에 따라서 회로가 적응할 수 있도록 하기 위해 프로그래머블 이득이 필요하다.

전통적으로 대다수의 PGIA는 완전 차동 고정밀 SAR 아키텍처 기반 신호 체인을 최대 속도로 직접 구동하지 못하는 싱글 엔디드 출력으로 구성되며, 최소한 하나의 신호 컨디셔닝 또는 드라이버 스테이지를 필요로 할 수 있다. 오늘날에는 아날로그 회로를 개발하고 기능을 검증하는 데 투입할 수 있는 시간이 촉박하고 연구개발 예산과 출시 일정도 넉넉하게 주어지지 않는다.

또 하드웨어 개발 자원을 사용할 때 반복 작업을 줄이도록 하는 압박이 심해지고 있다. 이 글에서는 디스크리트 광대역폭 완전 차동 PGIA를 설계할 때의 여러 측면을 살펴보고, 고속 신호 체인 µModule® 데이터 수집 솔루션을 구동할 때의 성능에 대해서 설명한다.

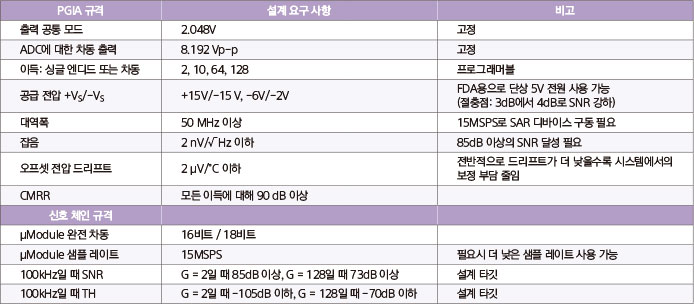

PGIA 설계 규격

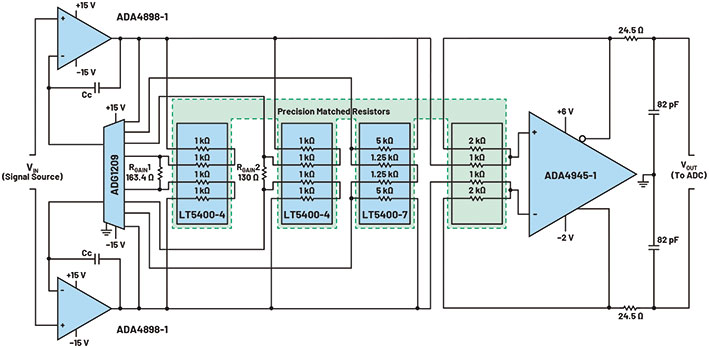

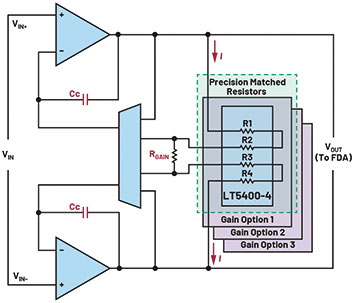

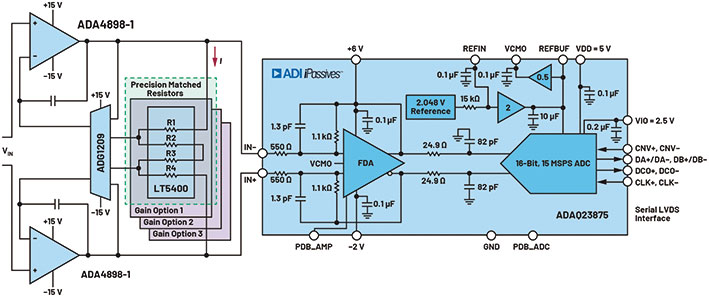

그림 1은 이 디스크리트 광대역폭 완전 차동 PGIA의 블록 다이어그램을 보여준다. 표 1은 이 PGIA 회로의 주요 규격을 나타낸다.

• ADA4898-1 저잡음 고속 증폭기

• LT5400 쿼드 저항 네트워크. PGIA 이득을 설정하기 위한 이득 및 피드백 저항으로 사용

• ADG1209 낮은 커패시턴스의 iCMOS™ 멀티플렉서. PGIA 이득을 제어

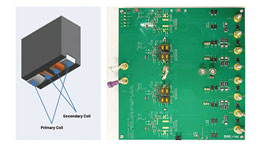

• ADA4945-1 광대역폭 완전 차동 증폭기(FDA)

이 광대역폭 PGIA 회로를 위해 이들 디스크리트 부품을 선택한 것은 표 1의 PGIA 규격을 충족하고, ADAQ23875와 ADAQ23878 같은 완전 차동 고속 신호 체인 µModule 데이터 수집 솔루션과 LTC2387-16/LTC2387-18 같은 ADC를 구동할 때 최적의 AC 및 DC 성능을 달성하기 위해서다.

설계 팁과 부품 선택

고속 SAR 아키텍처 기반 신호 체인 µModule 솔루션을 구동하고 최적의 성능을 달성하는 이 광대역폭 디스크리트 PGIA 솔루션의 능력은 증폭기와 FDA의 핵심 규격(대역폭, 슬루율, 잡음, 왜곡 등)에 따라 좌우된다. ADA4898-1과 ADA4945-1을 선택한 것은 이들 제품의 이득 대역폭(GBW) 곱이 이 신호 체인의 전반적인 대역폭 요구와 잘 맞기 때문이다. ADA4945-1(FDA)은 LTC2387-16/LTC2387-18 같은 ADC를 구동할 때만 필요하다. 아래에서 살펴보듯이, PGIA 이득을 설정하는 기준은 증폭기, 피드백, 저항, 멀티플렉서 선택에 따라 달라진다.

PGIA 이득 설정

*이득 및 피드백 저항 선택

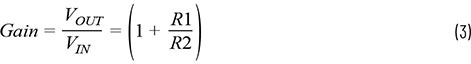

증폭기의 이득 및 피드백 저항은 정밀하게 매칭해야 한다. LT5400 쿼드 저항 네트워크는 폭 넓은 온도 범위에 걸쳐서 0.2ppm/℃의 매칭 드리프트와 0.01%의 저항 매칭을 특징으로 하며, 저항들을 개별적으로 매칭할 때보다 더 우수한 CMRR을 달성한다. 최적의 CMRR 성능을 달성하기 위해서는 FDA 주변의 이득 저항들도 정밀하게 매칭시켜야 한다. LT5400 저항 네트워크를 사용하면 증폭기 이득을 설정할 수 있다. 공식 1 ~ 3은 이득을 계산하는 방법을 보여준다:

![]()

![]()

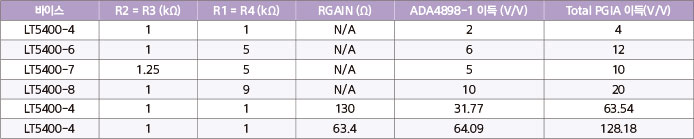

LT5400을 사용해서 R1 = R4, R2 = R3으로 설정하면 이득은 다음과 같다:

증폭기들과 FDA(2의 고정 이득)의 이득을 합치면 표 2와 같이 이 PGIA의 총 이득을 구성할 수 있다.

표 2에서 보듯이 LT5400 시리즈는 다양한 저항 옵션을 사용할 수 있다. 증폭기들을 단위 이득 구성으로 사용하면 ADG1209 멀티플렉서를 바이패스할 수 있으므로, 이 경우에는 총 PGIA 이득이 2로 설정될 것이다.

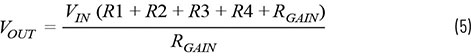

RGAIN 값 계산은 공식 4 ~ 8을 활용하면 된다:

![]()

![]()

그러므로 원하는 이득을 위한 RGAIN 값은 다음과 같이 구할 수 있다:

![]()

*멀티플렉서 선택

멀티플렉서를 사용해서 이 PGIA 회로의 다양한 이득을 제어할 수 있다. 이 디스크리트 광대역폭 PGIA 설계에 사용하기 위한 멀티플렉서를 선택할 때는 온 저항(RON), 온 커패시턴스(CON), 오프 커패시턴스(COFF) 같은 멀티플렉서 파라미터들을 고려해야 한다. 이 광대역폭 PGIA 설계에는 ADG1209 멀티플렉서를 권장할 만하다. 증폭기들의 피드백 경로에 보상 커패시터(CC)를 추가해서 이득 피킹을 최소화하고 멀티플렉서 온/오프 커패시턴스의 영향을 낮출 수 있다.

CC가 RON, 피드백, 이득 저항과 함께 극점을 형성하고, 이는 피드백 루프 이득에서 커패시티브 기생 영점의 영향을 보상할 것이다. CC 값은 원하는 폐쇄 루프 응답을 달성하도록 최적화해야 한다. ADA4898-1 주변에 더 높은 피드백 저항 값을 사용하면 높은 입력 커패시턴스에 의해서 폐쇄 루프 이득에 더 높은 피킹(peaking)이 나타날 것이다.

이를 피하려면 ADA4898-1 주변에 높은 피드백 저항 값과 함께 피드백 커패시터를 병렬로 사용해야 한다. 여기서는 그림 2에서 볼 수 있는 것처럼 ADA4898-1 데이터 시트에서 권장하고 있듯이 2.7pF의 최적화된 CC 값을 선택하고 있다. 더 작은 CC 값을 사용하면 이득 피킹을 최소화할 수 있으며, CC 값이 너무 크면 폐쇄 루프 이득의 이득 평탄도에 영향을 미칠 것이다.

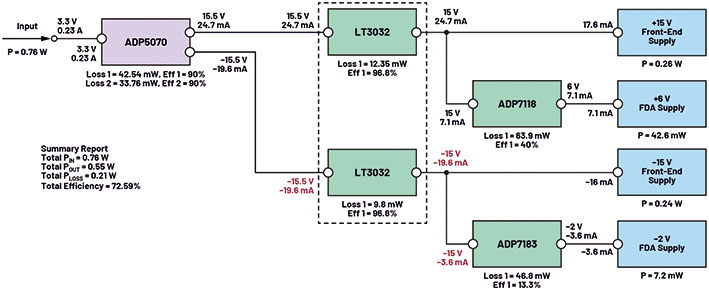

PGIA 전원공급장치

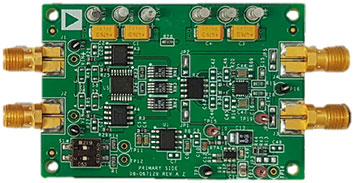

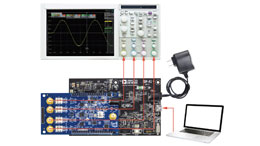

그림 3은 이 디스크리트 광대역폭 PGIA의 성능을 평가하기 위해 사용되는 보드의 모습이다.

PGIA 성능

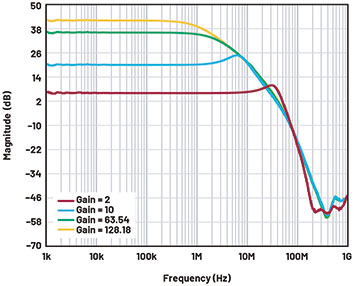

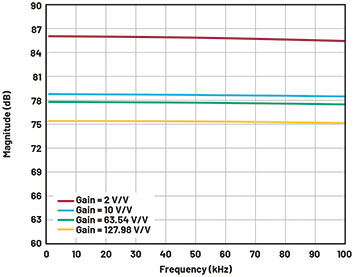

*대역폭

그림 5는 서로 다른 이득 설정에 대한 폐쇄 루프 이득 대 주파수의 관계를 보여준다. PGIA 이득이 2에서 128로 높아질수록 대역폭은 감소하고 잡음 관련 출력(RTO)은 증가한다. 따라서 신호대 잡음비(SNR)는 낮아진다.

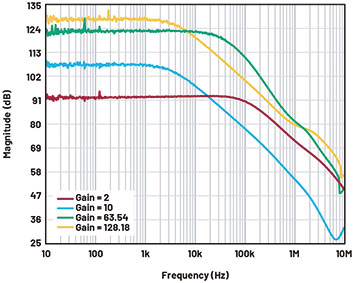

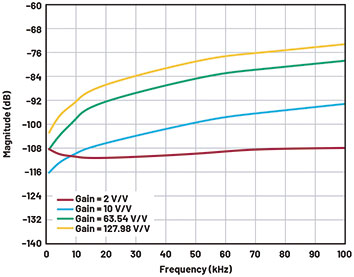

*CMRR

그림 6은 서로 다른 PGIA 이득 설정에 대한 CMRR 대 주파수의 관계를 그래프로 나타낸 것이다.

[그림 6] CMRR 대 주파수의 관계

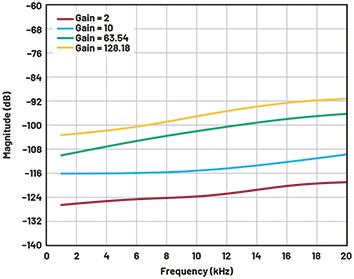

*왜곡

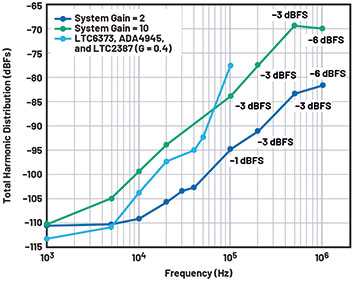

Audio Precision®(APX555) 신호 분석기를 사용해서 이 PGIA 보드(그림 3)의 왜곡 성능을 테스트했다. 출력은 8.192Vp-p로 설정하고, 다양한 이득 설정에 대해 다양한 입력 전압을 인가했다. 그림 7은 이 디스크리트 광대역폭 PGIA의 총 고조파 왜곡(THD) 대 주파수 성능을 보여준다.

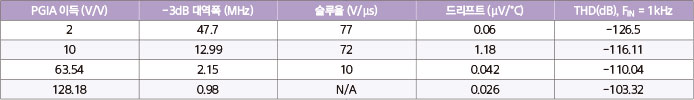

*주요 성능 요약

표 3은 이 디스크리트 PGIA 보드를 사용하여 벤치 상에서 측정한 대역폭, 슬루율, 드리프트, 왜곡 같은 주요 PGIA 성능을 요약해서 정리한 것이다.

[표 3] 독립형 PGIA의 주요 성능

PGIA로 신호 체인 µModule 솔루션 구동하기

그림 8에서는 LT5400 쿼드 정밀 매칭 저항 네트워크를 통한 이득을 멀티플렉서에서 선택하고 이를 2개의 ADA4898-1 저잡음 고속 증폭기에 적용한 뒤 15MSPS로 동작하는 ADAQ23875 신호 체인 µModule을 구동하는 것을 보여준다. ADAQ23875는 내부에 완전 차동 증폭기를 포함하고 있으므로 광대역폭 디스크리트 PGIA 보드(그림 3)의 FDA 블록은 바이패스 되어야 한다. Audio Precision (APx555) 신호 소스를 사용해서 SNR과 THD를 측정했으며, 이 때 입력 진폭은 약 -0.5dBFS로 설정했다.

[그림 8] ADAQ23875를 구동하는 디스크리트 PGIA의 간략한 신호 체인

전체적인 신호 체인 성능

*잡음

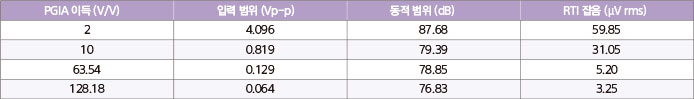

표 4는 이 전체적인 신호 체인(그림 8)의 특정한 입력 범위 또는 이득 설정에 대한 동적 범위와 RTI 잡음을 보여준다.

ADAQ23878의 정밀한 성능에다 높은 샘플링 레이트를 결합함으로써, 잡음을 낮출 뿐만 아니라 오버샘플링을 통해서 극히 낮은 rms 잡음을 달성하고 넓은 대역폭에 걸쳐서 낮은 수준의 신호를 검출할 수 있다. 다시 말해, 15MSPS의 샘플링 레이트 성능은 에일리어싱 방지 필터 요구량을 크게 완화하고 고속 트랜션트와 낮은 수준의 신호를 디지털화 할 때 대역폭을 극대화한다.

오버샘플링은 나이퀴스트 조건을 충족하기 위해 필요한 신호 대역폭의 두 배보다 훨씬 더 빠르게 샘플링하는 것을 말한다. 예를 들어서 ADAQ23875를 4의 계수로 오버샘플링하면 분해능에 한 비트를 추가하거나 동적 범위를 6dB 늘릴 수 있다. 즉, 오버샘플링을 통한 이 같은 동적 범위(DR) 향상은 다음과 같이 정의할 수 있다: ΔDR = 10 × log10(OSR). 단위는 dB이다.

ADAQ23875의 정격 동적 범위는 입력을 접지에 단락시키고 4.096Vref일 때 15MSPS에서 91dB이다. 예를 들어서 ADAQ23875를 256x 계수로 오버샘플링하면 이는 다양한 이득 옵션에 대해 29.297kHz의 신호 대역폭과 111dB에 가까운 동적 범위에 해당된다. 그러므로 µV 대의 낮은 수준의 신호를 정밀하게 검출할 수 있다. 원하는 측정에 적합하도록 잡음과 대역폭을 절충하면서 추가적인 오버샘플링을 적용할 수 있다.

*왜곡

그림 10과 그림 11은 이 디스크리트 PGIA를 사용해서 ADAQ23875를 구동할 때 전체적인 신호 체인의 THD 성능을 보여준다(100kHz까지와 100kHz ~ 1MHz). PGIA 이득과 입력 신호 주파수가 높아질수록 THD가 서서히 저하된다는 것을 알 수 있다. 이것은 ADA4898-1의 대역폭과 슬루율이 저하되기 때문이다. 그림 11은 이 PGIA를 사용해서 ADAQ23875를 구동할 때와 LTC6373과 ADA4945-1 조합을 사용해서 LTC2387-16을 15MSPS로 구동할 때의 THD 성능을 비교해서 보여준다.

[그림 10] PGIA를 사용해서 ADAQ23875를 구동할 때 THD 대 주파수의 관계

[그림 11] PGIA를 사용해서 ADAQ23875를 구동할 때와 LTC6373 + ADA4945-1 + LTC2387-16 조합을 사용할 때의 THD 성능 비교 그래프

*적분 선형성(INL)과 미분 선형성(DNL)

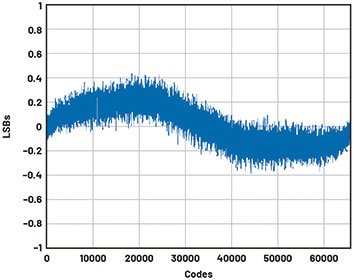

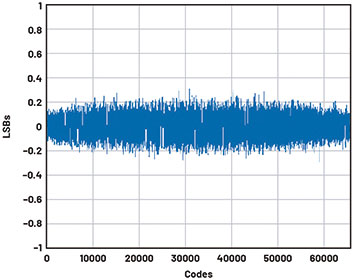

신호 체인의 전반적인 DC 정확도 역시 중요하다. 그림 12와 그림 13은 PGIA 이득이 2일 때 통상의 INL과 DNL 성능을 보여준다. 그 외의 모든 이득 설정에 대해, INL과 DNL은 통상 ±0.5LSB 이내이다.

[그림 12] ADAQ23875를 구동할 때 PGIA(G = 2)의 INL 플롯

[그림 13] ADAQ23875를 구동할 때 PGIA(G = 2)의 DNL 플롯

맺음말

이 글에서는 ADA4898-1 증폭기, ADG1209 멀티플렉서, LT5400 정밀 매칭 저항 네트워크를 사용한 디스크리트 광대역폭 PGIA 설계 방법에 관해 살펴보았다. 16비트 15MSPS ADAQ23875 신호 체인 µModule 솔루션을 구동하기 위해 수십 mV부터 10V 가까이 이르는 싱글 엔디드/차동 신호를 높은 정확도로 측정할 수 있다는 것을 확인했다. 이 전체적인 신호 체인은 모놀리식 PGIA를 사용해서 달성할 수 있는 것보다 전반적으로 더 정밀한 성능을 달성한다. 이 광대역폭 신호 체인은 자동화 테스트 장비, 전원 모니터링, 분석기 같은 테스트 장비에 사용하기에 적합하다.

[참고문헌]

Pachchigar, Maithil. “Increase Dynamic Range of SAR ADCs Using Oversampling.” Analog Devices, Inc., June 2015.

“CN-0560: High Precision, Wide Bandwidth Current Measurement Signal Chain.” Analog Devices, Inc., June 2022.

단일 IC로 구현한 포괄적 시스템 보호의 통합 솔루션

조회수 344회 / Anthony Huynh

지속가능한 모빌리티를 가속화하는 진보한 전동화 기술

조회수 420회 / Patrick Morgan

5G 및 차세대 통신 장비를 위한 향상된 -48VDC 전원 공급장치 설계

조회수 401회 / Hamed M. Sanogo

오픈소스 평가 플랫폼을 활용한 초음파 송신 서브시스템 프로토타이핑 방법

조회수 635회 / Sunshine Grace Cabatan 외 1인

밀리미터파 구현에 새로운 DPD 접근법이 필요한 이유와 가치 정량화 방법

조회수 865회 / Hossein Yektaii 외 2인

극히 빠른 동적 응답을 달성하는 유연한 TLVR 구조의 트랜스포머 기반 ...

조회수 758회 / Xingxuan Huang 외 2인

µModule 레귤레이터의 진화

조회수 636회 / Analog Devices

아나로그디바이스 양성환 전무 인터뷰, 고객의 성공에 기여하는 ADI 파...

조회수 951회 / Analog Devices

차세대 밀리미터파 스캐너를 가능케 하는 에지 프로세싱

조회수 829회 / Eamon Nash

PDF 다운로드

회원 정보 수정