차세대 밀리미터파 스캐너를 가능케 하는 에지 프로세싱

글/에이먼 내쉬(Eamon Nash) 애플리케이션 엔지니어링 디렉터, 아나로그디바이스

머리말

밀리미터파(mmWave) 이미징이 공항, 공공 건물, 경기장 등의 보안 검사 시스템에서 중요한 역할을 하고 있다. 밀리미터파 스캐너는 금속과 비금속 위험물을 모두 탐지 및 식별할 수 있다는 점에서 기존의 금속 탐지기보다 우월하다. 이 글에서는 밀리미터파 이미징 하드웨어가 어떻게 작동하는지 설명하고, 에지 프로세싱을 활용해 대규모의 데이터를 처리함으로써 워크스루(walkthrough) 보안 검사 시스템을 구현할 수 있게 하는 칩셋을 소개한다.

밀리미터파 이미징의 작동 방식

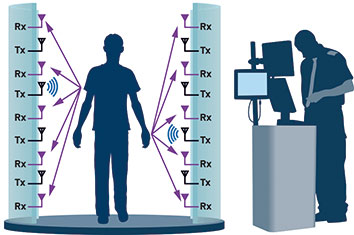

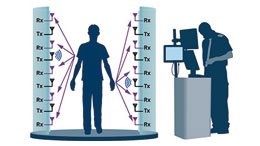

그림 1은 밀리미터파 스캐너가 어떻게 작동하는지 보여준다. 이 시스템은 일련의 송신기와 수신기가 공간 안에 산발적으로 분포된 안테나 어레이와 연결되어 이루어진다. 이 시스템은 리턴 손실, 즉 S11을 측정하는 네트워크 분석기와 비슷하다고 할 수 있다. 특정 시점에 어레이 중의 한 안테나가 어떤 한 주파수로 저전력 신호를 송신하면, 이 신호가 표적에 부딪혀서 반사됨으로써 후방산란(backscatter)을 일으킨다(이 그림에서는 표적의 한 지점으로부터만 반사가 이루어지는 것으로 표현되어 있지만, 실제로 송신 신호는 전방향성이다. 따라서 표적의 여러 지점들로부터 반사가 일어난다).

RF 신호의 침투 깊이와 반사 특성은 주파수에 따라서 달라지므로, 위에서 설명한 스캔을 넓은 대역에 걸쳐서 여러 주파수를 사용해서 반복한다. 그 결과 얻어진 벡터 행렬이 다차원 어레이를 형성하고(주파수 및 공간적 위치에 대해서), 이를 사용해 이미지를 생성함으로써 혹시나 옷 속에 숨기고 있는 금속 및 비금속 물체를 찾아낼 수 있다.

이러한 스캔 작업에 요구되는 하드웨어는 다채널이어야 하며, 넓은 동작 주파수 범위를 가져야 한다. 10GHz ~ 40GHz 주파수 범위이면 통상적인 보안 검사 상황(옷, 배낭, 무기, 폭발물)에서 물체들을 식별하는 데 충분하다. 채널 수가 많을수록 더 높은 분해능이 가능하므로, 더 작은 물체를 식별할 수 있다. 일례로 공항 스캐너는 면도날을 탐지하는 것이 중요한 데 반해, 공공 건물이나 경기장에서는 무기나 폭발물 같이 더 큰 물체를 탐지하는 데 좀 더 초점이 맞춰진다. 이러한 애플리케이션에서는 대체로 더 적은 수의 채널을 사용한다.

이들 시스템에서 또 다른 중요한 요소는 빠른 스위칭 시간이다. 스위칭 시간이 빠르면 검사를 받는 사람이 짧은 시간 동안만(통상적으로 1초 미만) 자세를 취하면 되는 검사 시스템을 구현할 수 있다. 차세대 워크스루 시스템은 사람이 멈춰서 자세를 취할 필요가 없도록 하기 위해서 더 빠른 스위칭 시간을 요구한다.

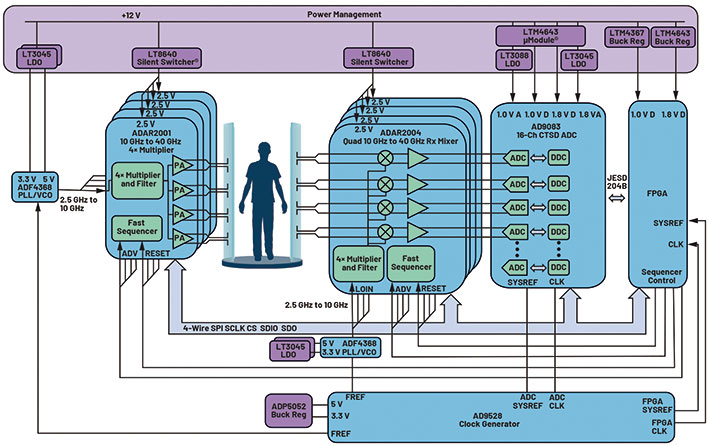

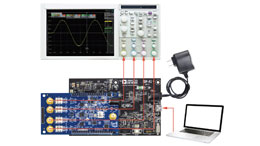

그림 2는 아나로그디바이스(Analog Devices)의 밀리미터파 이미징 칩셋을 사용해서 완전한 밀리미터파 스캐너를 구현할 수 있다는 것을 보여준다. 송신기(ADAR2001) 어레이는 중앙의 민첩한 주파수 소스를 사용해서 구동된다. 수신기(ADAR2004) 어레이는 반사된 신호를 검출하고 이를 낮은 중간 주파수로 하향 변환한다. 그런 다음 다채널 연속-시간 시그마 델타(CTSD) 컨버터(AD9083)가 IF 샘플링을 한다.

그러면 이들 각각의 디바이스에 대해서, 그리고 이들 디바이스의 기능들이 어떻게 전반적인 시스템 성능을 최적화하는지 알아보자.

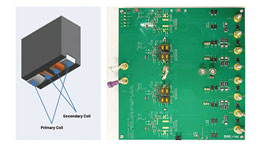

송신기

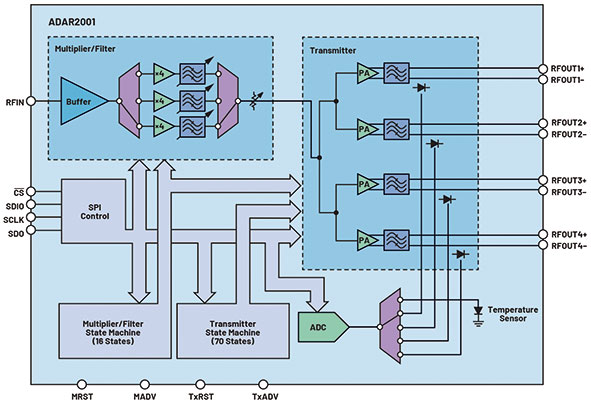

앞서도 언급했듯이, 송신기는 공간에 산발적으로 분포된 안테나들을 위한 여러 채널들로 이루어지며, 각각의 송신기는 전력 증폭기에 의해 구동된다. ADAR2001은 4채널 송신기로서, 안테나들에 직접 연결되고 출력 주파수 범위는 10GHz ~ 40GHz이다. 대규모 어레이로 10GHz ~ 40GHz 신호를 분배할 때 어려움이 있기 때문에 이를 고려해서 ADAR2001은 4x 체배기를 포함한다. 그러므로 이 송신기 IC 앞 단의 모든 경로와 신호 분배는 2.5GHz ~ 10GHz 주파수 범위에서 이루어진다.

ADAR2001 송신기의 주요 RF 소자들로는 RF 입력 버퍼, 스위칭 가능 고조파 필터를 내장한 4x 주파수 체배기, 1:4 신호 스플리터, 4개의 차동 출력 전력 증폭기(다이폴 안테나나 스파이럴 안테나 같은 차동 안테나 구조를 구동하기 위한 것)를 포함한다. 그림 3은 ADAR2001의 상세한 블록 다이어그램을 보여준다.

이 체배기 출력은 프로그래머블 감쇠기를 거친 다음에 4개로 분할되어 4개의 전력 증폭기로 인가된다. 체배기 블록에 필터링을 구성할 수 있을 뿐 아니라, 각각의 PA는 활성화 또는 비활성화 될 수 있는 저역통과/노치 필터를 포함하고 있다. 이 필터는 최대 20GHz의 출력 주파수까지는 활성화되어야 하고, 20GHz 이상일 경우에는 비활성화되어야 한다.

프로그래머블 감쇠기를 활용하면 출력 전력 대 주파수를 비교적 평탄하게 하는 데 도움이 된다. 이 감쇠기는 약 15dB의 디지털 스텝 감쇠 범위를 제공한다. 출력 주파수가 10GHz ~ 40GHz까지 스윕하기 때문에, 주파수에 대해 원하는 출력 전력 평탄도를 유지하기 위해서는 이 감쇠를 낮춰야 한다. 이렇게 하면 각각의 차동 PA 출력에서 +5dBm의 공칭 PA 출력 전력과 -20dBc ~ -30dBc 범위의 고조파 억제 결과를 얻을 수 있다.

10GHz ~ 40GHz까지 전체 주파수를 스윕하려면, 최적의 고조파 제거 및 출력 전력을 달성하기 위해 체배기/필터 블록 설정을 일곱 번 조정해야 한다. 또한, 이 시스템이 한 주파수를 처리하는 동안 각각의 송신기 채널을 연속해서 켜고 꺼야 한다. SPI 명령에 병목이 일어나지 않도록, ADAR2001은 최대 70개 상태로 프로그램할 수 있는 2개의 상태기(state machine)를 포함한다. 이 디바이스의 RAM이 프로그램된 다음에는, 이 디바이스의 MADV(Advance) 핀에 간단한 펄스를 인가해서 상태를 전진시킬 수 있다. 이러한 특성들이 결합됨으로써, 2ns의 빠른 채널 스위칭 시간이 가능해졌다. 이 스위칭 시간은 IC들 간에 스위칭할 때도 마찬가지다(예를 들어, 디바이스 A의 채널 4를 끄고, 디바이스 B의 채널 1을 켤 때). 전체적인 스캔을 위해서는 여러 주파수에서 모든 채널을 스윕해야 하므로 스위칭 시간이 결정적으로 중요하다. 예컨대 어레이가 500개의 소자들로 구성되고 10GHz ~ 40GHz의 주파수 범위에서 50MHz 단위로 스윕한다면, 전체 스캔을 완료하기 위해서는 총 300,000번의 채널 스위칭이 이루어져야 한다.

채널별 RF 출력 전력은 개별적인 온칩 RF 검출기를 사용해서 모니터링할 수 있다. 또한 다이 온도는 온칩 온도 센서를 이용해 모니터링할 수 있다. 이들 센서는 5:1 아날로그 멀티플렉서(MUX)로 신호를 전달하고, 여기서 원하는 신호들은 온칩 8비트 ADC로 다시 전달된다.

ADF4368 PLL/VCO는 송신기 네트워크로 스티뮬러스를 제공한다. 이 출력 신호는 송신 채널 수에 따라서 여러 번 분할된다. ADF4368의 비교적 높은 +9dBm의 출력 전력과 ADAR2001의 최소 입력 임계값(-20dBm)은, 증폭기 버퍼링이 요구되기 전에 ADF4368의 출력을 여러 갈래로 분기할 수 있게 해준다.

수신기

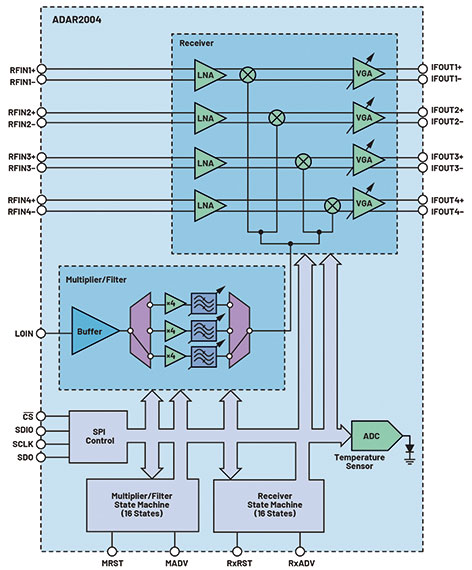

수신기는 송신 신호가 반사되는 것을 포착한다. 수신기는 다채널 믹서와 ADC로 이루어진다. ADAR2004는 쿼드 믹서 및 ADC 드라이버에 디지털 프로그램가능 이득 증폭기(DGA)를 결합하고 있다. LO 입력 역시 내부에 4x 체배기를 포함하고 있는데, 이차 PLL에 의해서 구동된다. 이 PLL은 무선 주파수로부터 해당 출력 주파수를 오프셋해서 믹서가 실수 IF 출력을 생성하도록 한다. 그러면 이 믹서의 IF 출력은 디지털 하향변환을 통합한 16채널 연속-시간 시그마 델타(CTSD) ADC인 AD9083에 의해 샘플링된다. 제로-IF 아키텍처 대신 IF 샘플링 아키텍처가 선택된 이유는, 수신기에서 LO 누설로 인한 DC 오프셋과, LO의 쿼드러처 스플리터에서 불완전한 쿼드러처 평형으로 인한 I/Q 오차를 피하기 위해서다. 보정을 통해서 이러한 불완전성을 완화할 수는 있는데, LO 누설과 쿼드러처 오차는 주파수에 따라 달라지기 때문에 모든 입력 주파수에서 보정이 필요할 것이다.

그림 4는 ADAR2004 쿼드 믹서의 블록 다이어그램을 보여준다. LO 입력을 2.5GHz ~ 10GHz 사인파로 구동해서 체배기 출력에서 10GHz ~ 40GHz를 발생한다. 이 체배기 출력은 자신의 IF 출력에 프로그래머블 이득을 가지고 있는 4개의 믹서로 전달된다. ADAR2001 송신기와 마찬가지로 ADAR2004 수신기 역시 사전에 프로그램 가능한 2개의 온칩 상태기를 포함한다.

[그림 4] ADAR2004 10GHz ~ 40GHz 수신기의 블록 다이어그램

다채널 ADC

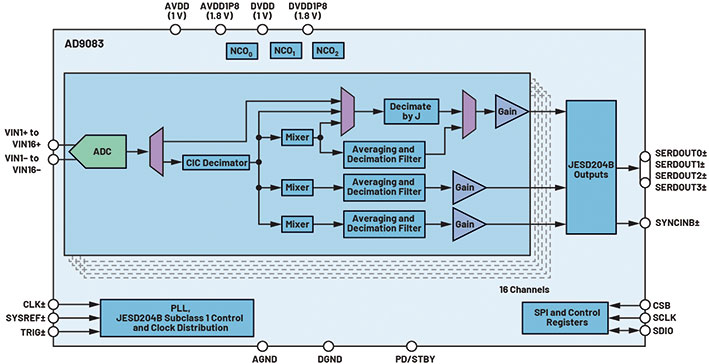

그림 5는 AD9083 16채널 CTSD ADC의 블록 다이어그램을 보여준다. 이 ADC의 입력은 ADAR2004의 IF 출력과 동일한 공통 모드 전압을 갖도록 설계되었기 때문에 믹서 출력과 ADC 입력을 곧바로 연결할 수 있다. AC 커플링 커패시터를 사용하지 않으므로 믹서 출력이 갑자기 스위칭할 때(예를 들어 믹서의 입력에서 주파수 스텝이 이루어지는 동안) 충전/방전 트랜션트가 발생하지 않는다.

각각의 ADC는 시그마-델타 ADC로부터 대역외에서 형성된 잡음을 필터링하고 샘플 레이트를 낮추기 위해 신호 처리 타일을 포함한다. 각각의 타일은 CIC 필터, 여러 개의 FIR 데시메이션 필터(J 블록으로 데시메이션)를 가진 쿼드러처 DDC, 또는 데이터 게이팅 애플리케이션을 위해 애버리징 데시메이션 필터를 가진 최대 3개의 쿼드러처 DDC 채널을 포함한다. 쿼드러처 DDC 채널을 최대 3개까지 사용할 수 있으므로 최대 3개의 주파수를 동시에 복조할 수 있다. 이 기능을 사용해서 어떻게 스캔 시간을 크게 단축할 수 있는지는 뒤에서 더 자세히 설명한다.

시스템 셋업과 작동

ADAR2001과 ADAR2004는 대규모 어레이로 효율적으로 동작하도록 특별히 설계되었다. 특히 배선 작업의 수고를 더는 데 중점을 두었다. ADAR2001과 ADAR2004의 RFIN 및 LO 입력 포트는 -20dBm에 이르는 낮은 입력 레벨로 동작할 수 있다. 이들 입력을 공통 LO 소스(이 경우에 ADF4368)를 사용해서 구동하는 것이 바람직하므로, 이처럼 낮은 입력 감도는 증폭이 요구되기 전에 여러 번의 패시브 팬아웃을 가능하게 한다. 예를 들면, 윌킨슨(Wilkinson)의 전력 스플리터 제품 순손실이 1dB라고 한다면, ADF4368의 9dBm 출력 전력을 수동으로 7번 팬아웃할 수 있고, 128개의 디바이스(512 채널)를 구동할 수 있다.

또한 ADAR2001과 ADAR2004의 온칩 시퀀서를 구동하는 Advance 핀과 Reset 핀은 병렬로 구동할 수 있도록 설계함으로써, 프로세서나 FPGA가 제공해야 하는 GPIO 수를 최소화할 수 있게 했다. 시퀀서에 충분한 깊이와 복잡함을 제공함으로써, 한 세트의 Advance 펄스와 Reset 펄스를 사용해서 최대 16개의 ADAR2001 디바이스를 구동할 수 있다.

작동에 앞서, ADAR2001과 ADAR2004의 시퀀서를 프로그램해야 한다. 두 디바이스 모두 SPI 명령을 사용해서 모든 기능에 액세스할 수 있지만, 그에 따른 지연시간이 전반적인 스캔 시간을 허용할 수 없을 정도로 길게 만들 수 있다.

이제 64 채널 시스템(64개의 송신기, 64개의 수신기)을 채널 기반 스캔으로 어떻게 셋업해야 하는지 살펴보자. 채널 기반 스캔이란 어떤 한 주파수로 모든 송신 채널들을 사이클링한 다음, 주파수를 높여가면서 이 과정을 반복하는 것이다.

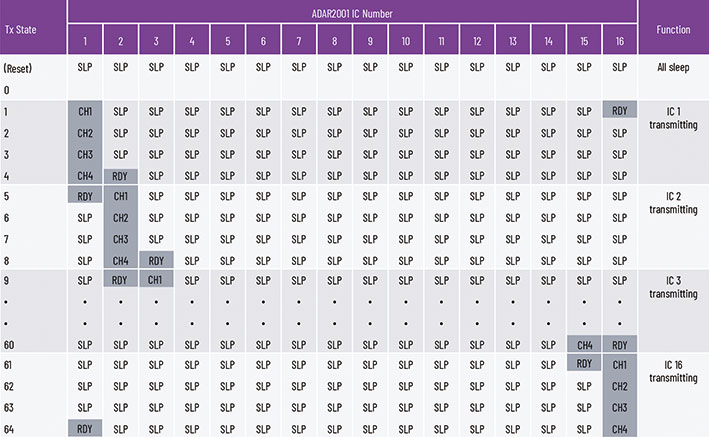

그림 6은 이 스윕을 하기 위해서 16개 ADAR2001 디바이스의 상태기들을 어떻게 프로그램해야 하는지 보여준다. 이 아키텍처의 가장 큰 목적은, 공통의 제어 라인을 사용해서 여러 디바이스를 시퀀싱할 수 있도록 하는 것이다.

IC 2 역시 마찬가지로 상태 5부터 상태 8까지만 작동한다. 그 동안 나머지 모든 IC들은 SLP 모드이거나 RDY 모드이다. 이런 식으로 일정한 온(on) 사이클 간격으로 16개의 상태기를 구성함으로써 병렬 펄스들을 사용해서 모든 16개 디바이스의 Advance 라인과 Reset 라인을 구동할 수 있다.

RDY 모드는 스위칭 시간을 최적화하고 전력 소모를 줄이기 위해서 개발된 중간적 상태이다. 대부분의 송신기가 대부분의 시간 동안 비활성화 상태로 있기 때문에, 전력 소모를 줄이기 위해서는 SLP 모드일 때 전력 소모를 낮추는 것이 중요하다. 그런데 SLP 모드에서 송신 모드로 전환하기 위해 필요한 시간(50ns)이 시스템 관점에서는 과도하기 때문에 스캔을 하는 동안 지연이 발생할 것이다. RDY 모드는 IC가 송신할 준비가 되었을 때 사용할 수 있는 중간적 상태이다.

그림 6에서 보면, 상태 4일 때 IC 1의 채널 4가 송신을 하고 IC 2는 RDY 모드가 되어서 송신을 할 수 있는 준비를 하고 있다. 송신기 상태 4에서 5로 전환하면, IC 1은 송신 모드에서 RDY 모드로 전환하고 IC 2는 RDY 모드에서 송신 모드로 전환한다. 이 전환에는 10ns가 소요된다. 후속 온칩 채널 전환은 전환 시간이 2ns이다. 그러므로 1024개 소자로 이루어진 어레이에서 10GHz부터 40GHz까지 0.1GHz 간격으로 스윕한다고 했을 때 전체적인 스캔 시간은 20ms 미만일 것이다. 이는 PLL 동기화 시간이 50µs라고 가정했을 때이다. 더 빠른 주파수 안정화를 달성하기 위해서 핑퐁 모드로 동작하는 PLL을 2개 사용한다면 스캔 시간은 5ms도 되지 않을 것이다.

ADAR2004 수신기의 작동과 시퀀싱은 이보다 덜 복잡하다. 모든 수신기 채널이 항상 수신이 가능하도록 구성하는 것이 통상적이기 때문이다. 그렇다 하더라도, 수신기가 송신기와 동시에 스윕할 때 적절한 체배기 경로와 필터 설정을 선택하도록 하기 위해, 상태기들을 여전히 시퀀싱해야 한다.

앞서 언급했듯이 각각의 AD9083 ADC 채널은 최대 3개의 쿼드러처 DDC 채널에 액세스할 수 있다. 다시 말해, 3개의 주파수를 동시에 복조할 수 있다는 뜻이다. 단, 모든 3개 주파수가 이 ADC의 아날로그 입력 대역폭(125MHz)의 입력 주파수 범위 이내일 경우 그렇다. 예컨대 3개의 IF 톤을 50MHz, 75MHz, 100MHz로 배치함으로써 3개 모두를 동시에 I 및 Q 베이스밴드 데이터로 복조할 수 있다.

이러한 접근법을 송신단에 사용하기 위해서는 하나가 아니라 3개의 송신 PLL을 사용해야 한다. 3개의 송신 주파수를 항상 물리적으로 서로 다른 송신 IC에 지정해야 한다(ADAR2001의 체배기는 멀티톤 신호를 처리하지 못한다). 이들 3개 주파수는 항상 달라야 하되 주파수끼리 서로 가까워야 한다. 예를 들어 한 ADAR2001 디바이스의 한 채널로 10GHz로 송신한다면, 50MHz, 75MHz, 100MHz의 IF 출력을 지원하기 위해서 다른 두 디바이스는 10.025GHz와 10.050GHz로 송신해야 한다. 이 접근법은 송신 경로에 더 많은 하드웨어와 스위칭 인프라가 필요하지만, 전체 스캔 시간을 1/3로 줄일 수 있다는 이점이 있다.

맺음말

ADAR2001 쿼드 송신기, ADAR2004 쿼드 수신기, AD9083 16채널 ADC, ADF4368 PLL/VCO로 구성되는 이 칩셋은 통합 수준이 높아, 차세대 워크스루 밀리미터파 보안 스캐너를 구현하는 데 필요한 기능들을 제공한다. 상태기와 온칩 디지털 하향변환을 내부에 포함함으로써 기존의 중앙집중식 프로세싱의 부담을 크게 덜어줄 뿐 아니라, 프로세싱을 인텔리전트 에지로 분산할 수 있게 해준다. 따라서 중앙의 프로세서가 스캔 시 시스템 제어에 대해 신경을 덜 써도 되고, 이미 복조와 데시메이션이 이루어진 데이터를 받아볼 수 있다. 이 칩셋은 특별히 밀리미터파 보안 이미징 애플리케이션을 위해 설계된 것이지만, ADAR2001 송신기와 ADAR2004 수신기의 넓은 주파수 범위와 AD9083 16채널 ADC의 높은 집적 수준 덕분에 높은 채널 밀도와 빠른 스위칭을 필요로 하는 다른 많은 애플리케이션에도 사용할 수 있다.

단일 IC로 구현한 포괄적 시스템 보호의 통합 솔루션

조회수 312회 / Anthony Huynh

지속가능한 모빌리티를 가속화하는 진보한 전동화 기술

조회수 398회 / Patrick Morgan

5G 및 차세대 통신 장비를 위한 향상된 -48VDC 전원 공급장치 설계

조회수 378회 / Hamed M. Sanogo

오픈소스 평가 플랫폼을 활용한 초음파 송신 서브시스템 프로토타이핑 방법

조회수 611회 / Sunshine Grace Cabatan 외 1인

밀리미터파 구현에 새로운 DPD 접근법이 필요한 이유와 가치 정량화 방법

조회수 836회 / Hossein Yektaii 외 2인

극히 빠른 동적 응답을 달성하는 유연한 TLVR 구조의 트랜스포머 기반 ...

조회수 731회 / Xingxuan Huang 외 2인

µModule 레귤레이터의 진화

조회수 610회 / Analog Devices

아나로그디바이스 양성환 전무 인터뷰, 고객의 성공에 기여하는 ADI 파...

조회수 926회 / Analog Devices

차세대 밀리미터파 스캐너를 가능케 하는 에지 프로세싱

조회수 806회 / Eamon Nash

PDF 다운로드

회원 정보 수정