전원 애플리케이션으로 SiC와 GaN 활용 비교

글/Anup Bhalla, PhD., VP Engineering, Qorvo

실리콘 카바이드(SiC)와 갈륨 나이트라이드(GaN) 반도체 기술이 미래에 성장 잠재력이 큰 것으로 알려지고 있다. 캐스코드 구조를 적용한 SiC 디바이스를 사용함으로써 와이드 밴드갭 디바이스의 이점을 취하면서 기존 시스템을 손쉽게 업그레이드할 수 있다.

와이드 밴드갭 디바이스란 무엇이고 어떤 이점이 있는가?

실리콘 카바이드(SiC)와 갈륨 나이트라이드(GaN) 같은 와이드 밴드갭(WBG) 반도체 기술이 뜨거운 화제로 떠오르고 있다. 와이드 밴드갭 디바이스를 사용함으로써 범용 무선 충전에서부터 지극히 축소된 크기의 전원 컨버터에 이르기까지 많은 것들이 가능해질 것으로 기대된다. 하지만 이러한 기술들 중에서 어떤 것을 선택할지 결정하기가 꼭 간단치만은 않으며, 와이드 밴드갭 디바이스를 도입하는 시장 분야는 생각보다 더 폭넓을 수도 있다.

WBG 디바이스란 무엇인지부터 살펴보자. 반도체는 전자들을 가둬두고 있으며, 이 전자들은 원자핵 주위로 가전자대와 전도대라고 하는 특정한 에너지 대역들에 존재한다. 전자들이 전도대로 옮겨가야 전류 흐름에 기여할 수 있는데, 그러기 위해서 에너지를 필요로 한다. WBG 디바이스는 이렇게 필요로 하는 에너지가 실리콘(Si)보다 훨씬 높다. Si는 1.1eV(전자볼트)를 필요로 하는 것에 비해서, SiC는 3.2eV를 필요로 한다. WBG 디바이스는 전자들을 전도대로 이동시키기 위해서 더 높은 수준의 에너지를 필요로 함으로써 동일한 규모의 Si에 비해서 전계 항복 성능이 더 높다. 이러한 이유에서 SiC는 결함이 발생되기까지 더 높은 온도(열 에너지)를 견딜 수 있으며, 소재 자체에 있어서 열 전도성이 Si보다 약 3.5배 더 우수하다. 이러한 특성에 의해서 높은 전압과 전력대로 고주파 고온 동작이 가능하다.

초기에 SiC로 이용할 수 있는 디바이스는 단순한 다이오드였으나, 소재 기술이 발전됨에 따라서 JFET과 MOSFET을 제조하는 것이 가능하게 되었다. 그림 1은 수직형 트렌치 구조를 적용해서 극히 낮은 온(on) 저항을 달성하는 SiC JFET 셀과 측방향 구조를 적용한 GaN HEMT(고 전자 이동도 트랜지스터) 셀을 비교해서 보여준다.

[그림 1] SiC JFET 셀과 GaN HEMT 셀의 구조 비교

애플리케이션에 적합한 솔루션 찾기

낮은 전력대 및 중간 전력대 스위칭 애플리케이션에는 향상 모드 “normally-off” Si MOSFET과 이제 SiC MOSFET이 주로 사용되고 있는데, 이들 디바이스는 다음과 같은 단점들을 수반한다:

• MOSFET은 진성 바디 다이오드를 포함하는데, 이 바디 다이오드가 순방향 전압 강하가 높고 복구 전압(Qrr)이 비교적 높다. 더구나 Qrr이 온도에 걸쳐서 3배까지 변동적일 수 있다. 높은 Qrr과 높은 순방향 전압 강하는 회로로 높은 손실을 발생시킨다. 그래서 쵸퍼, 유도성 부하에 대한 하드 스위칭 브리지, PFC 스테이지에 널리 사용되는 브리지리스 토템폴 구성처럼 바디 다이오드를 전도해야 한다. 추가적인 병렬 SiC 쇼트키 다이오드를 사용해서 바디 다이오드를 바이패스할 수 있는데, 이 방법은 비용을 증가시키고 효과도 제한적이다.

• MOSFET은 게이트 턴온 임계값이 낮다. SiC 디바이스로 이 임계값이 약 2.2V이다. 그러므로 최대의 성능과 함께 안전한 동작을 위해서 게이트-소스 전압을 꽤 엄격한 한계 이내로 유지해야 한다.

• 게이트-소스 전압에 따라서 단락 회로 포화 전류가 변화되며 이것을 제어하기가 쉽지 않다. 이 점이 시스템 신뢰성에 있어서 중대한 과제이다.

• 입력, 출력, MOSFET 주변의 밀러 커패시턴스가 비교적 높다. 그러므로 상당한 게이트 구동 전력을 필요로 하고, 커패시턴스를 방전하고 충전할 때 손실을 초래하고, 밀러 커패시턴스를 통해서 게이트로 전류가 주입됨으로써 스퓨리어스 턴온을 발생시킬 수 있는 위험성이 있다.

바디 다이오드를 없애고 JFET을 사용하는 것을 생각해 볼 수 있는데, 이것은 애석하게도 제로 게이트 전압으로 “normally on”이고 약 -7V를 인가해서 오프(off)가 된다. “normally-on” 디바이스는 회로 차단기 같은 애플리케이션에는 유용하나, 스위칭 애플리케이션에는 “normally-off” 타입이 좀더 바람직하다.

스위치들을 결합한 캐스코드 구조

WBG 기술을 활용하면서도 MOSFET의 단점을 피하기 위해서 제조사들이 1930년대의 진공관 기술로 시계를 되돌려서 그림 2에서와 같은 캐스코드 구조를 도입하게 되었다.

그럼으로써 MOSFET과 같은 “normally-off” 디바이스를 얻게 된다. 그러면서 다음과 같이 MOSFET의 한계점들 또한 해결한다:

• 저전압 Si MOSFET으로 바디 다이오드를 포함하는데, 이 바디 다이오드는 Qrr이 매우 낮다. 고전압 SiC MOSFET의 다이오드보다 두 배 혹은 그 이상 낮으며, 표준적 고속 복구 다이오드보다는 20배가량 더 낮다. 그러므로 바디 다이오드가 전도하게 되는 실제 회로로 추가적인 병렬 다이오드가 필요하지 않다.

• Si MOSFET 게이트 구동은 SiC MOSFET과 비교해서 그렇게 까다롭지 않으며 최대 ±25V를 견딜 수 있다.

• 캐스코드 구조로 Si MOSFET의 게이트-소스 전압은 약 +8V로 최대의 향상 후에 단락 회로 포화 전류에 영향을 미치지 않는다. 그러면 이제 JFET의 수직형 트렌치로 핀치오프 효과를 통해서 전류를 제어할 수 있다. 핀치오프 효과가 실제적으로 전류를 포화 수준으로 제한한다. 이와 함께 전류에 의해서 발생되는 발열 효과가 JFET 채널의 전도성을 떨어트린다. 그럼으로써 자체적으로 제한하는 특성을 띈다. 높은 접합부 온도를 허용할 수 있다는 점 또한 도움이 된다.

• 캐스코드 구조에 사용되는 Si MOSFET은 저전압이고 이 용도로 최적화되었기 때문에 입력 커패시턴스 Ciss가 낮고 캐스코드 드레인-게이트 밀러 커패시턴스 Crss가 거의 0이다. (그림 3은 UnitedSiC의 1200V 60mΩ 디바이스의 경우를 보여준다.) 그럼으로써 게이트 구동 전력을 낮추고, dV/dt가 밀러 커패시턴스를 통해서 게이트 구동 회로로 전류 스파이크를 발생시킴으로써 스퓨리어스 턴온이 발생될 위험성을 제거한다.

• Coss와 관련해서 스위칭 시에 에너지 손실 Eoss가 발생된다. 650V 급의 디바이스로 SiC 캐스코드는 이 값이 약 6.5μJ로, 동급의 Si 또는 SiC MOSFET과 비교해서 절반이거나 혹은 더 우수하다.

그림 4는 600V 유도성 부하로 UnitedSiC의 UJC1206K 캐스코드 디바이스를 사용할 때 2.35Ω부터 20.5Ω 사이의 게이트 저항 R(on)을 사용해서 달성된 값들을 보여준다. 매 1nH의 인덕턴스가 1000A/마이크로초의 di/dt로 1V 트랜션트를 발생시킨다. 게이트 회로 루프로 이러한 트랜션트가 발생되면 턴온 또는 턴오프 마진을 줄일 것이다. 마찬가지로 손쉽게 달성 가능한 50V/ns의 dV/dt는 불과 20pF의 부유 커패시턴스로 1A의 전류 스파이크를 발생시킬 것이다.

그림 5는 WBG 기술들과 전통적인 Si 수퍼정션 MOSFET의 특성을 비교해서 보여준다.

[그림 4] 게이트 저항을 사용한 dV/dt 및 di/dt 조절

[그림 5] 각기 다른 기술의 상대적인 다이 크기 비교

기존 슬롯으로 캐스코드 디바이스를 사용해서 곧바로 대체

WBG 디바이스의 가장 큰 이점이라면, 수 메가헤르츠와 200℃ 이상의 접합부 온도로 높은 속도와 높은 온도로 동작할 수 있다는 점이다. 그럼으로써 크기와 비용을 크게 낮추고 효율을 높이도록 한다. 하지만 이것은 새로운 자기 소자, 공진 토폴로지, RF 스타일의 레이아웃을 사용해서 설계를 완전히 새로 했을 때의 얘기다.

대표적인 예로서 Google과 IEEE가 개최한 “Little Box Challenge”라고 하는 대회를 들 수 있다. 이 대회는 50W/입방인치 전력 밀도로 95% 효율 컨버터를 설계하는 것이었다. 이것은 당시에 최신 컨버터와 비교해서 크기가 10배나 더 작은 것이다. 이 대회의 우승자는 WBG 기술을 사용해서 145W/입방인치 이상을 달성했다.

하지만 설계를 완전히 새로 하는 것이 불가능하거나 경제적이지 않은 경우에 기존 장비를 업그레이드하는 것이 또 다른 거대한 시장을 형성할 것이다. 대부분의 WBG 스위치 솔루션은 IGBT나 Si MOSFET 같이 기존에 탑재되어 있는 부품들과 맞지 않는다. 이들 부품에 사용되는 게이트 구동 시스템은 SiC MOSFET이나 GaN HEMT 디바이스에 필요로 하는 정밀한 게이트 구동 전압과 호환이 되지 않는다.

하지만 캐스코드 SiC JFET은 다르다. 캐스코드 디바이스는 전통적인 TO-247 및 TO-220 케이스이고 넓은 범위의 게이트 구동 전압을 지원하므로 모든 다른 디바이스 표준을 수용할 수 있다(그림 6). 일부 캐스코드 디바이스는 과전압과 ESD로부터 보호를 위해서 게이트 클램핑 다이오드를 포함하기도 한다. 기존 시스템으로 IGBT와 Si MOSFET은 트랜스포머를 통해서 듀티 사이클에 따라서 변화되는 부정확한 전압으로 게이트를 직접적으로 구동한다. 이 점에서 있어서도 역시 SiC 캐스코드가 넓은 범위의 게이트 전압 구동을 허용하므로 쉽게 교체할 수 있다.

실제적으로 밀러 효과를 제거함으로써 시스템 안정성과 가능한 속도를 향상시키며, 게이트 구동 전력을 훨씬 낮춘다. UnitedSiC의 SiC 캐스코드 타입 UJC1210K 800V/20A를 IGBT 타입 IRG7PH35UD 600V/25A와 비교하면, 총 게이트 전하 QG(total)이 캐스코드는 47.5nC이고 IGBT는 85nC이다. 이것이 큰 차이가 아니라고 생각될 수 있으나, 캐스코드는 게이트로 0V/12V로 스위칭할 수 있는데 IGBT는 -9V/+15V를 필요로 한다. 필요한 게이트 구동 전력 PG는 다음과 같이 계산할 수 있다:

이 공식에서 F는 동작 주파수이고, VSW는 총 게이트 전압 스윙이다. 이 스윙이 IGBT는 캐스코드의 두 배이다. 그러므로 캐스코드는 필요로 하는 총 전력이 약 1/4이다. 매 스위칭 피리어드에 게이트를 완전히 충전하고 방전하기만 한다면 어떤 듀티 사이클로나 이 전력은 일정하다.

그러므로 IGBT, Si MOSFET, 심지어는 SiC MOSFET을 사용하는 많은 애플리케이션으로 SiC 캐스코드를 곧바로 교체해 넣을 수 있으며, 그러기 위해서 스위칭 속도를 최적화하도록 직렬 게이트 저항 값을 변경하기만 하면 된다. 그림 7은 SiC 캐스코드의 게이트 구동 회로를 보여준다. 특이하게도 R(on)이 R(off)보다 낮다는 것을 알 수 있다. 캐스코드로 내부적 발진을 피하기 위해서는 R(off)가 최소한 약 10Ω이어야 한다. 댐핑을 위해서 선택적으로 직렬 페라이트 비드를 사용할 수 있다.

[그림 7] SiC 캐스코드의 게이트 구동 회로

SiC 대 GaN

SiC보다 나중에 나온 GaN은 비용, 수율, 신뢰성 염려 때문에 더디게 도입되고 있다. GaN은 훨씬 더 높은 전자 이동도로 이론적으로 SiC나 Si보다 더 높은 스위칭 속도가 가능하나, 열 전도성이 SiC보다 3배 낮으므로 가능한 전력 밀도가 제한적이다. 현재 SiC 디바이스는 650V부터 1.2kV 혹은 그 이상까지 두루 사용되고 있는데, GaN은 대략 650V까지로 제한적이다. 이 전력대로 좀더 성숙한 기술로서 동일한 전압으로 더 낮은 비용과 검증된 견고성을 앞세운 SiC 디바이스와 경쟁하기 위해서 애쓰고 있다.

GaN 업체들은 비용을 낮추고자 하는 바람이 현실화됨에 따라서 데이터 센터, EV/HEV, 태양광 같은 낮은 전압/전력 대의 시장들로 도입이 확대되기를 희망하고 있다. 그런데 SiC 캐스코드도 역시 이들 시장 분야를 겨냥하고 있다. 특히 양방향 DC-DC 컨버터와 토템폴 PFC(뒤에서 설명) 같은 애플리케이션을 들 수 있다. IHS의 데이터에 따르면[1], 2020년대 중반까지는 차지하는 시장들이 비슷하게 유지될 것으로 보이며, WBG 시장이 전부 합쳐서 35억 달러 규모에 이르고 이 중에서 GaN은 여전히 대략 5억 달러에 그칠 것으로 전망된다.

SiC는 공급 사슬을 통해서 확실하게 자리를 잡고 있으며, 주요 유통판매 업체들을 통해서 관련 제품을 공급하고 있다.

SiC 트렌치 캐스코드는 성능 지표의 하나인 RDSA가 훨씬 우수하다는 점에서 GaN보다 우위에 있고 Si MOSFET이나 SiC MOSFET보다도 우위에 있다(그림 8). RDSA는 특정한 다이 면적으로 어느 만큼의 전반적인 온 저항을 달성하는가를 나타낸 것으로서, 동일한 전력대로 비교해 보면 SiC 캐스코드가 GaN보다 5~10배 더 우수하다. 달리 말하면 다이 크기를 5~10배 더 작게 할 수 있다는 뜻이며, 그러면 커패시턴스를 낮추고 웨이퍼당 더 많은 다이를 채취할 수 있으며 그럼으로써 비용을 낮출 수 있다. 열을 전달할 수 있는 면적이 줄어들기는 하나, SiC는 GaN보다 열 전도성이 3배나 더 우수하고 특성 변화가 거의 없이 최대 250℃까지 이르는 접합부 온도를 허용할 수 있다.

SiC와 GaN 사이의 좀더 실체적인 차이는 이용할 수 있는 패키징에 있다. SiC 디바이스는 주로 TO-247과 TO-220으로 제공됨으로써 기존 디자인으로 MOSFET과 IGBT를 곧바로 대체할 수 있다는 이점이 있다. 또한 다양한 표면실장 패키지들이 개발되고 있다. 하지만 GaN 디바이스는 제조사들 스스로가 리드형 패키지가 근본적으로 속도 제한적인 배선 인덕턴스로 인해서 최대한의 성능을 끌어내는 데 걸림돌이 된다고 인정해 왔다.

그래서 주로 표면 실장, 단일 소스, 칩 스케일 패키징을 적용해 왔다. 이 때문에 새로운 디자인에 도입하기가 제한적이다. 다만 새로운 디자인으로 GaN 디바이스 특성에 맞게 시스템 디자인을 설계하고 더 작은 수동 부품들을 사용할 수 있을 것이다. 특히 자기 소자와 커패시터를 들 수 있다.

시장 현황

SiC 캐스코드는 대체로 650V 및 1200V 정격으로 최대 85A 전류로 약 30mΩ의 온 저항으로 제공된다. 수퍼 캐스코드(super cascode) 디바이스도 나오고 있다. 수퍼 캐스코드는 JFET들을 직렬로 연결한 것으로서 3.5kV 이상의 정격이 가능하다. 최대 1700V로 약 70A와 45mΩ으로 SiC MOSFET 제품들이 나와 있으나, 캐스코드와 달리 내부 바디 다이오드가 비교적 느리고, 하드 스위칭 브리지 회로 같은 애플리케이션의 필요에 따라서 바이패스를 위해서 비싼 외부적 고속 SiC 다이오드를 사용해야 할 수 있다.

GaN 디바이스는 최대 650V로 대략 60A와 25mΩ으로 많은 SiC 디바이스들과 필적할 만하며, 이론적으로 더 빠른 스위칭이 가능하다. 그런데 흥미롭게도 100V 정격의 GaN 디바이스가 온 저항에 있어서 전통적인 Si MOSFET보다 결코 더 낫지 않으며, 그러므로 이 전력대로 보통의 MOSFET과 비교해서 크게 증가하는 비용을 상쇄하기 위해서 속도에 있어서 우위에 의존하고 있다.

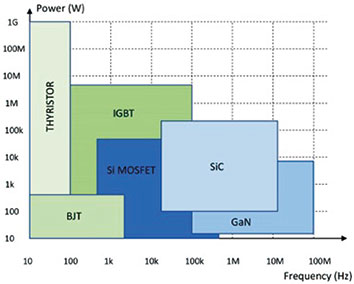

IHS의 데이터를 보면, 앞으로 WBG 디바이스 도입이 큰 폭으로 증가할 것으로 전망된다. IGBT와 전통적인 MOSFET 판매 역시도 시장의 성장에 발맞춰서 증가할 것이다. 논란이 되는 것은, 각기 다른 WBG 기술들이 특정 시장 분야들을 어떻게 차지할 것이냐 하는 것이다. 그림 9에서는 각기 다른 기술들이 미래에 전력대와 동작 주파수에 따라서 시장을 어떻게 차지할 것인지 전망한 것을 보여준다. 다만 여기서도 GaN의 입지는 앞으로 비용을 어느 정도로 낮추느냐에 따라서 달라질 수 있을 것이다.

[그림 9] 가능한 미래 전망

애플리케이션

WBG 디바이스는 빠른 스위칭과 낮은 손실로 고온으로 동작할 수 있으므로 성능을 중요하게 요구하는 군용과 산업용 애플리케이션에 사용하기에 이상적이다. 브리지 회로는 높은 전력대로 인버터, 용접 장비, Class D 오디오 증폭기, 모터 드라이브 등에 널리 사용되는 회로이다. 특히 큰 혜택을 볼 수 있는 애플리케이션이 브리지리스 토템폴 PFC 회로이다(그림 10). Si 기술을 사용한 이전의 회로는 MOSFET 바디 다이오드의 느린 성능 때문에 제약이 따랐다. 병렬 SiC 다이오드를 사용하면 도움이 되는데, 그러면 부품 수를 줄이고자 하는 목적과 상충된다.

이 때문에 임계 전도 모드를 사용해야 한다. 이 모드는 매 전도 간격 끝에 스위칭 전류를 0으로 설정한다. 그런데 이 가변 주파수 모드는 높은 피크 전류와 높은 EMI를 발생시킨다. 캐스코드 SiC JFET을 사용함으로써 연속 전도 모드를 사용할 수 있으며, 그럼으로써 효율을 높이고 인덕터 크기를 줄이고 고정적 동작 주파수를 사용해서 필터링과 EMI 문제를 완화할 수 있다. 1.5kW와 230VAC 라인으로 UnitedSiC의 UJC06505K 디바이스를 사용한 회로로 99.4%의 놀라운 효율을 달성하는 것으로 확인되었다[2].

[그림 11] SiC 캐스코드를 활용한 동기 정류

견고성 문제

고전력 애플리케이션으로는 트랜션트 단락 회로와 과전압에 대한 견고성이 염려되는 문제이다. 캐스코드 SiC JFET은 이 측면에서 매우 뛰어난 특성을 지녔다. 앞에서 핀치오프 효과에 대해서 언급했는데, 이 효과가 음의 온도 계수로 포화 전류를 제한한다.

과전압이 발생되면 SiC JFET 게이트-드레인 다이오드가 전도해서 전류가 내부적 게이트 저항으로 흐르게 하고 JFET 채널을 턴온해서 과전압을 클램프한다. 이때도 역시 SiC 다이가 높은 온도로 동작할 수 있다는 점에서 비교적 작은 다이 크기로도 상당한 수준의 애버랜치 에너지를 견딜 수 있다. 또한 신뢰성을 더욱 더 높이는 점으로서, 최종 테스트 시에 모든 부품들로 100% 애버랜치를 가해서 테스트를 실시한다[3].

PDF 다운로드

회원 정보 수정