항공 우주 및 방위 산업의 적응형 SDR 통신 시스템에서 민첩한 RF 트랜시버 사용

글/Stephen Evanczuk, DigiKey 북미 편집자 제공

항공 우주 및 방위(ADEF) 시스템 설계자는 동적 신호 환경에 민첩하게 대응할 수 있는 저전력 콤팩트 통신 시스템에 대한 끊임없는 요구에 직면해 있다. 기존 무선 통신 아키텍처를 뛰어넘는 소프트웨어 정의 무선 통신(SDR) 기술은 ADEF 무선 통신에 대한 빠르게 변화하는 요구 사항을 충족하는 데 도움이 될 수 있지만, SDR 구현은 기능적 요구 사항과 크기, 무게 및 전력(SWaP) 감소 요구 사항을 모두 충족해야 하는 여러 과제를 안고 있다.

이 기사에서는 성능에 영향을 주지 않으면서 민첩한 저전력 콤팩트 통신 시스템 설계를 간소화할 수 있는 Analog Devices의 비용 효율적인 SDR 솔루션을 설명한다.

새로운 과제로 인해 더욱 까다로워지는 요구 사항

설계자는 보안 무선 통신, 적응형 레이더, 전자전, 향상된 GPS 내비게이션 등 증가하는 산업용 핵심 응용 제품에서 효과적인 통신에 대한 요구에 직면해 있다. 이러한 새로운 과제로 인해 향상된 광대역 작동, 높은 작동 범위, 향상된 주파수 민첩성, 재구성 가능성 등에 대한 요구가 증가하고 있다. 하지만 통신 시스템이 무인항공기(USA), 이동식 장치 등 소형 배터리 구동 플랫폼으로 전환하면서 이러한 까다로운 기능적 요구 사항은 낮은 SWaP에 대한 요구와 상충할 수 있다.

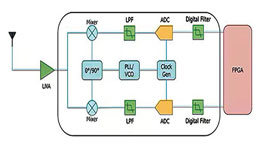

기존의 이산 소자 슈퍼헤테로다인 무선 통신 아키텍처를 기반으로 하는 설계 솔루션은 고성능, 넓은 작동 범위 및 최소 스퓨리어스 잡음을 제공한다. 설계자의 경우 이 접근 방식의 핵심인 중간 주파수(IF)에서 원하는 신호를 분리해야 하는 과제로 인해 일반적으로 SWaP가 높고 재구성 가능성이 거의 또는 전혀 없는 복잡한 설계를 하게 된다(그림 1).

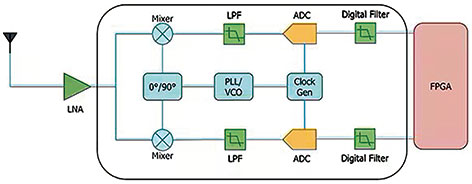

이에 반해 직접 변환(zero-IF) 아키텍처는 필터링 요구 사항과 고대역폭 아날로그 디지털 컨버터(ADC) 요구 사항을 모두 줄여서 단일 칩에서 구현될 수 있도록 설계를 간소화한다(그림 2).

SDR 기술은 기존 무선 통신 아키텍처의 한계를 극복할 수 있는 잠재력을 제공하지만 ADEF 응용 제품과 관련된 광범위한 요구 사항을 해결할 수 있는 솔루션은 거의 없다. Analog Devices의 ADRV9002 RF 트랜시버를 사용하여 개발자는 이러한 응용 제품의 낮은 SWaP와 향상된 성능 및 기능 요구 사항을 쉽게 충족할 수 있다.

낮은 SWaP로 최적화된 성능을 제공하는 통합된 기능

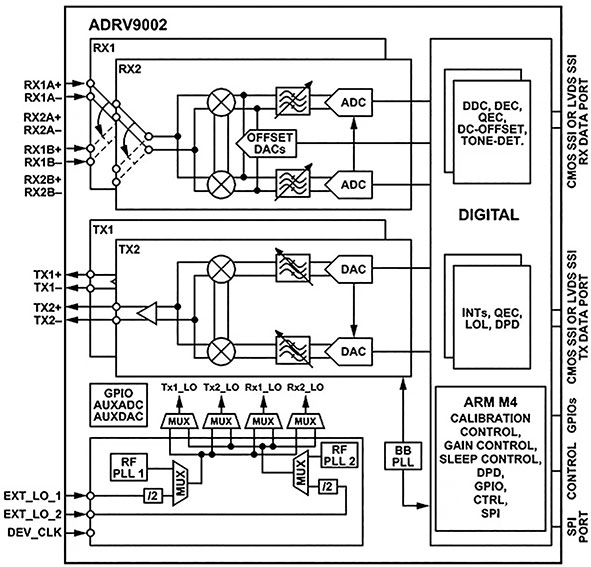

30MHz~6,000MHz 주파수 범위를 지원하는 ADRV-9002는 광범위한 응용 제품 요구 사항을 지원하는 데 필요한 RF, 혼합 신호, 디지털 기능을 모두 포함하는 고집적 트랜시버이다. 시분할 듀플렉서(TDD) 및 주파수 분할 듀플렉서(FDD) 작동을 모두 지원하는 이 장치는 프로그래밍 가능 디지털 필터, DC 오프셋 수정, 직각 위상 오류 수정(QEC)을 포함하는 개별 이중 채널 직접 변환 수신기 및 송신기 서브 시스템을 제공한다.

온 칩 합성기 서브 시스템 내에서 ADRV9002는 두 개별 위상 고정 루프(PLL) 경로를 제공한다. 즉, 고주파 RF 경로와 디지털 클록 및 컨버터 샘플링 클록 경로를 제공한다. 마지막으로 이 장치의 디지털 신호 처리 블록에는 자기 보정 및 제어 기능을 처리하는 Arm® M4 내장형 프로세서가 포함되어 있다(그림 3).

각 수신기 서브 시스템은 전류 모드 수동 소자 혼합기에 공급되는 이득 제어를 위해 저항 입력 네트워크를 통합한다. 그러면 트랜스 임피던스 증폭기는 혼합기의 전류 출력을 높은 작동 범위의 ADC에 의해 디지털화되는 전압 레벨로 변환한다. 수신기 시스템이 하나만 사용되는 FDD 응용 제품 또는 TDD 작동에서 사용 가능한 송신기 슬롯에서 미사용 수신기 입력을 사용하여 송신기 채널에서 LO 누설 및 QEC를 모니터링하거나, 미사용 수신기 입력을 사용하여 전력 증폭기(PA) 출력 신호 레벨을 모니터링할 수 있다.

후자의 기능은 모니터링된 PA 신호 레벨을 사용하여 출력을 선형화하는 데 필요한 적절한 전치 왜곡을 적용하는 ADRV9002의 통합 디지털 전치 왜곡(DPD) 기능에서 작동한다. 이 기능을 통해 ADRV9002에서 PA를 포화 상태에 가깝게 구동하여 효율성을 최적화할 수 있다.

전력 및 성능 조정

ADRV9002 장치는 196-볼 칩 스케일 패키지(CSP) 볼 그리드 어레이(BGA)에서 완벽하게 통합된 솔루션을 제공하며, SDR ADEF 통신 시스템의 크기와 무게를 최소화한다. 개발자가 전력 소비를 최적화하도록 돕기 위해 ADRV9002는 성능과 전력 사이의 적합한 균형을 찾을 수 있도록 특별히 고안된 여러 기능을 통합한다.

블록 레벨에서 개발자는 개별 신호 경로 블록에 전력 조정 기능을 배포하여 성능 저하를 전력 소비 감소로 상쇄할 수 있다. 또한 TDD 수신(RX) 및 송신(TX) 프레임의 블록을 비활성화하여 RX/TX 또는 TX/RX 회송 시간을 희생하는 대신 전력 소비를 줄일 수 있다. 개발자가 전력 대비 성능을 최적화할 수 있도록 돕기 위해 각 ADRV9002 수신기 서브 시스템에는 두 쌍의 ADC가 포함되어 있다. 한 쌍은 고성능 시그마-델타 ADC로 구성되며, 전력 소비가 중요한 경우 두 번째 쌍으로 대체될 수 있다.

주기적으로 비활성 상태가 지속되는 응용 분야의 경우 ADRV9002의 RX 모니터 모드를 채택할 수 있다. 이 모드에서 ADRV9002는 프로그래밍된 듀티 사이클에 따라 최소 절전 상태와 감지 상태를 교대로 작동한다. 감지 상태에서 이 장치는 수신기를 활성화하고 개발자가 프로그래밍한 대역폭 및 RX LO 주파수를 통해 신호를 획득하려고 시도한다. 장치에서 프로그래밍된 임계값을 초과하는 신호 전력 레벨을 측정하면, 모니터 모드가 종료되고 원하는 신호를 처리하기 위해 ADRV9002 블록이 구동된다.

신속한 시제품 제작 및 개발

엔지니어가 평가, 시제품 제작 및 개발 단계를 신속하게 전환하도록 돕기 위해 Analog Devices는 ADRV9002 기반 시스템에 대한 포괄적인 하드웨어 및 소프트웨어 지원을 제공한다.

하드웨어 지원을 위해 Analog Devices는 한 쌍의 ADRV9002 기반 카드를 제공한다.

• ADRV9002NP/W1/PCBZ: 30MHz ~ 3GHz 범위에서 작동하는 저대역 응용 제품용 카드

• ADRV9002NP/W2/PCBZ: 3GHz ~ 6GHz 범위에서 작동하는 고대역 응용 제품용 카드

FMC 커넥터가 탑재된 이러한 카드는 전력 조정 및 하드웨어 인터페이스와 클록 및 다중 칩 동기화(MCS) 분배 기능을 갖춘 기판 실장 ADRV9002를 지원한다. 이 카드는 FMC 커넥터를 통해 FPGA 마더보드(예: 전력 및 응용 제품 제어를 위한 AMD의 ZCU102 평가 기판)에 연결된다.

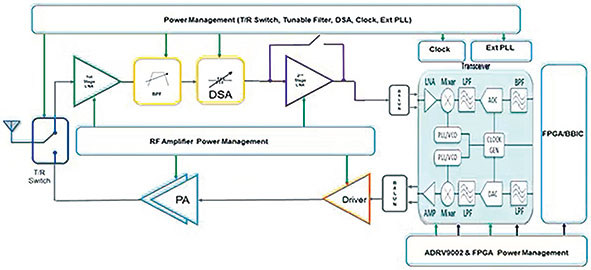

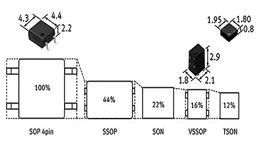

Analog Devices는 지원 패키지에서 ADRV9002NP 무선 통신 카드에 대한 전체 회로도와 자재 명세서(BOM)를 제공한다. 회로도 및 BOM은 대부분의 응용 제품에 대한 맞춤형 하드웨어 개발에 효과적인 시작점이 된다. 일부 응용 제품에서는 특정 신호 조절 요구 사항을 충족하기 위해 추가 RF 프런트 엔드가 필요하다. 이러한 응용 제품의 경우 개발자는 몇 가지 추가 부품만 있으면 설계를 완료할 수 있다(그림 4).

• ADRF5160 RF 스위치

• HMC8411 저잡음 증폭기(LNA)

• ADMV8526 디지털 방식으로 튜닝 가능한 대역 통과 필터

• HMC1119 RF 디지털 스텝 감쇠기(DSA)

• HMC8413 구동기 증폭기

• HMC8205B PA

Analog Devices는 설명서와 다운로드 가능한 소프트웨어 패키지를 통해 포괄적인 소프트웨어 개발 지원을 제공한다. 위에서 언급한 개발 하드웨어를 사용하는 개발자는 Analog Devices의 제품 라인 소프트웨어 또는 오픈 소스 소프트웨어 패키지를 기반으로 시제품 제작 및 개발을 진행할 수 있다.

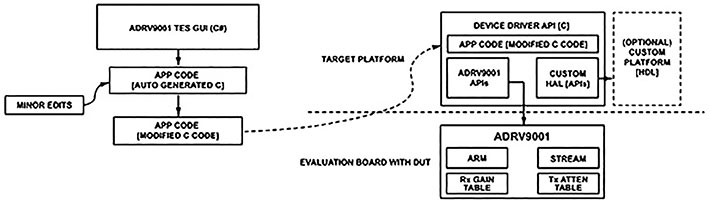

이 기사에서는 제품 라인 소프트웨어에 대해서만 논의한다. 오픈 소스 개발 방법에 대한 자세한 내용은 Analog Devices의 ADRV9001/2 시제품 제작 플랫폼 사용 안내서를 참조한다. Analog Devices는 회사의 지원 설명서에서 ‘ADRV9001’은 ADRV9002와 다른 ADRV9001 제품군을 포괄하는 제품군 지정자라고 명시했다. 따라서 아래 텍스트 또는 그림 5에서 ADRV9001은 이 기사의 초점인 ADRV9002 장치에 적용된다.

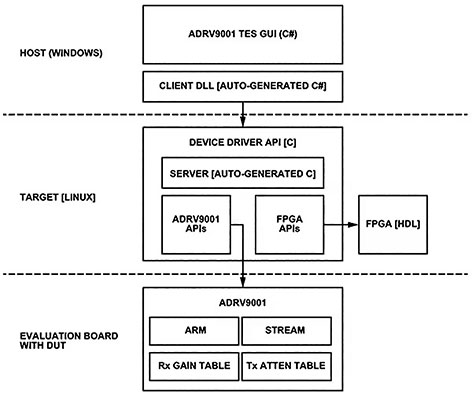

Analog Devices의 제품 라인 소프트웨어 개발 키트(SDK) 배포를 통해 제공되는 회사의 Windows 기반 트랜시버 평가 소프트웨어(TES) 도구는 트랜시버 성능을 빠르게 구성하고 평가하기 위해 접근 가능한 시작점을 제공한다.

Analog Devices의 ADRV9002 기반 카드와 AMD의 ZCU102 평가 기판으로 평가 및 시제품 제작을 수행하는 동안 TES 도구는 하드웨어를 구성하고 캡처된 데이터를 관찰하기 위한 그래픽 사용자 인터페이스(GUI)를 제공한다(그림 5).

TES 도구는 Linux 환경, MATLAB 환경 또는 Python에 컴파일될 수 있는 C# 코드를 자동으로 생성한다. SDK는 AMD ZCU102 플랫폼용으로 개발된 ADRV9001 API 패키지를 포함하여 전체 소프트웨어 라이브러리 및 응용 프로그래밍 인터페이스(API) 세트를 제공한다.

또한 SDK 흐름은 평가 기판을 통한 평가 및 시제품 제작에서 개발자의 맞춤형 대상 환경으로의 마이그레이션을 직접 지원한다(그림 6).

결론

ADEF 응용 제품은 점점 더 복잡해지는 신호 환경에서 증가하는 과제에 직면하고 있다. 개발자는 더 넓은 주파수 범위에서 더 높은 성능에 대한 요구를 충족하면서 이러한 응용 제품을 배터리 구동 시스템으로 마이그레이션하는 것을 지원하기 위해 SWaP를 낮추어야 한다. 개발자는 Analog Devices의 고집적 트랜시버를 통해 SDR 솔루션을 구현하여 이러한 요구 사항을 효과적으로 해결할 수 있다.

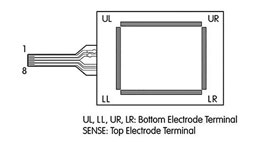

안정적인 터치스크린을 빠르게 구현하는 방법

조회수 141회 / Steven Keeping

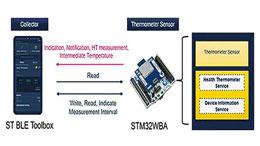

Bluetooth 5.3을 Edge IoT 설계에 빠르고 비용 효율적으로 추가하는 방법

조회수 375회 /

적절한 안전 컨트롤러 선택의 복잡성 해결

조회수 99회 / Jeff Shepard

반도체 자동화 테스트 장비에 SSR을 사용하는 방법

조회수 108회 / Jens Wallmann

항공 우주 및 방위 산업의 적응형 SDR 통신 시스템에서 민첩한 RF 트랜...

조회수 365회 / Stephen Evanczuk

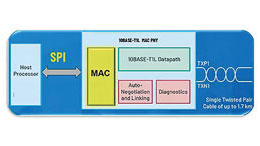

10BASE-T1L을 통한 건물 자동화 혁신

조회수 198회 / Rolf Horn

다기능 전원 공급 장치를 사용하여 지능형 화재 안전 및 보안 시스템 신...

조회수 340회 / Art Pini

전력 소자 구동기의 선택 및 시작하는 방법

조회수 557회 / Bill Schweber

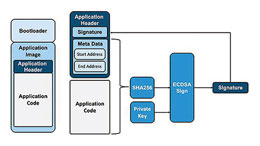

DSC와 MCU를 사용하여 내장형 시스템 보안을 보장하는 방법

조회수 568회 / Stephen Evanczuk

PDF 다운로드

회원 정보 수정