램리서치, EUV 리소그래피 위한 건식 레지스트 신기술 발표

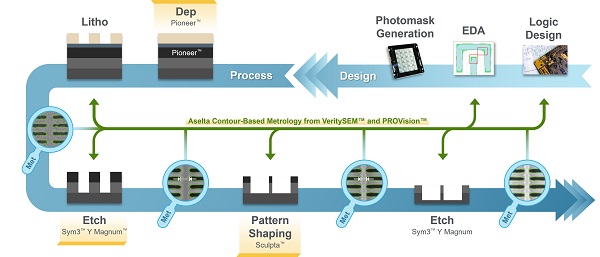

램리서치가 EUV 노광 공정에서 회로 선폭 미세화의 열쇠를 쥔 해상도(resolution)를 높여 수율과 생산성을 크게 높이는 건식 레지스트 신기술을 공개했다.

반도체 업계에 혁신적인 웨이퍼 제조 장비 및 서비스를 공급하는 램리서치(Lam Research)가 극자외선 패터닝(EUV patterning)에 사용될 건식 레지스트 신기술을 26일(현지 시간) 미국 새너제이에서 개최된 국제광공학회(SPIE Advanced Lithography) 컨퍼런스에서 발표했다. 이번 건식 레지스트 신기술은 증착과 식각 공정 분야를 선도하고 있는 램리서치가 ASML, 다국적 반도체 연구소인 imec와의 전략적 제휴를 통해 개발했다.

26일 공개된 램리서치의 새로운 건식 레지스트 기술로 EUV 리소그래피의 해상력을 높여 웨이퍼의 수율과 생산성을 한층 높일 수 있게 되었다. 새로운 건식 레지스트 솔루션이 제공하는 뛰어난 EUV 민감도와 해상력으로 웨이퍼 EUV 리소그래피 공정에 대한 비용 절감 효과도 함께 거둘 수 있을 것이란 기대다.

현재 전 세계 최첨단 칩 제조 업체들이 EUV 리소그래피 시스템을 대량 생산에 사용하고 있기 때문에, 이번 건식 레지스트 신기술이 제공하는 해상력과 생산성은 향후 공정 노드를 효율적으로 확대하는데 크게 기여할 것으로 기대된다. 새로운 건식 레지스트 기술은 조사선량 (線量, dose)을 줄이고 해상력은 증가 시켜 생산성을 높이면서 노광 공정 윈도우를 확대하는 효과를 거둘 수 있다. 또한, 소재 사용량을 5분의 1에서 10분의 1까지 줄일 수 있어 비용 절감은 물론 사회적 책임을 나타내는 ESG 경영( Environmental, Social, Governance)에 대응하는 데도 기여할 것으로 보고 있다.

피터 베닝크(Peter Wennik) ASML 회장 겸 최고경영자는 "ASML은 전 세계 반도체 업계를 선도하는 파트너들과 20년이 넘게 지속해서 연구개발(R&D)을 이어 왔으며, 그 결과 현재는 EUV가 대량 칩 제조 공정의 핵심으로 자리 잡게 됐다.”며, "앞으로도 램리서치, imec과의 긴밀한 협력을 통해 이 기술을 고도화시키고 확장해 갈 것”이라고 말했다. 아울러 “전략적 제휴를 통해 개발한 이번 건식 레지스트 신기술은 칩 제조업체들이 더 낮은 비용으로 더 높은 성능의 칩을 제조할 수 있도록 지원함으로써 기술의 잠재력과 새로운 가능성을 열어 가는 기회가 될 것”이라고 전했다.

팀 아처(Tim Archer) 램리서치 회장 겸 최고경영자는 "이번 공개된 혁신 기술은 ASML, imec과의 파트너십이 고객과 업계에 혁신적인 가치를 가져다 준 완벽한 사례"라며, “램리서치는 앞으로도 증착과 식각 분야를 선도해 가면서도, 이번 기술을 통해 패터닝 솔루션을 포토 레지스트 리소그래피 재료로까지 넓힐 기회로 만들 것”이라고 말했다. 또한, “이번 건식 레지스트 신기술은 멀티 패터닝 솔루션이 업계 수준으로 자리 잡는 초기 단계를 지나, 이제는 EUV의 생산성과 효율성을 확대하는 램리서치의 패터닝 전략의 방향성을 보여주는 것”이라고 말했다. 이 같은 전략에 따라 램리서치는 건식 레지스트 기술로 EUV 노광 공정의 주요 과제들을 해결하기 위해 전 세계 칩 제조업체들과 협력하고 있으며, 더욱 향상된 로직 및 메모리 기기의 지속적인 확장이 가능하게 될 것으로 기대하고 있다.

뤽 반 덴 호브(Luc Van den hove) imec 회장 겸 최고경영자는 "패터닝 공정을 최적화하려면 다양한 기술이 필요하기 때문에 imec은 수 년 동안 핵심 파트너들과 협력해 패터닝 공정 개발을 개척해 왔다"고 말했다. 또한, “건식 레지스트 기술은 EUV 리소그래피의 도입과 기술 로드맵을 확대하는데 필요한 중추적 역할을 할 수 있을 것”이라며, “램리서치, ASML과 건식 레지스트 기술을 최적화해 가능한 최상의 효율을 얻을 수 있도록 할 것”이라고 말했다.

한편, 램리서치는 현지 시각으로 2020년 2월 26일 오전 9시 40분 미국 새너제이에서 열린 광학 박람회에서 이번 EUV 리소그래피 공정에 혁신을 가져올 건식 레지스트 신기술 개발을 알렸다.

버티브, 인공지능 기능의 차세대 마이크로 모듈형 데이터센터 출시

조회수 66회 / Vertiv

TTTech Auto, 복잡한 소프트웨어 통합을 혁신할 차세대 스케줄러 ‘Motio...

조회수 93회 / TTTech Auto

슈퍼마이크로, X14 서버 제품군에 6세대 인텔 제온 프로세서 탑재 예정

조회수 93회 / 슈퍼마이크로

스펙트럼 인스트루먼트 계측 카드 적용한 ‘차세대 EPR 분광기’ 나와

조회수 91회 / 스펙트럼 인스트루먼트

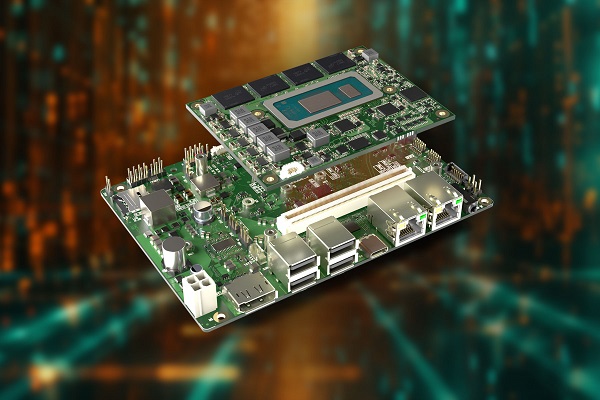

콩가텍, COM-HPC Mini 모듈용 3.5인치 애플리케이션 캐리어 보드 출시

조회수 124회 / 콩가텍

아테리스, FlexNoC 인터커넥트 IP 및 Magillem SoC 집적 소프트웨어

조회수 87회 / 아테리스

위로보틱스, 보행보조 웨어러블 로봇 윔(WIM) B2C 제품 출시

조회수 68회 / 위로보틱스

어플라이드 머티어리얼즈, 옹스트롬 시대 칩 제조 위한 패터닝 공정 혁신

조회수 108회 / 어플라이드

아비바, 스마트팩토리를 위한 지능형 솔루션 소개

조회수 64회 / 아비바코리아

PDF 다운로드

회원 정보 수정