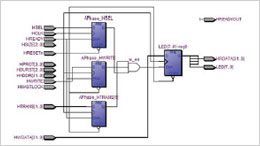

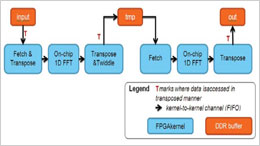

FPGA용 OpenCL을 사용한 2백만 포인트 주파수 도메인 필터 설계

이 글에서는 120~240 MSPS(million samples per second)에 이르는 다양한 샘플 속도를 지원하는 현행 FPGA 아키텍처로 1백만~1600만 포인트에 이르는 주파수 도메인 필터를 설계할 수 있다는 것을 설명하려고 한다. 그러한 예로서 OpenCL을 사용해서 2백만 포인트 단정도 주파수 도메인 필터를 설계하는 것에 대해서 설명한다. 이 글은 독자들이 FPGA 설계와 OpenCL의 기본 개념을 충분히 이해하고 있는 것으로 간주하고 있다.

Altera Design Contest 수상팀 논문_FPGA를 이용한 무선 빔프로젝터

조회수 3987회 / 김상돈 외 2인

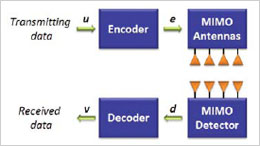

Korean MCU Design Contest 2015(2)_ 5세대 이동통신용 Massive MIMO 시...

조회수 3165회 / 공병용 외 1인

OpenCL표준을 이용한 FPGA 디자인 구현

조회수 2239회 / Altera

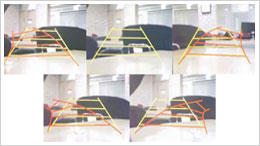

FPGA 논문 콘테스트 수상작(9)_FPGA를 이용한 눈동자추적 시스템

조회수 2772회 / 임태규 외 1인

FPGA용 OpenCL을 사용한 2백만 포인트 주파수 도메인 필터 설계

조회수 2291회 / Dmitry Denisenko 외 1인

FPGA 논문 콘테스트 수상작(8)_영상 신호로 차량의 방향을 알려주는 시스템

조회수 2869회 / 송영범 외 4인

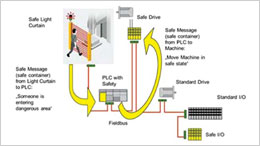

FPGA 기술을 사용함으로써 차별화된 ‘Functional Safety’ 솔루션의 비...

조회수 2292회 / David J. Moore 외 1인

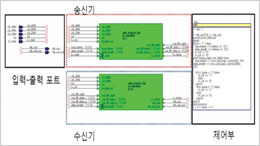

FPGA 논문 콘테스트 수상작(7)_IEEE 802.11a 송수신 모뎀 설계

조회수 2136회 / 박지은 외 1인

FPGA 논문 콘테스트 수상작(6)_비전 기반의 운전자 지원 네비게이션 시스템

조회수 2366회 / 배기영 외 2인

PDF 다운로드

회원 정보 수정