DDR5: 더 빠른 메모리 속도가 미래를 결정한다

글/벤 밀러(Ben Miller), 키사이트테크놀로지스 프로덕트 마케팅 관리자

DDR은 왜 중요할까?

빠른 데이터 처리를 위해서는 더 빠른 메모리가 필요하다. DDR SDRAM(2배 데이터율 동기식 동적 랜덤 액세스 메모리)을 사용하면 전 세계 컴퓨터가 메모리 데이터로 작업할 수 있다. DDR은 서버, 워크스테이션, 데스크톱뿐만 아니라 가전제품과 자동차 그리고 기타 여러 시스템에도 내장되어 있다. DDR SRAM은 어플리케이션을 실행하고 빠른 속도로 계산을 수행하는 데 사용되며 DDR 표준은 메모리 공급자가 메모리 읽기와 쓰기에 대해 동일한 수준의 품질과 속도를 따르도록 하고 있다.

JEDEC (Joint Electron Devicde Engineering council) 에서 정의한 DDR 표준은 새로운 새대가 등장할 때마다 속도 증가, 사용 공간 감소, 용량 증가 및 전력 효율성 향상을 포함하여 이전 세대에 비해 상당한 성능 향상을 제공한다. 최신 표준인 DDR5는 2020년에 출시되었다. 개발자들은 이미 이전 세대의 두 배인 초당 6400 메가트랜스퍼(MT/s)의 놀라운 데이터 전송 속도를 기대하고 있다.

이러한 메모리 속도의 향상은 거의 즉각적인 데이터 처리에 크게 의존하는 기술을 활성화한다. 그러나 이러한 성능 향상은 메모리 설계자와 제조업체에 새로운 설계와 테스트 과제를 안겨준다. DDR5 표준이 이러한 과제를 어떻게 해결하고, 개발자가 신생 기술에서 DDR5를 활용하는 방법과, 차세대 DDR이 갖게 될 모습에 대해 살펴본다.

Faster, not wider

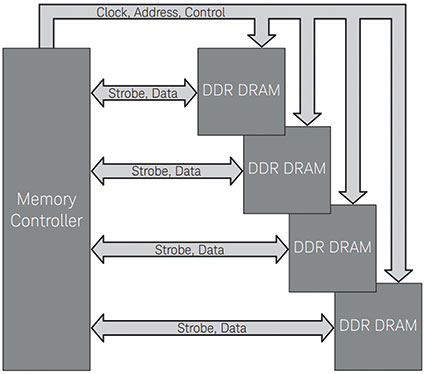

SDRAM이 탄생한 이후로 엔지니어들은 메모리 속도를 높여야 하는 과제에 직면했다. DDR은 칩 설계자와 디바이스 제조업체 간에 보편적인 표준을 제공하면서 더 빠르고 효율적인 메모리 처리 방법으로 등장하였다. 그림 1과 같이 DDR 메모리는 클럭, 주소 및 제어 신호를 전송하는 메모리 컨트롤러와 데이터를 저장하는 일련의 DRAM 칩으로 구성된다. 쓰기 작업에서 컨트롤러는 데이터와 스트로브 신호를 DRAM으로 전송하며 읽기 작업에서 DRAM은 동일한 양방향 라인을 통해 데이터와 스트로브 신호를 다시 돌려보낸다. DDR SDRAM은 1990년대 후반에 표준이 되었으며 이후 여러 번 성능이 향상되었다.

[그림 1] DDR에는 단방향 제어 신호와 양방향 데이터 버스가 모두 있다.

DDR 개발 전에는 메모리 속도의 범위가 최대 100MT/s 이내였다. 1세대 DDR 표준은 데이터 이전율을 최대 200~400MT/s로 높였다. 후속 세대가 등장할 때마다 일반적으로 비트 레이트가 이전 세대보다 두 배로 증가했다. 이러한 첫 번째 표준 그룹인 DDR1~DDR3은 데이터 비트 레이트가 도달함에 따라 신호 무결성이 증가하는 문제에 부딪쳤다. 그 과정에서 JEDEC는 모바일 어플리케이션에 최적화된 사양인 저전력 DDR(LPDDR)과 컴퓨터 그래픽에 최적화된 사양인 GDDR 등 관련 사양을 개발했다. DDR4가 출시되면서 3200MT/s의 속도로 인해 비트 오류율 문제가 일어나기 시작했다. 더 빨라진 속도로 신호 무결성을 훨씬 더 우선시함으로써 설계와 검증이 복잡해졌다. 클럭과 스트로브 신호는 차동 신호이며 노이즈를 상쇄하지만 컨트롤러와 DRAM 칩 사이의 양방향 데이터 신호를 포함한 다른 신호는 싱글 엔드 신호이므로 노이즈와 혼선(크로스토크), 간섭에 취약하다.

한 번에 더 많은 비트를 전송하여 DDR 비트 레이트를 달성하는 것도 가능한다. 많은 현대의 통신 프로토콜과 달리 DDR은 직렬 버스가 아닌 병렬 버스이다. 그러나 추가된 채널을 지원하려면 다이와 패키지를 모두 증가시켜야 하기 때문에 디바이스의 핀 수를 특정 양 이상으로 늘리는 것은 비현실적이며 비용도 많이 든다. 메모리의 핀 카운트는 이전 세대에서는 증가했지만, 이후에는 평준화되어 DDR5에는 DDR4와 동일한 수의 핀이 있다. 현재로서는 더 빠른 신호 속도만이 차세대 디바이스의 메모리 비트 레이트를 높이기 위해 선택할 수 있는 방법이다.

더 빠른 속도가 불러오는 과제

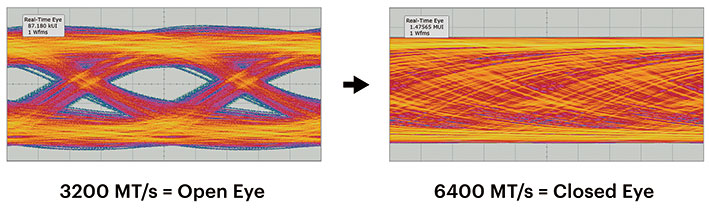

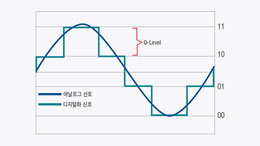

앞서 언급했듯이 더 빠른 전송 속도는 비트 오류율에 문제를 일으킬 수 있다. 데이터 비트는 충전된 커패시터에 저장되기 때문에 DRAM 프로세스는 본질적으로 속도에 반한다. 채널 및 상호 연결 효과는 고속으로 작동하는 신호에서 ISI(부호 간 간섭)을 일으킬 수 있다. 이는 오실로스코프에서 눈 다이어그램으로 나타나며 비트 레이트가 3600MT/s 이상으로 증가하면 점점 더 닫힌다. 높은 비트 오류율은 수신기가 신호에서 이러한 왜곡이 있는 부호를 해결할 수 없는 경우에 나타난다. 즉, 데이터 비트는 그림 2의 아이 다이어그램에 나타난 것처럼 고속에서 구별할 수 없게 된다.

[그림 2] 비트 레이트가 증가함에 따라 부호 간 간섭이 증가하여 아이 다이어그램이 나타난다.

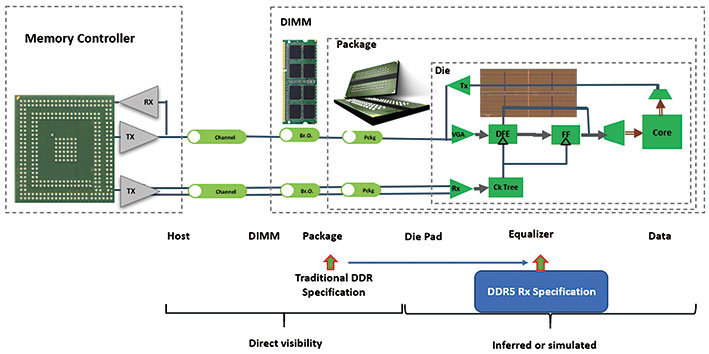

신호 무결성을 유지하기 위해 DDR5는 DFE(결정 피드백 이퀄라이제이션)를 통해 신호 왜곡을 보정하고 눈을 다시 연다. 비슷한 목적으로 이퀄라이제이션을 사용하는 고속 직렬 통신과 달리 DDR5는 DDR 컨트롤러 측면과 DRAM 다이 내부에 이퀄라이제이션을 적용한다. 이러한 요소는 DDR4에는 없었다. 특히 PHY는 커패시턴스로 인한 잠재적인 문제로 인해 DRAM 메모리 셀 어레이 외부에 있다. 그림 3에는 이러한 요소들이 DDR5 메모리 시스템에서 어디에 배치되는지를 보여주는 블록 다이어그램이 있다.

[그림 3] DDR에 새로 추가된 사양에는 이퀄라이저와 같은 다이 내부의 사양이 있다.

DDR 메모리 사이클의 모든 단계에서 엔지니어는 DDR5의 증가된 요구 사항에 주의를 기울여야 한다. 디바이스 시뮬레이션, 설계 및 검증 단계에서는 가장 신뢰할 수 있는 데이터 전송을 위해 송신기, 수신기 및 채널을 최적화해야 하며, 더 빠른 비트 레이트 요구 사항에 내재된 설계 복잡성 증가와 타이밍 마진 감소 문제를 처리해야 한다. 디바이스, 보드 및 시스템 테스트 엔지니어는 증가하는 ISI와 신호 무결성 문제를 항상 주시해야 하며 특히 DDR 결함을 디버깅할 때에는 데이터 경로의 이퀄라이저로 인해 프로세스가 더욱 복잡해진다. 궁극적으로 디바이스는 다른 메모리 콤포넌트와의 상호 운용성을 보장하기 위해 JEDEC DDR5 표준 준수 여부를 테스트해야 한다. 이러한 모든 노력과 복잡성은 보다 정교하고 빠른 메모리 전송 시스템에서 최고조에 달하며 낮은 비트 오류율을 유지하면서 6000MT/s 이상의 메모리 속도에 도달할 수 있도록 지원한다.

더 빠른 메모리로 미래 실현

DDR5는 아직 도입된 지 얼마 되지 않았다. JEDEC는 2020년 7월에 DDR5의 표준을 발표했다. DDR5를 지원하는 최초의 CPU 플랫폼은 2022년 초에 출시되었다. 그러나 이 플랫폼에서는 여전히 DDR4도 지원하므로 업계에서 DDR5를 실질적인 메모리 표준으로 허용하고 메모리 시스템을 새로운 표준으로 완전히 전환하는 데까지는 시간이 걸릴 수 있다. 앞으로 몇 년 동안 더 많은 개인용 컴퓨터, 서버 및 임베디드 시스템이 DDR5가 제공하는 더 빨라진 속도와 낮은 전력 및 큰 메모리 용량의 이점을 누릴 것이다. 이를 통해 고속 네트워킹과 데이터 처리에 대한 새로운 가능성이 많이 열릴 것이다.

사물 인터넷(IoT)과 V2X(Vehicle-to-Everything) 자율 주행 차량은 수십억 개의 새로운 디바이스를 클라우드 서비스에 연결할 5G와 400기가비트 이더넷으로 활성화되는 많은 기술의 일부에 불과하다. 모든 데이터를 처리하는 데 필요한 데이터 스토리지 인프라에는 특히 V2X와 같은 시간 엄수와 안전이 중요한 어플리케이션에서는 지금까지 본 것보다 더 빠르고 효율적인 메모리가 필요하다. 서버에 DDR5를 적용하는 과정은 더 빠른 무선 통신의 도입과 함께 이러한 새로운 기술을 가능하게 할 큰 진전이 될 것이다. 그러나 이러한 어플리케이션이 현실화되면 DDR5는 충분히 빠르게 작동할까?

DDR6: DDR5 데이터율의 2배

DDR5는 이제 막 시장에 도입되기 시작했지만 JEDEC와 얼리어댑터들은 이미 다음 세대를 기대하고 있다. DDR6는 이전의 모든 DDR 세대처럼 이전 세대의 최대 비트 레이트를 두 배로 증가시킬 가능성이 높다. 한 메모리 제조업체는 2021년 말에 JEDEC와 함께 DDR6 개발을 시작했으며 새로운 표준에서는 메모리 용량이 4배로 증가하고 속도가 12,000MT/s를 넘어설 수 있다고 발표했다. 그러나 앞서 언급한 속도 문제를 고려할 때 이러한 놀라운 비트 레이트 목표에 도달하려면 심각한 데이터 변형 왜곡을 일으키지 않고 신호를 더 빠르게 성공적으로 전송하기 위해 훨씬 더 큰 혁신이 필요하다.

한 가지 가능성은 DDR6에서 PAM(펄스 진폭 변조)나 QAM(직교 진폭 변조) 신호를 사용하여 Wi-Fi 및 이더넷과 같이 다른 표준을 따르는 것이다. DDR5는 이미 표준에 더 많은 데이터 처리를 추가하는 선례를 남겼기 때문에 다음 세대에서는 비트 레이트를 더 높이기 위해 더 복잡한 신호 방법을 사용할 수 있다. 주어진 채널을 통해 가능한 최대 비트 레이트를 정량화하는 섀넌-하틀리(Shannon-Hartley) 정리에 따르면 DDR4는 현재 DIMM의 상호 연결 용량의 약 10%만 차지한다. 지금부터 DDR6가 출시될 때까지 왜곡으로 인한 데이터 비트 손실 없이 나머지 90%를 사용하는 것이 JEDEC 엔지니어의 주요한 과제이다. 이들이 이러한 과제들을 해결할 수 있다면 미래에 더 많은 데이터 기반 기술에 필요한 토대를 마련할 수 있다.

새로운 현실

DDR6가 현실화될 때까지 개발자들은 DDR4에서 새로운 DDR5 표준으로 계속 이동할 것이다. 업데이트된 표준에 제품을 적용하려면 시간이 걸린다. 사양에 이퀄라이제이션을 추가하는 것을 포함하여 DDR5 표준에서 약간 더 복잡해진 특성은 시뮬레이션, 설계, 검증과 적합성 테스트가 모두 더 까다로워지고 오류 마진이 훨씬 더 줄어든 것이다. 그러나 많은 엔지니어들의 경우 이러한 변화는 더 빠른 비트 전송률을 위해 충분히 감수할 만 하다. 게이머와 데이터 센터 기술자, AI 및 자율 주행 차량 개발자에 이르는 이들의 고객은 이에 동의할 것이다. 더 빠른 메모리는 많은 필수 어플리케이션에서의 더 빠른 데이터 처리를 위한 핵심 요소이다.

키사이트는 JEDEC 및 DDR5 표준을 조기에 채택한 파트너들과 긴밀히 협력하고 있다.

2024 업계 예측(반도체, 전자 설계 자동화)

조회수 409회 / 키사이트

DDR5: 더 빠른 메모리 속도가 미래를 결정한다

조회수 926회 / Ben Miller

ADC 비트와 ENOB에 대한 이해: 오실로스코프 신호 무결성

조회수 4594회 / 키사이트테크놀로지스

PDF 다운로드

회원 정보 수정