SiC FET을 사용한 고전력 양방향 AC/DC 전원장치 설계

본 고에서는 다음과 같은 주제들을 살펴보려고 한다. 먼저 고전력 양방향 AC/DC 전원장치 애플리케이션에 대해서 개략적으로 알아본다. 그 다음에는 이러한 애플리케이션으로 적합한 토폴로지들과 이러한 토폴로지들로 적합한 전력 스위치와 드라이버를 어떻게 선택할지 알아보고 컨트롤러 선택 기준과 컨트롤러를 선택할 때 고려해야 할 것들을 알아본다. 마지막에는 디자인 사례를 들어서 살펴본다.

글/Robert Taylor, Texas Instruments

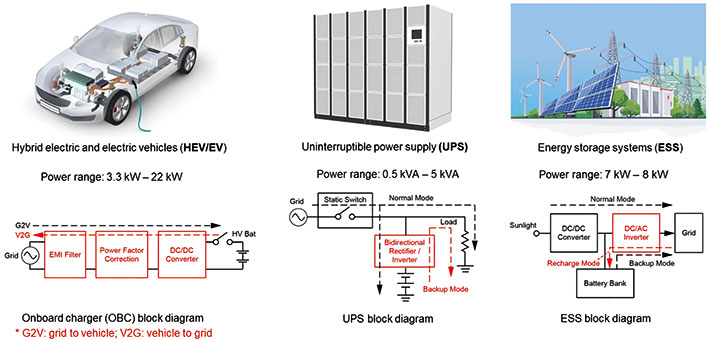

고전력 양방향 AC/DC 전원 애플리케이션으로서 대표적으로 3가지를 들 수 있다. 하이브리드 전기차(HEV)와 전기차(EV)는 자동차 배터리를 충전하기 위해서 온보드 차저를 사용한다. 충전 전력은 전력망에서 자동차로 흐른다. 이것을 G2V라고 한다. 온보드 차저의 전력대는 3.3kW부터 22kW까지 이른다. 일부 첨단 HEV/EV 디자인으로는 예를 들어서 고립된 상황에서 자동차에서 AC 기기로 전력을 제공할 수 있도록 하기 위해서 배터리에서 거꾸로 전력망으로 전력 흐름을 요구하기도 한다.

이것은 V2G라고 한다. HEV/EV로 V2G를 요구하는 경우에는 온보드 차저로 고전력 양방향 AC/DC 전원장치를 필요로 한다. 또 다른 대표적인 고전력 양방향 AC/DC 전원장치 애플리케이션으로는 비중단 전원장치(UPS)와 에너지 저장 시스템(ESS)을 들 수 있다. UPS와 ESS는 시스템 내로 배터리들을 설치한다. 일차 에너지 소스를 사용할 수 있을 때는 배터리를 충전한다. 일차 에너지 소스를 사용할 수 없을 때는 배터리의 에너지를 사용해서 부하로 에너지를 제공한다.

[그림 1] 고전력 양방향 AC/DC 전원 애플리케이션

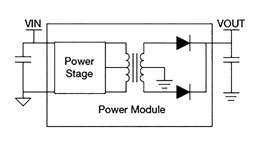

UPS와 ESS의 양방향 AC/DC 전원장치로는 수 킬로와트를 제공할 수 있는 전원장치가 요구된다. 또한 UPS와 ESS로는 일차 에너지 소스를 사용할 수 없을 때 에너지 흐름을 빠르게 전환할 수 있어야 한다. HEV/EV 온보드 차저로는 이 기능이 요구되지 않는다. 그러면 온보드 차저를 예로 들어서 고전력 양방향 AC/DC 시스템을 어떻게 설계할지 알아보자. 온보드 차저의 전원 스테이지는 두 부분으로 이루어진다. AC/DC 비절연형 정류기와 절연형 DC/DC 컨버터이다. 이 2스테이지 접근법은 전반적인 시스템 효율과 전력 밀도를 최적화하고, 손쉽게 접지 결함 보호를 할 수 있으며, 전력망 간섭 내성이 높다.

AC/DC 정류기의 출력 전압은 배터리 전압을 추종하도록 가변적일 수 있다. 이렇게 하면 절연형 DC/DC 컨버터가 최적의 효율로 동작할 수 있다. 가변 전압인데다 전력 흐름을 양방향으로 제어해야 한다는 점에서 디지털 제어가 필요하다. 와이드 밴드갭 전력 스위치는 역 복구 전하가 낮고 통상의 실리콘 MOSFET에 비해서 기생 커패시턴스가 낮다. 그러면서도 우수한 RDS(ON) 특성을 유지한다. 이 타입의 디바이스를 사용함으로써 전반적인 시스템 효율을 추가적으로 향상시킬 수 있다.

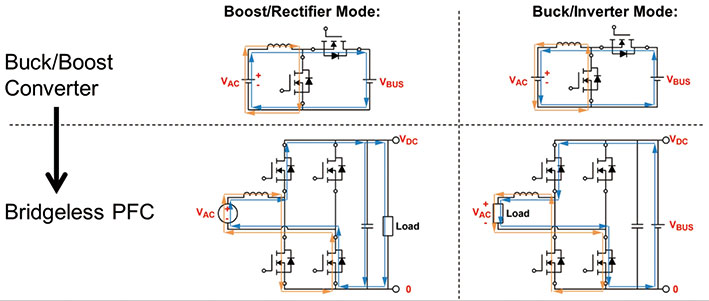

이번에는 이와 같은 디자인으로 적합한 토폴로지들을 알아본다. 본 고에서는 AC/DC 정류 스테이지로 단일 위상 AC 입력을 사용하는 것에 대해서만 다루도록 하겠다. 이 양방향 AC/DC 전원장치는 높은 전력을 제공하기 위한 것이므로, 무효 전력을 최소화하기 위해서 AC/DC 정류 스테이지로 높은 역률을 달성하도록 해야 한다. 또한 AC/DC 정류기와 절연형 DC/DC 컨버터 모두로 전도 손실을 최소화하기 위해서는 높은 출력 전압을 발생시켜야 한다. 그러므로 동적 PFC를 적용한 부스트 타입의 양방향 AC/DC 정류기가 필요하다. 이것들은 이러한 조건들을 충족하면서 널리 사용되는 세 가지 AC/DC 정류기 구성이다. 하나는 토템폴 브리지리스 PFC이고 이 둘은 양방향 스위치를 사용한 브리지리스 PFC이다(그림 2 참조).

[그림 2] 단일 위상 정류기/인버터

이러한 구성들로는 전통적인 다이오드를 MOSFET 같은 스위치로 교체해야 한다. 그래야 양방향 전류 흐름이 가능해진다. 브리지리스 PFC 구성이 복잡해 보일 수 있는데, AC 입력 사인파의 각기 하프 사이클로 나눠서 구성을 단순화해볼 수 있다. 양의 사이클일 때 에너지가 VAC에서 VBUS로 전송된다면 이 회로는 단순한 부스트 컨버터로 표현할 수 있다.

마찬가지로 에너지가 인버터 모드로 VBUS에서 VAC로 전송된다면 이 회로가 벅 컨버터처럼 동작한다. 이번에는 AC 입력의 음의 하프 사이클을 본다. 역시 마찬가지로 구성을 단순화할 수 있다. 정류기 모드일 때는 에너지가 VAC에서 VBUS로 흐르는데, 이 때는 공통 소스 부스트처럼 동작한다. 인버터 모드로 동작할 때는 벅 컨버터처럼 동작한다.

양방향 절연형 DC/DC 컨버터를 위해서는 듀얼 플라이백, 듀얼 Cuk, 포워드 플라이백, 듀얼 능동 브리지를 비롯한 다양한 토폴로지를 선택할 수 있다. 그런데 이들 대부분의 컨버터들이 트랜스포머나 결합 인덕터의 손실이나 크기 상의 이유 때문에 전력이 제한된다.

고전력 애플리케이션으로는 누설 에너지를 소산시키기 위해서 스너버 회로를 사용해야 하는 토폴로지는 피해야 한다. 또한 높은 효율을 유지하기 위해서는 소프트 스위칭이 필수이다. 이 두 요건을 모두 충족하는 유일한 토폴로지가 듀얼 능동 브리지(DAB) 컨버터이다.

듀얼 능동 브리지 컨버터는 다시 두 유형으로 구분할 수 있다. 위상 편이 DAB와 공진 DAB이다. 그러면 이들 각각의 구성이 어떻게 동작하는지 알아본다.

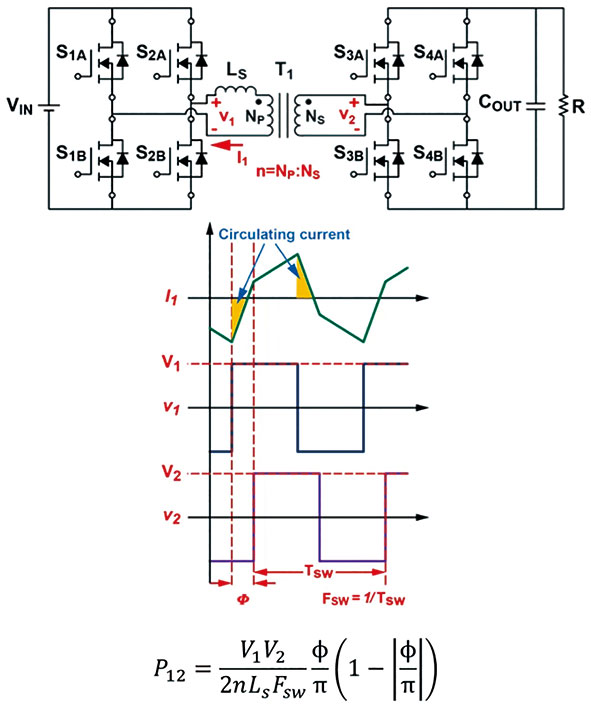

위상 편이 듀얼 능동 브리지는 일차 브리지와 이차 브리지로 50% 듀티 사이클로 트랜스포머로 전압을 인가해서 동작한다. 일차와 이차 사이에 위상 차를 변화시켜서 에너지 흐름을 제어한다. 그림 3 하단에서는 위상 편이 듀얼 능동 브리지의 주요 파형들을 볼 수 있다. 사각파 V1과 V2는 일차와 이차 브리지로 생성되어서 트랜스포머로 인가되는 전압들이다. 이 두 브리지 사이에 위상을 변화시킴으로써 직렬 인덕터 LS로 전압 차이를 인가한다. 그 아래에는 위상 편이 듀얼 능동 브리지의 전력 공식을 보여준다.

[그림 3] 위상 편이 듀얼 능동 브리지

위상 편이 DAB는 LS에 저장된 에너지를 사용해서 풀 브리지 스위치들의 커패시턴스를 충전하거나 방전해서 소프트 스위칭이나 제로 전압 스위칭(ZVS)을 달성한다. LS로 전류와 에너지는 부하 조건에 따라서 결정되므로, 부하가 경량이면 위상 편이 듀얼 능동 브리지가 ZVS 능력을 잃을 수 있다.

넓은 부하 범위에 걸쳐서 ZVS를 확장하기 위해서는 추가적인 외부적 직렬 인덕턴스를 사용할 수 있다. 그런데 또 이렇게 하면 중량 부하일 때 전도 손실에 영향을 미친다. 그러므로 ZVS 범위와 풀 부하 효율 간에 절충을 해야 한다.

일차와 이차 사이에 위상만 변화시킨다면 위상 편이 듀얼 능동 브리지 제어가 매우 단순할 수 있다. 이것을 단일 Φ 제어라고 한다. 하지만 이러한 단일 Φ 제어 위상 편이 듀얼 능동 브리지로는 다량의 순환하는 에너지가 발생된다. 이들 파형으로 순환 전류를 보실 수 있다. 그리고 이것은 전도 손실을 높인다.

이처럼 전도 손실이 높아지는 것을 극복하기 위해서 다중 위상 제어를 사용할 수 있다. 다시 말해서 일차와 이차 사이에 위상 편이만 제어하는 것이 아니라 각기 브리지의 레그도 제어하는 것이다. 이렇게 하려면 제어 알고리즘이 매우 복잡해진다.

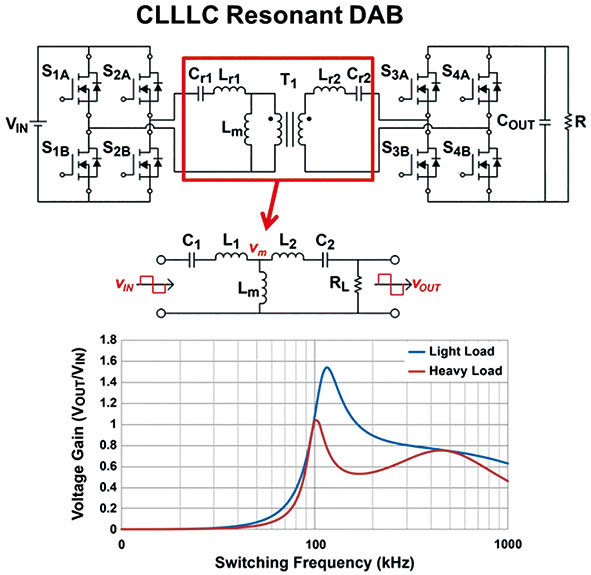

위상 편이 듀얼 능동 브리지와 달리, 공진 듀얼 능동 브리지는 가변 스위칭 주파수로 동작한다. 입력 풀 브리지가 사각파를 발생시키고 이것을 공진 탱크로 전달한다. 스위칭 주파수를 변화시킴으로써, 공진 탱크가 이득이 달라지게 되고 그러므로 탱크 회로의 출력 전압을 변화시킨다.

그림 4는 공진 듀얼 능동 브리지의 한 가지 타입으로서 CLLLC를 보여준다. 다시 말해서 3개 L을 사용한 직렬 공진 듀얼 능동 브리지이다. 공진 듀얼 능동 브리지로 다른 공진 탱크를 사용할 수도 있으며, 그러면 응답이 달라진다.

[그림 4] 공진 듀얼 능동 브리지

한 가지 중요한 점은, 공진 듀얼 능동 브리지를 이득 곡선이 음의 기울기가 되는 동작점으로 동작하도록 해야 한다는 것이다. 전압 이득 곡선이 음의 기울기이면 유도성 입력 임피던스가 된다. 이것은 입력 스위치가 제로 전압 스위칭(ZVS)을 달성하기 위해서 필요한 조건이다.

CLLLC는 직렬 공진 컨버터로서, 트랜스포머 자화 인덕턴스 Lm에 저장된 에너지를 사용해서 ZVS를 달성한다. 데드 타임 시에 Lm을 통해서 흐르는 최소한의 전류가 부하 조건에 대해서 종속적이지 않다. 그러므로 직렬 공진 DAB는 위상 편이 듀얼 능동 브리지처럼 효율을 절충할 필요 없이 전체적인 부하 범위에 걸쳐서 ZVS를 달성할 수 있다.

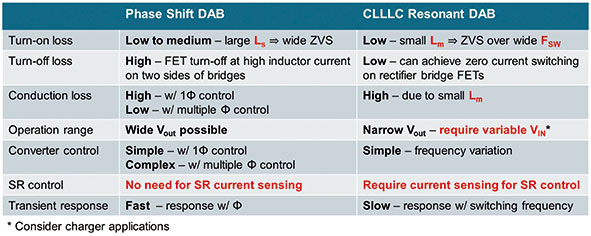

표 1에서는 위상 편이 듀얼 능동 브리지와 CLLLC 직렬 공진 듀얼 능동 브리지의 특징을 비교해서 보여준다. 먼저 위 두 줄은 스위칭 손실로서, 위상 편이보다는 공진 듀얼 능동 브리지에서 더 최소화할 수 있다. 또한 중요한 점은, 공진 회로로 스위칭 손실은 부하 조건에 종속적이지 않다는 것이다.

[표 1] 위상 편이 듀얼 능동 브리지와 CLLLC 직렬 공진 듀얼 능동 브리지의 특징

전도 손실은 두 컨버터 모두로 문제가 될 수 있다. 다만 위상 편이로 다중 Φ 제어를 사용하면 이 손실을 낮출 수 있다. 또 다른 중요한 절충 요소는 동작 범위이다. 위상 편이 구성은 넓은 출력 범위에 걸쳐서 동작할 수 있다. 그러므로 차저 애플리케이션의 경우에 입력 전압은 고정시키고 출력 전압은 배터리 전압에 따라서 변화될 수 있다.

공진 컨버터는 효율을 극대화하기 위해서 좁은 입력 대 출력 비로 동작해야 한다. 그러므로 차저 애플리케이션으로 효율을 높게 유지하기 위해서는 배터리 전압이 변화하는 것에 따라서 입력 전압이 변화되어야 한다. 동기 정류를 위한 메인 컨버터를 포함해서 제어 측면을 보면, 위상 편이는 단일 Φ 제어로 매우 단순하다. 공진 컨버터는 메인 제어는 단순하나, 복잡한 동기 정류기(SR) 제어를 필요로 한다.

또 다른 중요한 요소는 트랜션트 응답이다. 차저 애플리케이션의 경우에 트랜션트 응답은 그렇게 중요하지 않다. 하지만 제어 기법에 따라서 트랜션트 응답이 중요한 경우라면, 위상 편이가 응답이 훨씬 빠르다.

전력 스위치와 드라이버 선택

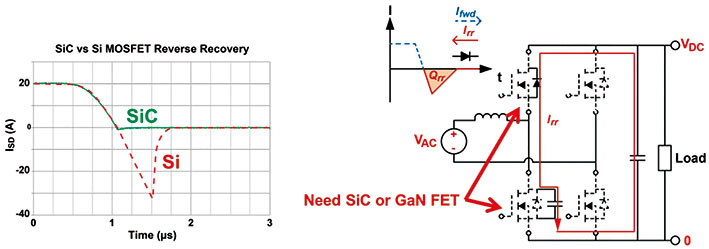

이번에는 이러한 애플리케이션들로 전력 스위치와 드라이버 선택에 대해서 알아보자. 전력 스위치와 드라이버는 전원장치로 높은 컨버터 효율을 달성하기 위해서 핵심적인 역할을 한다. 텔레콤 및 컨슈머 차저 애플리케이션에는 650V 정격의 실리콘 MOSFET이 널리 사용된다. 하지만 이 MOSFET은 역 복구 전하 Qrr이 높기 때문에 고전력 풀 브리지 정류기나 인버터 애플리케이션에는 거의 사용되지 않는다.

(a)

(b)

[그림 5] 정류기/인버터에서 SiC와 Si MOSFET 비교

그림 5a은 동급의 RDS(ON)으로 실리콘 MOSFET과 실리콘 카바이드 MOSFET의 역 복구를 비교해서 보여준다. 오른쪽 하단의 회로 다이어그램으로 실리콘 MOSFET을 사용하면, 하측 MOSFET이 턴온할 때 상측 MOSFET 바디 다이오드가 높은 역 복구 전류를 발생시킬 것이다. 그러면 하측 MOSFET으로 높은 스위칭 손실을 일으킨다.

음의 AC 사이클에도 마찬가지 상황이 발생된다. 심한 경우에는 높은 역 복구 전류로 인해서 MOSFET이 손상될 수도 있다. 그러므로 디바이스 바디 다이오드를 통해서 전류 전도를 필요로 하는 토템폴 브리지리스 PFC로는 Qrr이 낮거나 아예 제거하는 스위치를 선택해야 한다.

이러한 이유에서 하드 스위칭 정류기나 인버터에는 실리콘 MOSFET이 사용되지 않는다. 이러한 애플리케이션에는 실리콘 카바이드 MOSFET이나 GaN FET을 사용할 수 있다. 이번에는 DC/DC 컨버터로 필요한 스위치를 본다. PFC 스테이지와 달리 스위치들을 소프트 스위칭한다는 것을 알 수 있다.

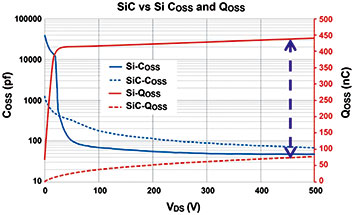

하드 턴온이나 역 복구를 하지 않으므로 정상 상태(steady state) 동작으로 실리콘 MOSFET을 안전하게 사용할 수 있다. 소프트 스위칭은 데드 타임 시에 인덕터와 MOSFET 출력 커패시턴스 COSS 사이의 공진 프로세스에 의해서 달성된다. COSS가 크면 더 많은 인덕터 에너지와 더 긴 데드 타임이 필요하다.

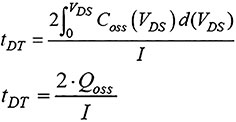

실리콘 FET이 COSS가 훨씬 높다는 것을 알 수 있다. ZVS를 달성하기 위해서 필요한 최소 데드 타임은 공식 1과 같이 계산할 수 있다. 그림 5b 하단의 그래프는 동급의 RDS(ON)으로 실리콘 MOSFET과 실리콘 카바이드 MOSFET의 COSS와 QOSS를 비교해서 보여준다.

(1)

(1)

COSS는 특성적으로 비선형적이므로, QOSS를 사용해서 COSS를 충전하기 위해서 필요한 전류와 시간을 계산할 수 있다. 400V로 실리콘 MOSFET의 QOSS가 실리콘 카바이드 MOSFET의 QOSS보다 거의 6배나 높다. 이 때문에 실리콘 FET은 실리콘 카바이드 FET에 비해서 데드 타임이 훨씬 길어야 한다.

실리콘 카바이드 FET을 사용하면, 컨버터로 듀티 사이클 손실을 낮추고, 비순환 전류를 낮추고, 전도 손실을 낮추고, 더 높은 스위칭 주파수로 동작할 수 있다. 실리콘 카바이드 MOSFET은 실리콘 MOSFET보다 훨씬 빠르게 스위칭하므로, 게이트 드라이버 디자인으로 몇 가지 추가적인 것들을 고려해야 한다(그림 6 참조).

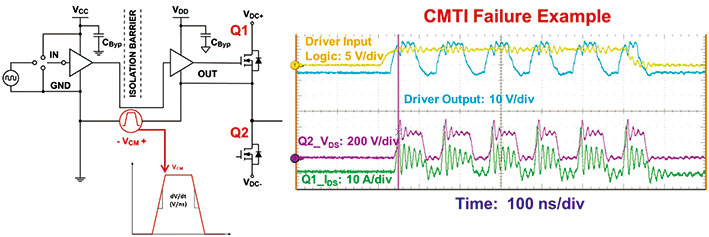

한 가지 주목할 점은, 실리콘 카바이드 디바이스는 경우에 따라서 1V에 이르기까지 게이트 임계가 낮다는 것이다. 이러한 이유에서 대부분의 실리콘 카바이드 게이트 드라이버는 게이트를 완전 오프 상태로 유지하기 위해서 음의 턴오프 전압을 사용한다. 실리콘 카바이드 MOSFET 드라이버 선택에 있어서 또 다른 중요한 파라미터는 공통 모드 트랜션트 내성(CMTI)이다.

브리지 구성으로 상측 디바이스로 플로팅 드라이버를 필요로 하므로, 통상적으로 이 드라이버를 절연을 해야 한다. 높은 dv/dt 스위칭 트랜션트가 상측 MOSFET 게이트 드라이버의 절연 벽으로 스트레스를 가한다.

그러므로 이 게이트 드라이버가 CMTI가 견고하지 않으면 dv/dt로 인해서 기생 잡음 전류가 발생되고 이로 인해서 펄스 소실, 과도한 전달 지연, 높거나 낮은 오차, 출력 래치 같은 드라이버 오동작을 일으킬 수 있다. 여기 보시는 이 파형은 공통 모드 전압 트랜션트 스트레스로 인한 드라이버 오동작을 보여준다.

[그림 6] SiC MOSFET 게이트 드라이버: CMTI 오동작 예

노란색으로 표시된 드라이버 입력 신호가 높아질 때 파란색의 드라이버 출력 전압이 로직 신호를 추종하지 못하고 보라색의 Q2 VDS 파형을 추종한다. 풀 브리지 구성에서는 다수의 스위치들이 어스나 안전 접지로 참조하지 않는다.

광학적 절연은 에폭시 절연 소재를 사용하고 절연 강도가 매우 낮다. 이러한 스위치들은 안전을 위해서 절연형 게이트 드라이버를 필요로 한다. 이 절연 기법에는 크게 세 가지를 들 수 있다. 광학적 절연, 자기 절연, 용량성 절연이다.

또한 속도가 느리고, 온도나 노후화에 따라서 성능이 저하되며, 대체로 신뢰성이 낮다. 자기 절연은 폴리이마이드 절연 소재를 사용하고, 절연 강도가 적당하다. 가장 큰 단점은 데이터 레이트에 비례하게 전력 소모가 증가한다는 점이다.

그러므로 높은 주파수로 스위칭하고자 한다면, 자기 절연은 너무 많은 전력을 필요로 할 것이다. 용량성 절연은 절연 강도가 가장 높고, 신뢰성과 견고성이 우수하다. 또한 산업용으로 수명이 가장 길어서 1.5kW 절연 전압으로 40년 이상의 수명이 가능하다. 또한 무엇보다도 데이트 레이트에 따라서 전력이 증가하지 않는다.

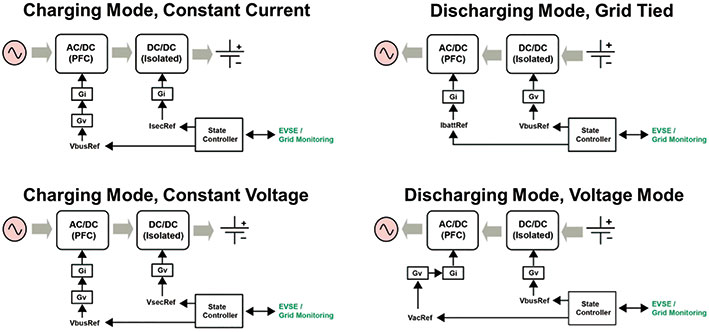

이번에는 컨트롤러 선택에 대해서 알아본다. 고전력 양방향 AC/DC 전원장치로 다수의 다양한 모드와 전원 스테이지를 구동하기 위해서는 디지털 컨트롤러가 필요하다. 이것은 전원장치가 처리해야 하는 4가지 동작 모드와 조건을 보여준다. 왼쪽의 두 사례는 전력이 AC 입력에서 배터리로 흐른다(그림 7 참조).

[그림 7] 양방향 모드 동작

위의 동작 모드는, AC/DC 스테이지는 중간적 전압을 제어해서 배터리 전압을 추종하고 DC/DC 스테이지는 출력 전류를 제어한다. 아래 동작 모드는, AC/DC는 고정적이고 DC/DC는 전류를 제어해서 출력 전압을 일정하게 한다. 오른쪽의 두 동작 모드는 에너지 흐름이 배터리에서 AC 소스 쪽으로 이루어진다. 위의 동작 모드는, AC가 전력망으로 연결되어 있다. 그러므로 전압과 주파수가 고정적이다. 그러므로 전원장치가 전류를 적절히 제어해야 한다. 아래 동작 모드는, AC가 전력망으로 연결되지 않았다.

그러므로 시스템이 출력 전압, 주파수, 전류도 레귤레이트해야 한다. 또한 모드 전환을 위해서 외부적 통신을 필요로 할 수 있다. 그러므로 디지털 컨트롤러가 적합한 선택이다. 펌웨어로 이러한 결정들을 손쉽게 구현할 수 있기 때문이다.

하지만 디지털 컨트롤러를 선택하기 위해서는 그에 따른 다수의 요인들을 고려해야 한다. PWM 기능, 아날로그-디지털 컨버터 통합, 제어 애플리케이션으로 CPU 성능 같은 것들을 들 수 있다. PWM은 전원장치의 핵심적인 부품이다. 갈수록 더 높은 스위칭 주파수를 추구함에 따라서 더 높은 정밀도가 요구되고 있다.

이것은 정밀도 확장 기능을 사용해서 달성할 수 있다. 전력 소모 문제 때문에 컨트롤러 주파수 자체는 높이기가 어렵기 때문이다. 이와 같은 정밀도 향상 기능과 관련해서 유의할 점은, 고분해능 듀티 사이클이 필요할 뿐만 아니라 고분해능 데드 타임과 고분해능 위상 편이 또한 필요하다는 것이다.

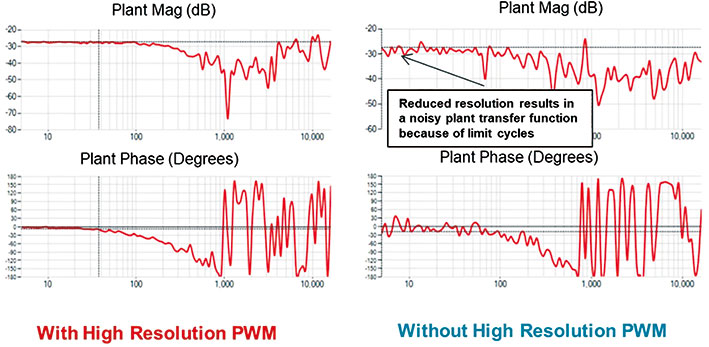

[그림 8] PWM 고려

그림 8은 고분해능 PWM을 사용하는 시스템과 사용하지 않는 시스템으로 플랜트 전달 함수 응답을 보여준다. 낮은 분해능은 플랜트 전달 함수로 추가적인 잡음으로 나타난다는 것을 알 수 있다. 이것은 정상 상태로 더 많은 잡음을 발생시킬 것이다. 검출 회로 또한 고려해야 한다.

여기서 다루고 있는 것과 같은 대부분의 고전력 애플리케이션으로 수백 볼트에 이르는 넓은 출력 전압 범위를 측정할 수 있어야 한다. 제어 수준을 유지하기 위해서는 ENOB(유효 비트 수)가 높은 ADC를 사용해야 한다. 시스템 요구를 충족하기 위해서 11 ENOB인 12비트 ADC를 흔히 사용한다. 또한 시스템으로 다수의 보호 기능이 필요하다. 이러한 것들로서 배터리 과전압과 공진 탱크 회로 과전류를 들 수 있다. 비교기와 DAC를 통합한 컨트롤러를 선택함으로써 이러한 기능들을 손쉽게 구현할 수 있다.

디자인 사례와 설계 고려사항

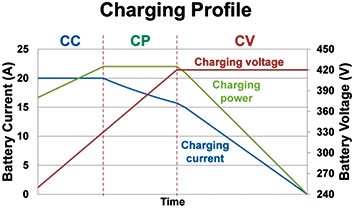

이번에는 고전력 양방향 온도브 차저의 디자인 사례와 설계 고려사항을 살펴본다. 이 디자인은 6.6kW 온보드 차저이다. 범용 AC 입력을 사용해서 400V 배터리를 충전한다. 출력 범위는 250V~450V이다. 배터리 전압이 낮을 때는 최대 20A의 정전류로 충전한다.

배터리 전압이 330VDC에 이르면, 6.6kW의 정전력으로 충전한다. 배터리 전압이 420V에 이르면, 정전압 레귤레이션으로 전환한다. 그림 9는 이 충전 프로파일을 보여준다. 또한 이 디자인은 배터리 전류 및 전압으로 5% 미만의 리플로 레귤레이션을 유지하고자 한다.

[그림 9] 충전 프로파일

이 디자인의 또 다른 중요한 목표는, 효율과 전력 밀도를 높게 유지하는 것이다. 60W/in3 이상의 전력 밀도와 96.5% 이상의 피크 효율을 목표로 한다. 96.5%의 피크 효율을 달성하기 위해서는 PFC 스테이지로 98.5% 및 DC/DC 스테이지로 98% 이상이 되어야 한다. 이것은 달성하기가 상당히 어려운 과제이다.

높은 효율과 높은 전력 밀도를 달성하기 위해서 이 디자인으로 토템폴 브리지리스 PFC와 공진 듀얼 능동 브리지를 선택하고 있다. 컨버터 효율을 끌어올리기 위해서 두 스테이지 모두로 고주파수 스위치로 실리콘 카바이드 MOSFET을 선택하고 있다. 또한 복잡한 양방향 제어와 통신을 처리하기 위해서 디지털 컨트롤러를 선택하고 있다.

전력 밀도가 높은 디자인으로 높은 신뢰성과 높은 견고성을 달성하도록 커패시티브 기반 절연형 드라이버를 선택하고 있다. 절연형 DC/DC 스테이지 효율을 극대화하기 위해서 PFC 출력 전압이 배터리 전압을 적응식으로 추종한다. 입력과 출력 전류 리플을 낮추기 위해서 인터리브 토템폴 브리지리스 PFC를 사용한다.

이번에는 인터리브 토템폴 브리지리스 PFC와 CLLLC 직렬 공진 듀얼 능동 브리지의 전원 스테이지 설계 고려사항을 살펴본다. 인터리브 PFC를 사용함으로써 컨버터 양쪽으로 전류 리플을 낮추고 각각의 전원 스테이지 디바이스들로 스트레스를 낮출 수 있다.

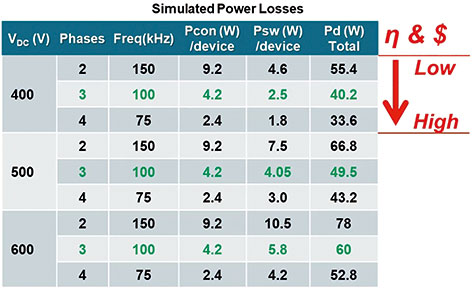

[표 2] 전력 손실 시험

또한 인터리브 구성은 경량 부하로 위상 셰딩 제어를 사용해서 효율을 추가적으로 향상시킬 수 있다. 표 2에서는 토템폴 브리지리스 PFC로 인터리브 위상 수에 따른 전력 손실을 보여준다. 동일한 300kHz 리플 주파수를 유지하기 위해서 각기 다른 위상 수에 따라서 스위칭 주파수가 변화된다.

위상 수가 증가하면 전력 소모가 감소한다는 것을 알 수 있다. 그 대신에 비용이 증가한다. 그러므로 BOM 비용과 효율 간에 절충을 해야 한다. 이 디자인으로 효율과 비용 요구를 조화시키기 위해서 3위상 인터리브 PFC를 선택하고 있다.

높은 전력 밀도와 높은 효율이라는 두 가지 목표를 모두 달성하기 위해서는 3개 L을 사용한 직렬 공진 듀얼 능동 브리지 컨버터로서 CLLLC를 높은 스위칭 주파수로 동작해야 한다. 직렬 공진 주파수가 스위칭 주파수와 같을 때 이 직렬 공진 컨버터의 효율을 극대화할 수 있다.

스위칭 주파수가 2개 직렬 공진 주파수 Fr1 및 Fr2와 같으면, 직렬 공진 임피던스가 0이다. 다시 말해서 입력 전압 대 출력 전압의 관계가 트랜스포머 권선비가 된다. PFC의 출력 전압을 380V부터 600V까지 가변적이도록 했으므로, 배터리 전압을 바탕으로 권선비를 계산할 수 있다.

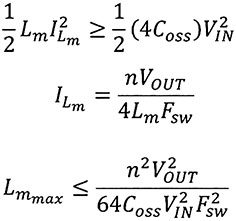

이 예의 경우에 권선비를 1.33:1로 선택한다. 그러면 285V부터 451V까지 배터리 전압 범위의 대부분을 지원할 수 있다. 285V 미만의 출력 전압은 주파수를 변경하거나 버스트 모드 동작을 사용해서 지원할 수 있다. 그 다음으로 결정해야 할 공진 탱크 파라미터는 Lm 자화 인덕턴스이다.

데드 타임 시에 Lm으로 저장된 에너지를 사용해서 FET의 COSS를 충전하거나 방전해서 제로 전압 스위칭을 달성한다. 계산을 단순화하기 위해서 트랜스포머와 출력 브리지가 이상적이라고 간주해 본다.

(2)

(2)

입력 풀 브리지로 제로 전압 스위칭을 달성하기 위해서는 Lm으로 저장되는 에너지가 모든 COSS로 저장되는 에너지보다 크도록 해야 한다. 이것을 보여주는 것이 공식 2의 첫 번째 공식이다. ILm은 피크 자화 전류로서, 두 번째 공식을 사용해서 계산할 수 있다.

첫 번째 공식과 두 번째 공식을 결합해서 허용 가능한 최대 Lm을 구할 수 있다. 이것이 세 번째 공식이다. Lm이 전류 공식의 분모에 있고 이것을 제곱하므로 첫 번째 공식에서의 부호를 ≥에서 ≤으로 바꿀 수 있다. 이렇게 해서 ZVS를 달성하기 위해서 허용 가능한 최대 인덕턴스를 구할 수 있다. 실제로는 트랜스포머 커패시턴스와 출력 브리지로부터의 COSS를 감안해서 Lm을 계산된 것보다 훨씬 낮게 선택해야 한다. 경험적 원칙으로서, Lm을 0.5Lm(max)보다 낮게 함으로써 ZVS를 달성하면서 순환 전류를 낮출 수 있다.

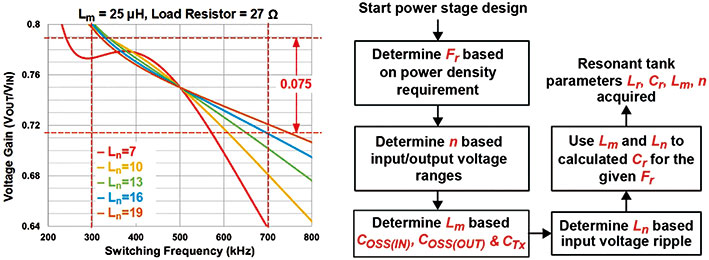

Lm을 결정한 다음에는 인덕턴스 비 Ln을 결정해야 한다. 이것은 Lm을 Lr로 나눈 것이다. Lr은 공진 인덕터이다. 인덕턴스 비는 스위칭 주파수가 변화될 때 이득에 영향을 미친다. 왼쪽 하단의 그림은 Fr1을 Fr2와 같도록 선택하고 이 둘을 500kHz로 설정했을 때 각기 다른 Ln 값으로 전압 이득 변화를 보여준다. 7부터 19까지의 Ln 값에 따라서 어떻게 변화되는지 알 수 있다(그림 10 참조).

[그림 10] CLLLC 공진 DAB 설계 고려

이 전압 이득 플롯을 보면, Ln이 작을수록 특정한 스위칭 주파수로 이득 변화가 크다는 것을 알 수 있다. 그러므로 낮은 Ln을 사용하면 더 넓은 입력 또는 출력 전압 변화를 지원할 수 있다는 뜻이 된다. 하지만 앞에서 살펴보았듯이, Ln을 작게 하기 위해서는 Lm은 작게 하고 Lr은 크게 해야 한다. 그러면 자화 인덕턴스가 작아짐으로써 더 높은 순환 전류가 발생되고 공진 인덕턴스가 커짐으로써 더 높은 전도 손실이 발생된다.

그러므로 효율과 동작 범위 간에 또 다른 절충을 해야 한다. 오른쪽의 플로우 차트를 보면, 공진 주파수를 500kHz로 선택하고 트랜스포머 권선비를 1.33:1로 선택함으로써 이 중의 두 단계는 이미 완수했다는 것을 알 수 있다.

또한 앞에서 Lm도 계산했다. 이 디자인의 목표 사양에 따라서 25μH로 계산된다. Ln으로 넘어가서, PFC 출력 전압으로 5% 리플을 유지하기 위해서는 이득 변화가 최소한 0.075여야 한다. 그러므로 약간의 여유를 두고 이와 같은 요구를 충족하는 가장 높은 값의 Ln을 선택한다.

그러므로 이 경우에는 Ln = 13을 선택한다. 이들 파라미터를 계산한 다음에는, 공진 커패시터 Cr1 및 Cr2를 계산할 수 있다. 이제 모든 공진 탱크 파라미터를 선택했다. 그런데 이것은 한 방향으로 전류 흐름에 대한 것이다.

그러므로 반대 방향으로 전류 흐름에 대해서 이 플로우 차트의 마지막 세 단계를 반복해야 한다. 그렇게 계산해서 Ln이 앞서 계산한 것보다 작으면, 두 Ln 값 중에서 작은 것을 사용한다. 그래야 모드 스위치들로 양쪽 방향으로 ZVS를 보장할 수 있다. 듀얼 능동 브리지 같은 직렬 공진 컨버터로 까다로운 과제가 동기 정류기 제어이다. 이 디자인은 에너지 흐름이 양쪽 방향으로 이루어지므로 제어가 특히 더 복잡한다. 정류된 전류의 전도 지속시간은 부하와 동작 주파수에 따라서 달라진다.

스위칭 주파수가 직렬 공진 주파수보다 낮으면, 입력 스위치가 턴오프하기 전에 정류 전류가 0이 된다. 그러므로 FET이 정류기로 동작한다면, 전류가 역으로 흐르는 것을 피하기 위해서 50% 미만의 듀티 사이클로 턴오프해야 한다. 중량 부하일 때 정류 전류 전도 시간은 직렬 공진 간격의 절반이다. 그러므로 중량 부하일 때는 SR 전도 시간을 직렬 공진 간격보다 약간 짧게 제한하고 경량 부하일 때는 SR 기능을 끌 수 있다.

이러한 개방 루프 타입의 제어 기법은 컨버터 효율을 극대화하지 못한다. 하지만 구현하기가 단순한다. MOSFET 드레인-소스 전압 검출, 전류 트랜스포머, 홀 센서 같은 SR 검출 방법들은 모두가 대체로 400kHz 미만으로 주파수가 제한된다. 그러므로 다른 기법이 필요하다.

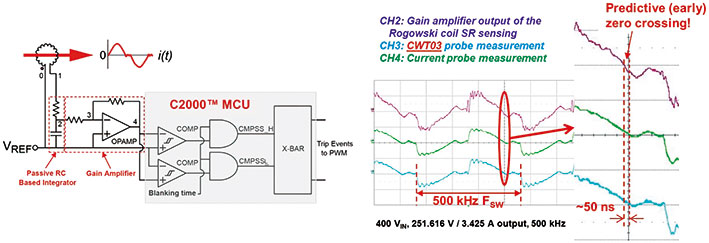

[그림 11] SR 검출 및 제어 기법

그림 11은 로고스키 코일 기반 SR 검출 및 제어 기법을 제안하고 있다. 트랜스포머 권선으로 에어 코어 코일을 탑재해서 전류 검출을 한다. 이 코일로 시간 가변 전류가 흐를 때 이 전류가 발생시키는 자기장이 코일 권선으로 전압을 유도한다. 이 유도 전압은 원래의 시간 가변 전류와 비교해서 90° 위상 편이가 될 것이다.

그리고 로고스키 코일 다음에 적분기를 추가하면, 원래의 시간 가변 전류와 위상이 일치하는 혹은 선행하는 전압을 발생시킬 수 있다. 그러므로 지연을 고려해서 적분기 출력의 제로 전압 크로싱이 시간 가변 전류의 제로 전류 크로싱 이벤트보다 약간 더 일찍 일어나도록 설정할 수 있다.

오른쪽 그림에서 보라색은 증폭기 파형이고, 녹색은 트랜스포머 권선 전류 파형이고, 파란색은 전류 프로브 측정이다. 검출 전류가 실제 측정과 거의 일치한다는 것을 알 수 있다. 이번에는 하드웨어를 사용한 실제 테스트 결과를 살펴본다. 성능 평가를 위해서 2개 프로토타입으로서 6.6kW 인터리브 토템폴 브리지리스 PFC와 6.6kW CLLLC 공진 듀얼 능동 브리지 컨버터를 제작했다.

각기 스테이지를 편리하게 평가하기 위해서 각각의 프로토타입으로 각기 마이크로컨트롤러를 사용하고 있다. 인터리브 토템폴 브리지리스 PFC는 92W/in3의 전력 밀도를 달성하고, CLLLC 직렬 공진 듀얼 능동 브리지는 76W/in3의 전력 밀도를 달성한다.

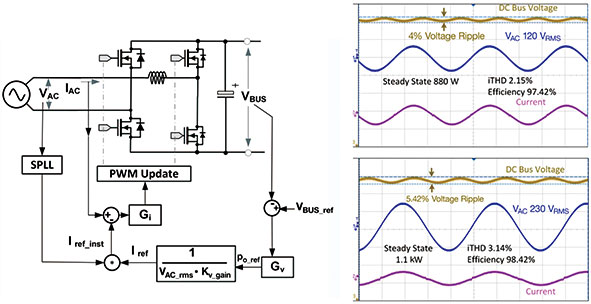

[그림 12] PFC의 제어 블록 다이어그램

그림 12에서 왼쪽은 정류기 모드로 PFC의 제어 블록 다이어그램을 보여준다. 이 때는 에너지가 AC에서 버스 전압으로 흐른다. 오른쪽의 파형은 경량 부하로 로우 라인과 하이 라인 동작을 보여준다. 양쪽 모두로 효율과 THD가 우수하다는 것을 알 수 있다. 전력망 연결 인버터 모드로는 에너지가 전압 버스에서 AC 전력망으로 거꾸로 흐른다.

전력망 전압은 고정적이므로, 레귤레이션 제어를 위해서 AC 전류만 사용할 수 있다. 역률은 거의 1에 가깝다. 그리고 경량 부하로도 THD가 낮다. 왼쪽 그림의 스코프 화면은 단일 위상에서 3위상으로 전환하는 것을 보여준다.

전력 수준이 단일 위상 수준에서 3위상 수준으로 상승한다. 대략적으로 1kW에서 5kW로 상승한다. 이 플롯에서는 60Hz 주파수를 보여준다. 컨버터가 단일 위상 동작에서 3위상 동작으로 전환함으로써 고주파 전류 리플이 감소된다. 오른쪽은 위상 셰딩을 적용했을 때와 적용하지 않았을 때 토템폴 브리지리스 PFC의 효율 측정을 보여준다.

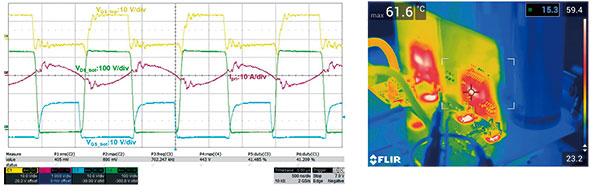

[그림 13] 실리콘 카바이드 MOSFET 드라이버 성능

그림 13에서는 실리콘 카바이드 MOSFET 드라이버 성능을 보여준다. 왼쪽의 파형은 UCC21530-Q1 게이트 드라이버를 700kHz로 ZVS 조건으로 동작하는 것을 보여준다. 채널 1과 채널 3은 상측 및 하측 MOSFET VGS 파형이다. 채널 2는 공진 탱크 전류이고, 채널 4는 스위칭 전압이다.

이 드라이버는 최대 전달 지연이 19ns 미만이다. 그리고 여기서는 6ns 미만의 지연이 관찰된다. 그러므로 매우 짧은 데드타임 설정이 가능하다. 오른쪽의 열 영상을 보면, 이 게이트 드라이버로 700kHz 스위칭 주파수로 온도 상승이 40℃ 미만이라는 것을 알 수 있다.

지금까지 말씀드린 것들을 다시 한 번 요약해 본다. 2스테이지 접근법을 사용해서 높은 컨버터 효율, 높은 전력 밀도, 접지 결함에 대한 높은 내성을 달성한다는 것을 살펴보았다.

AC/DC 정류기 스테이지로 토템폴 브리지리스 PFC와 절연형 DC/DC 스테이지로 CLLLC 직렬 공진 듀얼 능동 브리지 컨버터를 사용한 6.6kW 온보드 차저 디자인의 설계 과정을 설명했고 어떻게 부품을 선택하고 적합한 부품 값을 사용할지 알아 보았다.

기사입력 : 2020-11-02

전기차 시스템 혁신을 이끄는 GaN 기술

작성자 :

자동차 인포테인먼트 클러스터 시스템 구동

작성자 : Timothy Hegarty

절연 기술 개발과 고전압 설계 문제의 해결

작성자 : Krunal Maniar

AEC-Q100 MSPM0 MCU를 사용하여 오토모티브 차체 전자 장치 설계 최적화

작성자 : Henok Taffere

정밀 ADC로 전기차 충전기 계측

작성자 : Jiyah Starks

절연형 DC/DC 바이어스 전원 솔루션

작성자 : Taxas Instruments

옵토커플러를 업그레이드하자

작성자 : 김태호

급성장하는 HEV/EV 시장에서 오토모티브 HVAC 설계를 최적화하는 방법

작성자 : Osamah Ahmad 외 1인

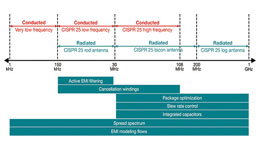

전원 공급 장치의 EMI 절감을 위한 시간 및 비용 효율적 혁신

작성자 : Yogesh Ramadass 외 2인

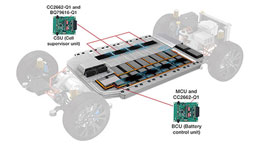

EV 채택을 증가시키는 배터리 관리 시스템의 혁신

작성자 : Issac Hsu