# 연산 증폭기에서 잡음을 낮추기 위한 설계 도움말

Designing with Op Amps for Low Noise

잡음은 기본적인 물리적 특성이면서 제한적인 요인으로 작용한다. 센서 신호를 처리할 때 잡음으로 인한 영향을 최소화하기 위해서는 신중하게 적합한 연산 증폭기를 선택하고, 입력 저항을 최소화 및 매칭시키고, 디자인의 물리적 레이아웃에 주의를 기울여야 한다.

글/Brian Black, Product Marketing Manager, Signal Conditioning Products, Glen Brisebois, Senior Applications Engineer, Signal Conditioning Products, Linear Technology

> ▲ 】제적인 물리적 성질 때문에 정밀도, 제로 잡음, 무 **근** 한한 개방 루프 이득, 슬루율, 이득-대역폭 곱이 완벽한 이상적인 연산 증폭기를 달성한다는 것은 불가 능하다. 하지만 증폭기 제품이 세대를 거듭할수록 이전 제품보다 나아지고 있다는 것은 확실하다. 그렇다면 1/ f 잡음이 낮은 연산 증폭기를 설계하려면 어떻게 해야 할 것인가?

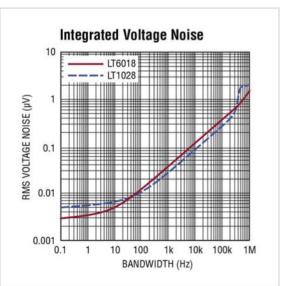

> 1985년에 Linear Technology의 George Erdi가 LT1028을 설계하였다. LT1028은 1kHz일 때 0,85nV/ √Hz의 입력 전압 잡음 밀도와 35nVp-p의 0,1Hz~10Hz 입력 전압 잡음으로서 30년 넘게 저주파수에서 전압 잡음이 가장 낮은 연산 증폭기로 남아 있다. 그런데 올 해 LT6018이라고 하는 새로운 증폭기가 등장함으로써 LT1028에 도전장을 내게 되었다. LT6018은 30nV<sub>P-P</sub>의 0.1Hz~10Hz 입력 전압 잡음과 1Hz의 1/f 코너 주파수 를 달성한다. 다만 광대역 주파수의 특성은 1.2nV/√Hz 이다. 그럼으로써 LT6018은 저주파 애플리케이션에서

LT6018은 저주파 애플리케이션에서 더 낮은 잡음을 가능하게 하며, LT1028은 많은 광대역 애플리케이션에서 우수한 성능을 달성한다.

The realities of physics prevent us from attaining the L ideal op amp with perfect precision, zero noise, infinite open-loop gain, slew rate, and gain-bandwidth product. But we expect successive generations of amplifiers to be better than the previous. What then to make of low 1/f noise op amps?

Back in 1985, George Erdi of Linear Technology

그림 1. LT1028과 LT6018의 적분 전압 잡음

더 낮은 잡음을 가능하게 하며, LT1028은 많은 광대역 애플리케이션에서 우수한 성능을 달성한다(그림 1).

### 잡음 요인

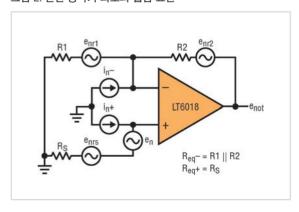

하지만 잡음이 낮은 회로를 설계하기 위해서는 특정 주파수 대역으로 전압 잡음 밀도(e<sub>n</sub>)가 낮은 증폭기를 선 택하는 것만이 중요한 것이 아니다. **그림 2**에서 보는 것 처럼 다른 잡음 요인들 또한 고려해야 한다. 비응집성 (incoherent) 요인들이 RSS(제곱 합의 제곱근)로 결합하 기 때문이다.

첫째, 잡음 요인으로서 저항을 고려해야 한다. 저항은 기본적으로 저항 값의 제곱근에 비례하게 잡음을 발생시킨다. 300K의 온도일 때 어떠한 저항의 전압 잡음 밀도는  $e_n=0.13\sqrt{R}$   $nV/\sqrt{Hz}$ 이다. 이 잡음은 노튼(Norton) 등가 전류 잡음  $i_n=e_n/R=0.13/\sqrt{R}$   $nA/\sqrt{Hz}$ 으로도 볼 수 있다. 그러므로 저항은 잡음 전력이 17젭토와트 (zeptoWatt)이다. 우수한 연산 증폭기가 되려면 이보다 더 낮은 잡음 전력이어야 한다. 예를 들어서 LT6018의 잡음 전력(1kHz일 때)은 약 1젭토와트이다.

그림 2의 연산 증폭기 회로에서는 소스 저항( $R_s$ ), 이 득 저항( $R_1$ ), 피드백 저항( $R_2$ ) 모두가 회로 잡음에 기여한다. 잡음을 계산할 때는 전압 잡음 밀도에 사용되는 'per root Hertz'는 혼란을 초래할 수 있다. 하지만 잡음 전력은 함께 더하는 것이지 잡음 전압이 아니다. 그러

그림 2. 연산 증폭기 회로의 잡음 요인

designed the LT1028. For over 30 years, it has remained the lowest voltage noise op amp available at low frequency with  $0.85 \text{nV}/\sqrt{\text{Hz}}$  input voltage noise density at 1kHz and  $35 \text{nV}_{P-P}$  0.1Hz to 10Hz input voltage noise. It wasn't until this year that a new amplifier, the LT6018 challenged the LT1028's position with 0.1Hz to 10Hz input voltage noise of  $30 \text{nV}_{P-P}$  and a 1Hz 1/f corner frequency, although it's wideband frequency is  $1.2 \text{nV}/\sqrt{\text{Hz}}$ . The result is that the LT6018 is the lower noise choice for lower frequency applications, while the LT1028 provides better performance for many wideband applications, as shown in Figure 1.

## A Noisy Noise Annoys

But there is more to designing low noise circuits than choosing the lowest voltage noise density  $(e_n)$  amplifier for a given frequency band. As shown in Figure 2, other noise sources come into play, with incoherent sources combining as a root sum of squares.

First, consider resistors as noise sources. Resistors inherently have noise, proportional to the square root of the resistance value. At a temperature of 300K, the voltage noise density of any resistor is  $e_n = 0.13 \sqrt{R} \text{ nV}/\sqrt{Hz}$ . This noise can also be considered as a Norton equivalent current noise:  $i_n = e_n/R = 0.13/\sqrt{R} \text{ nA}/\sqrt{Hz}$ . Resistors therefore have a noise power of 17 zeptoWatts. Good op amps will have lower noise power than this. For example, the LT6018 noise power (measured at 1KHz) is about 1 zeptoWatt.

In the op amp circuit of Figure 2, the source resistance, gain resistor, and feedback resistor (RS, R<sub>1</sub>, and R<sub>2</sub> respectively) all contribute to the circuit noise. When calculating noise, the "per root Hertz" used in voltage noise density can be confusing. But noise power is what adds together, not noise voltage. So

므로 저항이나 연산 증폭기의 적분 전압 잡음을 계산하 기 위해서는 전압 잡음 밀도를 주파수 대역의 헤르츠 수 의 제곱근으로 곱해야 한다. 예를 들어서  $100\Omega$  저항은 1MHz 대역폭에 걸쳐서 1.3μV RMS 잡음이다(0.13nV/  $\sqrt{\Omega} * \sqrt{100\Omega} * \sqrt{1,000,000 \text{Hz}}$ ). 브릭 월 필터가 아니라 일차 필터를 사용하는 회로에서는 더 높은 대역폭 스커 트로 잡음을 포착하기 위해서 이 대역폭에 1.57을 곱한 다. 또한 잡음을 RMS가 아니라 피크-대-피크로 표현하 기 위해서는 6을 곱한다(사인파에서 같은 2.8이 아니고). 이렇게 하면 이  $100\Omega$  저항의 잡음은 단순한 1MHz 저 역통과 필터를 사용할 때 9.8μV<sub>P-P</sub>에 근접한다.

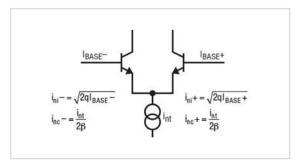

또한 연산 증폭기는 양쪽 입력 in- 및 in+로 들어오고 나가는 전류와 관련해서 입력 전류 잡음을 발생시킨다. 여기에다 각자의 저항(in-의 경우에는 병렬인 R<sub>1</sub>과 R<sub>2</sub>, i,,의 경우에는 Rs)을 곱하면 옴의 법칙에 따른 전압 잡음 을 구할 수 있다. 증폭기 내부를 들여다 보면(그림 3) 이 전류 잡음은 다수의 요인들로 이루어진다는 것을 알 수 있다.

광대역 잡음을 살펴보면, 2개 입력 트랜지스터 각각 이 자신의 베이스 i,,, 및 i,,,와 관련해서 샷 잡음을 갖는 데, 이 잡음은 응집성이 아니다. 입력 쌍 테일 i...의 전류 소스로부터의 잡음이 또한 2개 입력 사이에 분할되는 응 집성 잡음을 발생시킨다(각각으로 i,,/28). 2개 입력 상 의 저항이 동일하다면 각 입력의 응집성 전압 잡음 역 시 동일하고 증폭기의 동상 모드 제거(common mode rejection) 능력에 따라서 제거될 것이므로 주로 비응집 성 잡음을 남길 것이다. 이것을 데이터 시트에서는 평형

그림 3. 연산 증폭기 차동 쌍에서 응집성 및 비응집성 잡음 요인

to calculate the integrated voltage noise of a resistor or op amp, multiply the voltage noise density by the square root of the number of Hertz in the frequency band. For example, a  $100\Omega$  resistor has  $1.3\mu V$  RMS noise over a 1MHz bandwidth  $(0.13 \text{nV}/\sqrt{\Omega} * \sqrt{100\Omega})$ \* $\sqrt{1.000.000Hz}$ ). For a circuit with a first order rather than brick wall filter, the bandwidth would be multiplied by 1.57 to capture the noise in the higher bandwidth skirt. To express the noise as peak-to-peak rather than RMS, multiply by a factor of 6 (not 2.8, as you would for a sinusoid). With these considerations, the noise of this  $100\Omega$  resistor with a simple 1MHz low-pass filter is closer to 9.8µV<sub>P-P</sub>.

Also, the op amp has input current noise associated with the current into or out of each input, i<sub>n-</sub> and i<sub>n+</sub>. These multiply by the resistances they work into, R<sub>1</sub> in parallel with R<sub>2</sub> in the case of in- and R<sub>5</sub> in the case of int to create voltage noise through the magic of Ohm's law. Looking inside the amplifier (Figure 3), this current noise is comprised of multiple sources.

Considering the wideband noise, each of the two input transistors have shot noise associated with their base,  $i_{ni-}$  and  $i_{ni+}$ , which are not coherent. The noise from the current source in the input pair tail, int also creates coherent noise split between the two inputs  $(i_{nr}/2\beta$  in each). If the resistance seen by the two inputs is equal, the coherent voltage noise at each input is also equal and cancels according to the amplifier's common mode rejection capability, leaving primarily the incoherent noise. This is listed as the balanced current noise in data sheets. If the resistance seen at the two inputs is greatly mismatched, then the coherent and incoherent noise components remain and the voltage noise adds as the root sum of squares. This is listed in some data sheets as unbalanced noise current.

(balanced) 전류 잡음으로 표기한다. 2개 입력 상의 저항이 크게 불일치하면 응집성 및 비응집성 잡음 성분이 그대로 남아 있고, 전압 잡음이 RSS(제곱 합의 제곱근)로 더해질 것이다. 이것을 일부 데이터 시트에서는 비평형 (unbalanced) 잡음 전류로 표기한다.

LT1028과 LT6018은 둘 다 100Ω 저항(실온일 때 1.3nV√Hz)보다 전압 잡음이 낮다. 그러므로 소스 저항이 이보다 높으면 연산 증폭기의 전압 잡음이 회로의 잡음에 있어서 제한적 요인이 되지 않을 것이다. 소스 저항이 이보다 훨씬 낮을 때는 증폭기의 전압 잡음이 지배적 요인이 되기 시작할 것이다. 소스 저항이 아주 높으면 증폭기의 전류 잡음이 지배적 요인이며, 중간일 때는 저항의 존슨 잡음이 지배적 요인이면, 중간일 때는 저항의 존슨 잡음이 지배적 요인이 된다(잡음 전력이 과도하게 높지 않은 잘 설계된 연산 증폭기일 경우에). 증폭기전류 잡음과 전압 잡음이 평형을 이루어서 어느 것도 지배적 요인이 되지 않는 저항은 증폭기의 전압 잡음을 전류 잡음으로 나는 것에 해당된다. 전압과 전류 잡음은 주파수에 따라서 변화하므로 이러한 중간 저항 또한 변화한다. 비평형 소스일 경우에 10Hz일 때 LT6018의 중간점은 약 86Ω이다. 10kHz일 때는 약 320Ω이다.

#### 회로 잡음 최소화

그렇다면 설계 엔지니어가 잡음을 최소화하려면 어떻게 해야 할 것인가? 전압 신호를 처리하기 위해서는 등가 저항을 증폭기의 중간 저항 아래로 낮추는 것에서 시작하는 것이 좋다. 많은 애플리케이션에서 소스 저항은 흔히 센서인 전위 스테이지에 의해서 고정적이다. 그러므로 이득 및 피드백 저항을 작게 선택할 수 있다. 하지만 피드백 저항은 연산 증폭기 부하의 일부분을 이루므로 증폭기의 출력 구동 능력과 허용 가능한 열 및 전력소모에 따라서 선택에 제한이 있다. 입력 상의 저항뿐만 아니라 주파수 또한 고려해야 한다. 총 잡음은 전체 주파수에 걸쳐서 잡음 밀도를 적분하는 것으로 이루어지기때문이다. 또한 신호 대역폭보다 높은 주파수로의 잡음을 필터링하는 것이 중요하다(경우에 따라서는 신호 대

Both the LT1028 and LT6018 have lower voltage noise than a  $100\Omega$  resistor (which at room temperature is 1.3 nV//Hz), so where source resistances are higher, the op amp's voltage noise will often not be the limiting factor for noise in the circuit. In cases where the source resistances are much lower, the amplifier's voltage noise will begin to dominate. For very high source resistances, the amplifier's current noise dominates, and in the middle the Johnson noise of the resistors dominates (for well designed op amps which do not have excessively high noise power). The resistance at which the amplifier current noise and voltage noise are balanced so that neither dominates is equal to the amplifier's voltage noise divided by its current noise. Since voltage and current noise vary with frequency so too does this midpoint resistance. For an unbalanced source, at 10Hz the midpoint of LT6018 is approximately  $86\Omega$ ; at 10kHz it is about  $320\Omega$ .

#### **Minimizing Circuit Noise**

So what is the design engineer to do to minimize noise? For processing voltage signals, reducing the equivalent resistance below the amplifier's midpoint resistance is a good place to start. For many applications the source resistance is fixed by the preceding stage, often a sensor. The gain and feedback resistors can be chosen to be small. However since the feedback resistor forms part of the op amp load, there are limits due to the amplifier's output drive capability and the acceptable amount of heat and power dissipation. In addition to the resistance seen by the inputs, the frequency should also be considered. The total noise consists of the noise density integrated over the entire frequency. Filtering noise at frequencies higher (and perhaps also lower) than the signal bandwidth is

역폭보다 낮은 주파수에 대해서도 이렇게 해야 한다).

증폭기로의 입력이 전류인 트랜스임피던스 애플리케이션에서는 다른 전략을 필요로 한다. 이 경우에는 피드백 저항의 존슨 잡음이 저항 값의 제곱근으로 증가하며, 동시에 신호 이득 증가는 저항 값에 따라서 선형적이다. 그러므로 연산 증폭기가 허용하는 전압 용량이나 전류잡음만큼의 저항을 사용함으로써 최상의 SNR을 달성할수 있다. 이와 관련한 예로서 LTC6090 데이터 시트 26페이지의 애플리케이션에서 그러한 경우를 볼 수 있다.

# 잡음 및 기타 문제

잡음은 오차의 한 요인일 뿐이며 그 외에도 많은 오 차 요인들을 고려해야 한다. 입력 오프셋 전압(연산 증 폭기 입력 상의 전압 불일치)은 DC 전압으로 생각할 수 있다. 시스템 캘리브레이션을 실시함으로써 이 영향을 크게 줄일 수 있으나, 이러한 오프셋 전압은 기계적 스 트레스 때문에 온도와 시간에 따라서 변화한다. 입력 레 벨(CMRR)과 전원장치(PSRR)에 따라서도 변화한다. 이러한 변수들로 인한 드리프트를 제거하기 위한 실시 간 시스템 캘리브레이션을 하려면 비용이 급격히 상승 하므로 실용적이지 않다. 온도가 크게 변동적인 혹독 한 환경의 애플리케이션에서는 오프셋 전압과 드리프 트로 인한 측정 불확정도가 잡음보다 지배적일 수 있 다. 예를 들어서 온도 드리프트가 5μV/℃인 연산 증폭 기는 온도 드리프트 때문만으로 -40℃에서 85℃에 걸 쳐서 625μV의 입력 참조 변동을 겪을 수 있다. 이와 비 교해서 수백 나노볼트의 잡음은 시시한 것이다. LT6018 은 0.5μV/℃의 뛰어난 드리프트 성능과 -40°C~85°C 로 80μV의 최대 오프셋 사양을 제공한다. 더 우수한 성 능을 원하는 경우에는 최근에 출시된 LTC2057 오토 제

잡음은 오차의 한 요인일 뿐이며 그 외에도 많은 오차 요인들을 고려해야 한다. 입력 오프셋 전압은 DC 전압으로 생각할 수 있다. important.

In transimpedance applications, where the input to the amplifier is a current, a different strategy is needed. In this case, the Johnson noise of the feedback resistor increases as a square root factor of its resistance value, but at the same time the signal gain increase is linear with the resistance value. Hence the best SNR is achieved with as large a resistance as the voltage capability or the current noise of the op amp allows. For an interesting example, see the back page application on page 26 of the LTC6090 data sheet.

## **Noise and Other Headaches**

Noise is just one source of error, and should be considered within the context of other error sources. Input offset voltage (the voltage mismatch at the op amp inputs) can be thought of as DC noise. Its impact can be reduced significantly by doing a onetime system calibration, but this offset voltage changes with temperature and time as a result of changes in mechanical stress. It also changes with input level (CMRR) and power supply (PSRR). Real-time system calibration to cancel drift caused by these variables quickly becomes expensive and impractical. For harsh environment applications where the temperature fluctuates considerably, measurement uncertainty due to offset voltage and drift can dominate over noise. For example, an op amp with  $5\mu V/^{\circ}C$  temperature drift can experience an input-referred shift of 625µV from -40°C to 85°C due to temperature drift alone. Compared with this, a few hundred nanovolts of noise is inconsequential. The LT6018 has outstanding drift performance of 0.5µV/°C and a maximum offset spec of 80µV from −40°C to 85°C. For even better performance, the recently released LTC2057 auto-zero

로 증폭기 제품이 -40℃~125℃로 7µV 미만의 최대 오 프셋 전압을 제공한다. 또한 LTC2057은 광대역 잡음은 11nV/√Hz이고 DC~10Hz 잡음은 200nV<sub>P-P</sub>이다. 이것은 LT6018보다 더 높은 잡음인데, 저주파수 애플리케이션에서는 경우에 따라서 LTC2057이 더 우수한 선택일수 있다. LTC2057은 온도에 대해서 입력 오프셋 드리프트가 뛰어나기 때문이다. 또 한 가지 특기할 만한 점은, LTC2057은 입력 바이어스 전류가 낮기 때문에 LT6018보다 전류 잡음이 훨씬 낮다는 것이다. LTC2057의 낮은 입력 바이어스 전류의 또 다른 이점은 다른 많은 제로 드리프트 증폭기와 비교해서 클록 피드쓰루(clock feedthrough)가 매우 낮다는 것이다. 이러한 다른 제로드리프트 증폭기는 소스 임피던스가 높을 때 높은 전압잡음 스퍼를 나타낼 수 있다.

이러한 고정밀 회로에서는 또한 열전대(thermocouple) 효과를 최소화하도록 주의를 기울여야 한다. 열전대 효과는 상이한 금속이 접합하는 어느 부위에서나 발생될 수 있다. 서로 다른 회사에서 만든 2개 구리선을 접합하는 것만으로도 200nV/℃의 열 EMF를 발생시킬 수 있다. 이것은 LTC2057의 최악 상황 드리프트보다도 13배 이상 높은 것이다. 그러므로 이러한 고정밀 회로에서는 증폭기 입력 신호 경로 상에서 접합부 수를 최소화하고, 접합부를 서로 근접하게 매칭시키고, 열 경사 (thermal gradient)를 피하기 위한 레이아웃 기법들을 사용해야 한다.

## 맺음말

잡음은 기본적인 물리적 특성이면서 제한적인 요인으로 작용한다. 센서 신호를 처리할 때 잡음으로 인한 영향을 최소화하기 위해서는 신중하게 적합한 연산 증폭기를 선택하고, 입력 저항을 최소화 및 매칭시키고, 디자인의 물리적 레이아웃에 주의를 기울여야 한다. ₩

amplifier has a maximum offset voltage of less than  $7\mu V$  from  $-40^{\circ}C$  to  $125^{\circ}C$ . Its wideband noise of  $11nV/\sqrt{Hz}$ , and its DC to 10Hz noise is  $200nV_{P-P}$ . While this is higher noise than the LT6018, the LTC2057 can sometimes be the better choice for low frequency applications due to its outstanding input offset drift over temperature. It is also worth noting that due to its low input bias current, the LT2057 has much lower current noise than the LT6018. Another benefit of the LTC2057 low input bias current is that it has very low clock feedthrough compared with many other zero-drift amplifiers. Some of these other zero-drift amplifiers can exhibit large voltage noise spurs when source impedance is high.

In such high precision circuits, care must also be taken to minimize thermocouple effects, which occur anywhere that there is a junction of dissimilar metals. Even junctions of two copper wires from different manufacturers can generate thermal EMFs of 200nV/°C, over 13 times the worst–case drift of the LTC2057. Layout techniques to match or minimize the number of junctions in the amplifier's input signal path, keep inputs and matching junctions close together, and avoiding thermal gradients are important in these low drift circuits.

#### Conclusion

Noise is a fundamental physical limitation. To minimize its effects in processing sensor signals, care must be taken in choosing a suitable op amp, in minimizing and matching input resistances, and in the physical layout of the design.