]로 드리프트 증폭기는 이름에서 알 수 있듯이 오프셋 전압 드리프트가 거의 ()에 가까운 증폭기를 말한다. 자동 영점 조정(Auto zero) 기능 또는 쵸핑(chopping) 기 술을 사용하거나 이 둘을 모두 사용하는 제로 드리프트 증 폭기는 시간과 온도 변화에 따라 발생하는 DC 오류를 끊임 없이 자가 보정(Self-correct)한다. 이러한 기술을 통해 증 폭기는 마이크로볼트 수준의 오프셋과 극히 낮은 오프셋 드리프트 성능을 달성한다. 따라서 이러한 증폭기는 고이 득 & 고정밀 성능을 갖춘 신호 조정 회로에 특히 적합하다. 예를 들어 센서(온도, 압력, 로드 셀 등)는 보통 낮은 수준의 출력 전압을 발생시키기 때문에 추가 오류를 생성하지 않 으면서도 증폭기를 사용해 출력을 증폭시켜야 한다. 제로 드리프트 증폭기는 초저 오프셋 전압 및 드리프트 높은 공 통모드 및 전원 장치 신호 제거. 1/f 잡음 감소가 가능하도 록 설계되었다. 따라서 제품의 수명 주기가 길고 요구 사양 이 높은 신호 감지 및 조정 등의 시스템 어플리케이션에서 고도의 해상도를 달성하는데 이상적이다.

# 제로 드리프트 증폭기의 기본 아키텍처

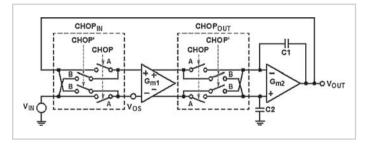

그림 1은 단위 이득일 때 기본 쵸퍼 증폭기의 회로 다 이어그램의 구성(configuration)을 보여준다. DC 이득 경로는 첫 번째 트랜스컨덕턴스(transconductance) 증

그림 1. 쵸핑 아키텍처(Chopping Architecture)

폭기(Gm1)인 입력 쵸핑 스위치 네트워크(CHOP₁)와 두 번째 트랜스컨덕턴스 증폭기(Gm2)인 출력 쵸핑 스위치 네트워크(CHOPour). 주파수 보상 커패시터(C1과 C2)로 이루어진다. CHOP와 CHOP'는 클록 발생기로 조정되 며 증폭기에서 나타나는 원치 않는 DC 오프셋 전압(Vos) 을 보정하는 기능을 한다.

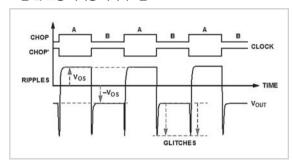

그림 2는 관련된 타이밍 다이어그램과 예상되는 출력 전압(Vour)을 보여준다. CHOP 클록 신호가 HIGH(위상 A) 일 때 증폭기 Gm1의 차동 입출력은 반전되지 않는 신호 경 로에 연결되며 Vos가 있기 때문에 양의 출력 전압(Vour)을 발생시킨다. CHOP' 클록 신호가 HIGH(위상 B)일 때 Gm1 의 입출력은 반전되어 신호 경로에 연결되며  $V_{\infty}$  때문에 음 의 출력 전압을 발생시킨다. Gm1에서 발생하는 양과 음의 전압은 출력 전압인 ±V<sub>cs</sub>가 된다. 시간 영역에서의 이러한 쵸핑의 개념은 주파수 영역에서의 변조 개념과 유사하다.

그림 2 쵸핑 타이밍 다이어그램

즉. Gm1의 오프셋 전압은 CHOPour에 의해 쵸핑 주파수로 상향 변조된다. 반면. 입력 신호는 CHOP™과 CHOPOUT에 의해 두 번 쵸핑된다. 이는 상향 변조되었다가 다시 원래의 주파수로 하향 변조될 때의 입력 신호와 일치한다. 따라서 입력 신호는 반전되지 않고 출력으로 전달된다.

Gm1에서 발생한 양과 음의 출력 전압(±V<sub>os</sub>)은 V<sub>OUT</sub> 에서 전압 리플로 나타난다(그림 2). 이외에도 CHOP과 CHOP'의 클록은 스위치에 연결된 기생 커패시턴스를 통해 차동 입력 핀과 연결된다. 클록이 상태를 변화시킬 때 전하가 차동 입력 핀으로 흘러 들어간다. 이러한 전하 주입은 한정된 입력 전원 임피던스를 통해 출력 전압의 글리치(glitch)로 변환된다. 글리치의 크기와 모양은 입 력 전원 임피던스와 차동 입력 핀에 주입되는 전하의 양 과 그 둘의 일치되는 정도에 따라 달라진다. 이러한 출력 전압 리플과 글리치는 쵸핑 주파수와 그 정수배의 주파수 에서 스위칭 잡음(artifacts)을 야기하며 이는 잡음 스펙 트럼의 증가 형태로 나타난다. 또한 스위칭 잡음의 크기 와 주파수는 각 제로 드리프트 증폭기마다. 장치(Unit)마 다 다르다. 이 글에서는 쵸핑과 스위칭 주파수라는 용어 를 서로 바꿔가며 사용한다.

#### 데이터시트에 나타난 스위칭 잡음

여태까지 제로 드리프트 증폭기에서 광대역 잡음은 상 당히 크고 스위칭 주파수의 범위는 수 KHz에서 수십 KHz로 낮은 편이었다. 이러한 특성 때문에 제로 드리프 트 증폭기의 사용은 DC 및 100Hz 이하의 범위를 지원하 는 어플리케이션으로 한정되다보니 스위칭 주파수는 해당 신호 대역의 외부에 남게 된다. 그보다 높은 대역에서 높

은 정밀도와 낮은 드리프트를 요구하는 어플리케이션의 경우 높은 스위칭 주파수를 지원하는 제로 드리프트 증폭 기를 사용하는 것이 중요하다. 사실상 스위칭 주파수는 제 로 드리프트 증폭기의 성능 지수로 간주되기도 한다.

최근에 출시되는 제로 드리프트 증폭기는 최신 설계 아키텍처를 기반으로 더 높은 주파수에서 스위칭 잡음을 줄일 수 있도록 설계된다. 예를 들어 고전압, 듀얼, 제로 드리프트 증폭기인 ADA4522-2는 4.8MHz에서 오프셋 전압도 쵸핑하지만 특허를 받은 오프셋 및 리플 보정 루 프 회로를 사용해 스위칭 잡음을 최소화한다. 보정 루프 는 800KHz에서 동작하며 오프셋 전압(±Vos)을 NULL 로 보내는 기능을 가진다(그림 2 참조). ±V∞를 원래 값 의 1% 수준으로 줄이면 스위칭 잡음이 40dB 향상되며 그 결과 시스템 설계자가 원하는 수준의 시스템 정밀성을 달성하기가 수월해진다.

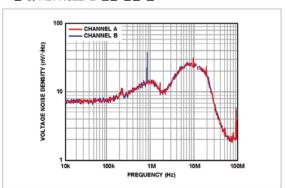

스위칭 잡음은 증폭기 전압의 잡음 밀도(Noise density) 스펙트럼을 살펴보면 가장 쉽게 확인할 수 있 다. **그림 3**은 ADA4522-2의 입력 기준 전압의 잡음 밀 도 그래프를 보여준다. 스위칭 주파수가 800KHz일 때 채널 B에서 잡음 스펙트럼이 증가한다는 것을 알 수 있 다. 잡음 스펙트럼의 이러한 증가는 이 글의 앞부분에서 도 언급했지만 전하 주입의 불일치로 인해 발생하는 부작 용이다. 이러한 불일치는 부품 간, 채널 간에 따라 달라지 기 때문에 잡음 스파이크의 크기도 달라지며 모든 장치 (units)에서 잡음 스파이크가 나타나는 것도 아니다. 예 를 들어 동일한 장치더라도 스위칭 주파수가 800KHz일 때 채널 A에는 잡음 스파이크가 발생하지 않는다. 스위 칭 주파수는 장치 사이에서도 온칩 클록 발진기의 주파수

그림 3, ADA4522-2 전압 잡음 밀도

변화로 인해 최대 10~20%까지 달라질 수 있다.

## 제로 드리프트 증폭기 간의 잡음 비교

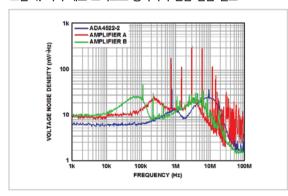

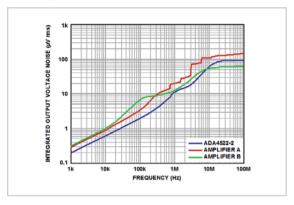

그림 4는 서로 다른 3종의 최신 고전압 제로 드리프트 증폭기에서 나타나는 입력 기준의 전압 잡음 밀도를 보여 준다. 테스트를 실시한 3종의 제로 드리프트 증폭기는 모 두 어느 정도의 스위칭 잡음이 발생한다는 점에 주의한 다. 스위칭 잡음은 어느 정도 정수배의 주파수에서 반복 되기도 한다. 스위칭 잡음은 중대한 사안일 수 있으며 회 로 설계에서 오류를 야기할 수 있다. 따라서 스위칭 잡음 이 회로에 미치는 영향을 이해하고 그 영향력을 약화시키 는 방법을 찾는 것이 중요하다. 증폭기의 폐쇄 루프 주파 수(a closed loop frequency)가 스위칭 주파수보다 높을 때 잡음 스펙트럼의 증가는 전체 대역에 걸쳐 통합되어 출력에 반영된다. 이외에도 이러한 입력 기준의 전압 잡 음은 증폭기의 잡음 이득으로 증폭된다. 예를 들어 증폭 기에서 이득을 100으로 설정하면 실효 출력 기준의 전압 잡음 밀도도 100배 증가할 수 있다.

증폭기의 출력에서 통합되는 총 RMS 잡음은 증폭기

그림 4. 여러 제로 드리프트 증폭기의 전압 잡음 밀도

의 대역폭에 따라 결정된다. 출력 전압 잡음은 사용 가능 한 대역폭에 따라 롤오프(roll-off)하기 때문에 이득이 크거나 대역폭이 크면 출력 증폭기 잡음의 진폭도 커진 다. 그림 5는 통합 출력 전압 잡음과 주파수를 비교한 그 래프를 보여준다. 이 그래프를 보면 주파수에 대한 총 통 합 잡음의 변화를 이해하기 쉽다. 예를 들어 증폭기의 대 역폭이 필터링을 통해 100KHz로 제한되면 증폭기 자체

그림 5. 통합 출력 전압 잡음

의 전압 잡음으로 인해 총 출력 잡음이 그래프 범위를 벗 어날 수 있으며 그 값은 다음과 같다.

동일한 배수(또는 파고율(crest factor))를 사용해 RMS 전압을 피크-대-피크 전압으로 변환할 때 피크-대-피크 잡음의 추정치는 표 1의 3번째 열에 표시된 값과 같다. 5V 시스템에서 ADA4522-2는 18.6bit의 피크-대-피크 해상도를 제공하며, 증폭기 B는 16.8bit의 피크-대-피크 해상도를 제공한다. 총 통합 출력 잡음은 낮으면 낮을수록 좋은데 이는 신호대잡음비(SNR. signal-tonoise ratio)가 높아지고 전체 시스템의 해상도가 높아지 기 때문이다.

표 1. 통합 출력 잡음

| 증폭기       | 출력 잡음( | 피크-대-피크 출력 잡음(µVpp) |

|-----------|--------|---------------------|

| ADA4522-2 | 1.91   | 12,61               |

| 증폭기 A     | 3.33   | 21,98               |

| 증폭기 B     | 6.40   | 42,24               |

그림 5에서 또 하나 흥미로운 점은 통합 잡음이 잡음 스파이크 주파수에서 계단식 함수처럼 증가한다는 점이 다. 잡음 스파이크가 비록 좁기는 해도 그로 인해(증가한 잡음 에너지와 함께) 총 통합 출력 잡음에 추가되는 잡음 은 상당히 크다.

### 시간 영역에서 스위칭 잡음

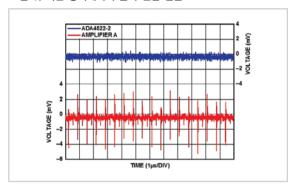

스위칭 잡음은 주파수 영역의 전압 잡음 밀도 스펙트럼 에서 분명히 확인되는 경우가 많다. 스위칭 잡음의 시간에

그림 6. 시간 영역에서의 출력 전압 잡음

따른 변화를 이해하기 위해서는 비반전 핀이 접지된 버퍼 구성에 증폭기를 설정하고 오실로스코프(Oscilloscope)의 출력을 직접 모니터링해야 한다. 그림 6은 제로 드리프트 증폭기 2개에서의 일반적인 출력을 보여준다. 증폭기 A는 다양한 진폭에서 출력 전압 스파이크가 나타난다는 점에 주목한다. 스파이크는 0.66 seec마다 동일하게 반복되며 그림 4에서 주파수가 1.51MHz일 때 나타난 잡음 스파이크와 일치한다. 반면에 ADA4522-2의 경우 시간 영역에서 스위칭 잡음이 나타나지 않는다(파란 그래프). 다시 말해 존재하는 잡음 스파이크는 측정 시스템의 잡음 플로어 아래에 있기 때문에 감지할 수 없다. 따라서 설계자는 잡음 스파이크를 문제 삼지 않고 안심하고 ADA4522-2를 ADC 구동 등의 어플리케이션에 사용할 수 있다.

#### 스위칭 잡음을 줄이기 위한 필터

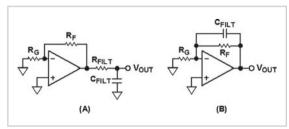

스위칭 잡음의 영향을 줄이기 위한 구현 방법에는 여러 가지가 있다. 이러한 방법들은 모두 결과적으로 증폭기의 대역폭을 스위칭 주파수보다 낮아지도록 제한하게된다. 잡음 스파이크를 제한하는 데에는 필터 사용이 가장 효과적이다. 가장 쉬운 설계 방법은 레지스터-커패시

그림 7. 필터가 설치된 제로 드리프트 증폭기

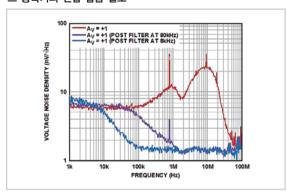

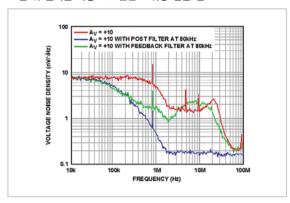

그림 8. 후치 필터(post filter)가 탑재된 단위 이득 제로 드리프 트 증폭기의 전압 잡음 밀도

터 네트워크를 증폭기의 출력에 위치시켜서 로우패스 필터(Low pass filter)를 생성하는 것이다(그림 7A 참조). 그림 8은 후치 필터(post filter)를 스위칭 주파수보다 1 또는 2 디케이드(decade) 아래의 주파수에서 사용하도록설계했을 때의 제로 드리프트 증폭기의 전압 잡음 밀도를보여준다. 800KHz에서의 잡음 스파이크는 36nV/√Hz(후치 필터가 없을 때)에서 4.1nV/√Hz(80KHz에서의 후치 필터)로 줄어들며 이는 증폭기의 저주파 대역 잡음 수준보다 낮은 수치이다. 후치 필터를 스위칭 주파수보다 2 디케이드 낮은 주파수에 위치시키면(8KHz에서의후치 필터) 잡음 스파이크는 더 이상 감지되지 않으며 ADA4522-2는 기존의 다른 어떤 증폭기와도 동일하게 작동되는 것처럼 보인다.

일부 어플리케이션에서는 증폭기의 출력에 R-C 네트워크를 위치시키기 어려울 수 있다. 필터 저항을 통과해 흐르는 증폭기의 출력 전류는 전압 오프셋을 생성하고 이로인해 출력 오차가 발생할 수 있다. 이 경우 피드백 루프에 피드백 커패시터를 위치시켜서 잡음 스파이크를 필터링할수 있다(그림 7B). 그림 9는 필터링을 하지 않고 이득을 10으로 설정했을 때와 스위칭 주파수보다 1 디케이드 아래에 후치 필터나 피드백 필터를 위치시켰을 때의 증폭기의 출력 전압 잡음 밀도를 비교해 보여준다. 후치 필터로는 로우패스 필터가 피드백 커패시터보다 더 효과적이다.

#### 이득을 높게 설정했을 때 제로 드리프트 증폭기 사용하기

많은 설계자들이 그 동안 제로 드리프트 증폭기를 사

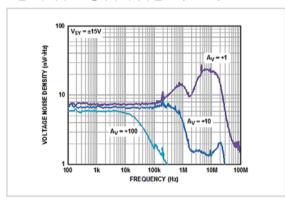

그림 9. 필터를 사용으로 인한 스위칭 잡음 감소

그림 10. 이득으로 증폭기 대역폭 롤오프(roll-off)

용했지만 실제로 시스템에서 스위칭 잡음을 확인한 경우 는 없었다. 그 이유 중 하나가 증폭기의 설정 때문일 수도 있다. 제로 드리프트 증폭기는 드리프트와 오프셋이 낮고 이득을 높게 설정했을 때 (예를 들어 100~1,000 정도의 이득) 낮은 수준의 진폭 센서 신호를 조정하는 데 흔히 사 용된다. 이득을 높게 설정했을 때 증폭기를 사용하면 로 우패스 필터를 증폭기에 위치시키는 것과 같은 효과를 가 진다. 이득이 증가함에 따라 대역폭은 감소한다. 그림 10 은 이득을 높게 설정해서 스위칭 효과를 약화시키는 방법 을 보여준다. 폐쇄 루프 이득이 100일 때 스위칭 잡음은 잡음 그래프(plot)에서 거의 드러나지 않을 수도 있다.

## 제로 드리프트 증폭기로서의 ADA4522-2의 장점

아나로그디바이스의 최신 제로 드리프트 연산 증폭기 (op-amp)인 ADA4522-2는 특허를 취득한 혁신적인 회

로 토폴로지(topology)를 사용해서 높은 스위칭 주파수를 달성하고, 기존의 증폭기와 비교해서 스위칭 잡음을 최소 화한다. 단위 이득 대역폭이 3MHz이고 스위칭 주파수가 800KHz와 4.8MHz일 때 이득을 40으로 설정하면 스위 칭 잡음을 필터링하기에 충분하며 외부의 로우패스 필터 링이 필요하지 않다. ADA4522-2의 특성인 최대 22nV/ °C의 낮은 오프셋 전압 드리프트. 5.8nV/√Hz에서의 낮 은 잡음(이득을 100으로 설정), 최대 150pA의 낮은 입력 바이어스 전류. 높은 공통모드 제거 및 전원 신호 제거 등 은 무게 계량, 전류 감지, 온도 센서 프론트 엔드, 로드 셀 및 브리지 트랜스듀서(Transducer)처럼 드리프트가 중요 한 다른 정밀 어플리케이션에 사용하기에 이상적이다.

### 결론

제로 드리프트 증폭기는 오프셋 전압과 드리프트가 매우 낮으며 낮은 수준의 신호를 정밀 증폭해야 하는 어 플리케이션에 사용하기 적합하다. 다음은 제로 드리프트 증폭기를 사용할 때 알아두면 좋은 여러 가지 팁이다.

- 1 모든 제로 드리프트에는 어느 정도의 스위칭 잡음 이 나타나며 전압의 잡음 밀도 그래프(plot)에서 가 장 흔히 감지될 수 있다.

- 2 스위칭 잡음의 크기는 장치(unit)마다 다르다.

- ❸ 스위칭 주파수는 장치에 따라 최대 20%까지 달라 질 수 있다.

- 스위칭 잡음은 주파수와 시간 영역에서 감지될 수 있 다. 어플리케이션에 따라 오류를 발생시킬 수 있다.

- **5** 제로 드리프트 증폭기는 이득을 높게 설정할 때 자 주 사용된다. 이득을 높게 설정하면 대역폭이 감소 해 스위칭 잡음이 문제가 되지 않는 경우가 많다.

- 6 스위칭 잡음을 낮추어서 출력 오차량을 줄이는 것 은 중요하다. 로우패스 필터(R-C 후치 필터나 피 트백 커패시터)를 사용해 스위칭 주파수가 잡음을 억제(suppress)하기 전에 증폭기의 대역폭을 롤오 프하다

- **7** 스위칭 주파수가 높으면, 넓고 유용하며 잡음이 없 는 대역폭에 대한 필터 요건이 간소해진다. 💵