되돌아보는 GaN의 역사: GaN-on-Si IC를 사용한 전원 변환 혁신

글/Alex Lidow Ph.D., CEO and Co-founder, Efficient Power Conversion Corporation

되돌아보는 GaN의 역사

1977년에 동료인 톰 허먼과 나는 International Rectifier에 입사해서 전원 변환 분야에 발을 담그면서 경력을 시작했다. 우리가 처음 맡은 프로젝트는, 당시에 주로 사용되던 전력 바이폴라 디바이스와 비교해서 더 나은 전력 트랜지스터를 설계하는 것이었다. 많은 검토와 논의를 거친 끝에, 톰과 나는 금속 산화막(MOS) 게이트를 사용한 전력 트랜지스터를 만들기로 결정했다. 1세대 디바이스는 알루미늄 게이트 기술을 사용해서 1978년 11월에 출시되었으며, 2세대 디바이스는 실리콘 게이트 기술을 사용해서 1979년 6월에 출시되었다. 6각형 구조를 기반으로 한다는 점에서 2세대 디바이스를 “HEXFET”이라고 명명했으며, 전원 변환 분야로 일대 변화를 가져왔다.

HEXFET은 이전 세대인 바이폴라 디바이스보다 더 빠르고, 크기가 작고, 궁극적으로 비용을 낮추고, 좀더 신뢰할 수 있었다. 더 빠른 스위칭 속도를 최대한 활용하기 위해서는 디자이너들이 어느 정도 자신의 엔지니어링 역량을 연마할 필요가 있었다. 스위칭 속도가 더 빠르므로 당시에 주로 AC/DC 컨버터와 모터 드라이브였던 전원 변환 시스템을 크기를 더 작게 하고, 신뢰성을 높이고, 비용을 낮출 수 있게 되었다.

성능이 더 높은, 이 새로운 디스크리트 디바이스를 사용해서 설계하기 위해서는 귀중한 시간이 들었고, 이 점이 이 디바이스를 채택하는 것을 꺼리게 만들었다. 이에 대한 해결책은 간단해 보였다. IC 형태로 전체적인 시스템온칩(SoC)을 개발하는 것이었다.

SoC를 개발하기 위해서 처음으로 시도한 것은 TRIMOS라고 하는 새로 개발된 디바이스를 사용해서 모노리딕 트라이액을 제작하는 것이었다[1]. 이렇게 하는 과정에서 실리콘으로 다중의 전력 소자를 통합하는 것과 관련한 몇 가지 기본적인 사실들을 발견하게 되었다. 동일한 칩으로 수직으로 전도하는 전력 소자들을 집어넣으려니까 비용이 크게 증가해서 SoC를 상업적으로 만들기 어려웠다. 전력 소자들을 횡형으로 설계하려니까 차지하는 면적 때문에 디바이스를 상업적으로 만들기 어려웠다. 이러한 문제를 깨닫게 되자 댄 킨저와 데이비드 탬까지 합류한 더 큰 팀이 주축이 되어서 하프 브리지 구성으로 전력 디바이스들을 스위칭하기 위해서 사용할 수 있는 드라이버 IC 개발에 나섰다. 이 첫 제품이 IR2110이었다.

오늘날까지도 디스크리트 전력 MOSFET(또는 이의 사촌 격인 IGBT)과 드라이버 IC는 전원 변환 분야에 지배적으로 사용되고 있다.

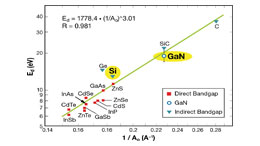

갈륨 나이트라이드(GaN) 전력 트랜지스터

일본의 어느 연구팀이 실리콘 웨이퍼 상에 갈륨 나이트라이드(GaN)를 성장하기 위한 기법을 개발한다는 소식을 들었을 때[2], 이 새로운 기술을 사용해서 전원 변환 시스템으로 실리콘의 집적 한계를 극복할 수 있겠다는 생각이 들었다. GaN은 특성적으로 절연성이며, GaN 트랜지스터를 만들기 위해서 가장 좋은 방법은 상단면으로 게이트, 드레인, 소스의 3개 단자를 형성하는 것이다. GaN은 소수 캐리어 전도가 크게 일어나지 않으므로, 횡형 전력 MOSFET이 다이오드 전도가 되었을 때 그러는 것처럼 정공이나 전자로 인해서 한 전력 소자가 다른 전력 소자를 오염시키는 문제가 발생하지 않는다.

이러한 이해를 바탕으로 나와 두 동료인 조 카우 및 밥 비치가 함께 2007년 가을에 Efficient Power Conversion(EPC)이라는 회사를 설립했다. 시작부터 목표는 실리콘 디바이스에 비해서 성능은 더 높고 비용은 낮추는 전력 디바이스를 개발하는 것이었다. 처음에는 디스크리트 디바이스를 개발하려고 했으나, 통합을 통해서 전환 변환으로 의미 있는 변화를 가져올 수 있겠다는 생각에 이르게 되었다. 통합이 디지털 전자기기로 그랬던 것처럼, 그리고 수십 년 전에 HEXFET이 그랬던 것처럼 말이다.

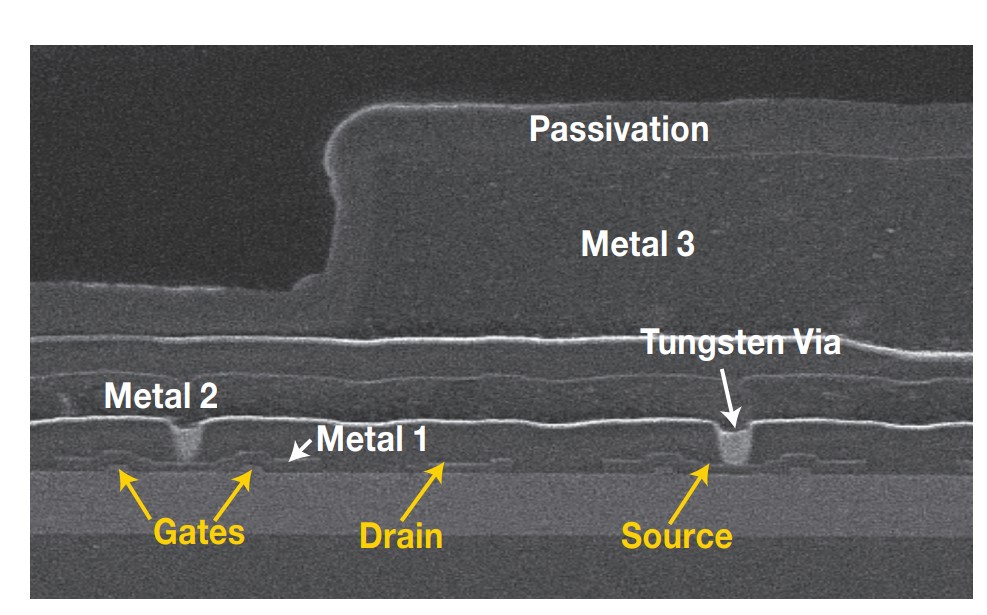

2009년에 우리 회사는 첫 번째 프로토타입으로서 100V 디스크리트 GaN-on-Si 전력 트랜지스터를 내놓게 되었다. 이 제품은 2010년 3월에 양산에 착수했으며, 40V 및 200V 트랜지스터와 함께 하나의 제품군을 형성하게 되었다. 이들 제품은 향상 모드 디바이스이기 때문에 eGaN® FET으로 명명하게 되었다. 그림 1은 eGaN FET의 주사 전자 현미경(SEM) 영상을 보여준다.

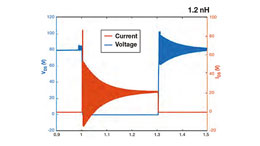

이 디바이스는 속도가 빨랐다. 비슷한 전압대 및 온 저항으로 실리콘 디바이스에 비해서 대략 5~10배 더 빨랐다. 이처럼 속도가 높아짐으로써 회로 디자이너들이 레이아웃에 좀더 주의를 기울여야 했다. 기생 인덕턴스가 추가됨으로써 전압 및 전류 오버슈트를 발생시킬 수 있기 때문이었다. 이 오버슈트는 전력 손실을 증가시키고, EMI 및 EMC 발생을 증가시키고, 게이트 또는 드레인 과전압을 발생시키는 것으로 이어졌다. 이 디바이스를 사용한 설계의 어려움 때문에 채택 속도도 더뎌 보였다.

그리고 일년이 안 되어서, 시간에 대해서 좀더 안정적이고 라이다, 포락선 추적, 자동차 전조등, DC/DC 컨버터 같은 더 다양한 애플리케이션을 지원할 수 있는 2세대 제품을 내놓게 되었다. 이 과정에서 해결 과제는 좀더 분명해졌다. 어떻게 하면 디자이너들이 좀더 손쉽게 이 최신 디바이스를 최대한 활용할 수 있도록 하느냐 하는 것이었다.

GaN IC

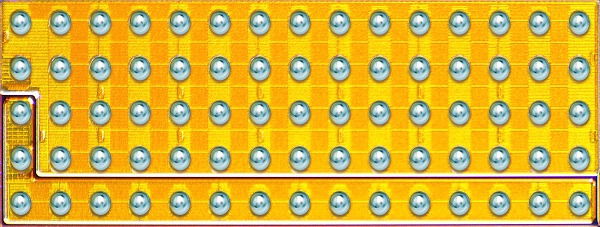

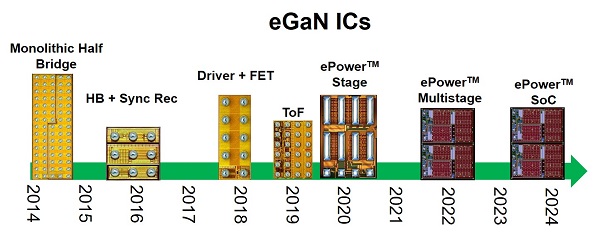

단일 칩으로 기능을 통합하는 여정에서 첫 발을 뗀 것은 2014년 9월이었다. EPC가 처음으로 모노리딕 하프 브리지 디바이스 제품군을 출시한 것이다. 단일 칩으로 하프 브리지로 구성할 수 있는 2개 FET을 통합함으로써, 고객들이 (a) 상당한 보드 공간을 절약하고 (b) 전력 루프 인덕턴스를 반으로 줄이고 (c) EMI와 EMC를 발생시키는 오버슈트를 낮출 수 있게 되었다. 그림 2는 이러한 초기의 하프 브리지 IC를 보여주는 것으로서, 이것은 벅 구성의 DC/DC 컨버터에 사용하도록 설계된 것이다. 상측 트랜지스터가 하측 트랜지스터보다 작게 설계되었으며, 두 전력 소자들 사이에 인덕턴스가 거의 0이 되도록 설계되었다.

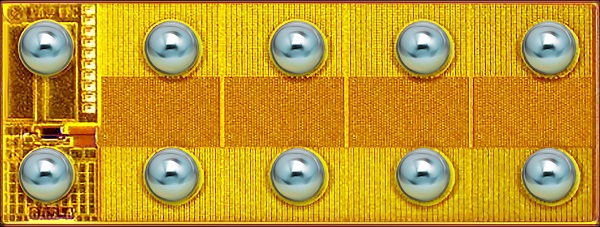

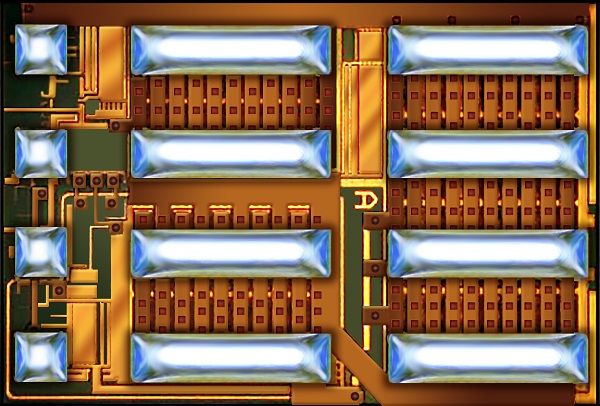

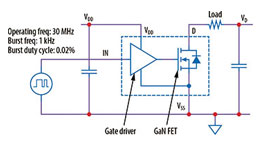

이와 동시에 동일한 칩으로 전력 FET에 드라이버를 추가하기 위한 연구가 시작되었다. 모노리딕 디바이스로 드라이버를 통합함으로써 외부적인 실리콘 기반 IC 드라이버를 필요 없게 만들고 게이트 루프 인덕턴스를 제거할 수 있겠다고 생각했다. 이 첫 번째 상용화 제품이 2018년에 출시되었다. 그림 3은 이 제품 중의 하나를 보여준다.

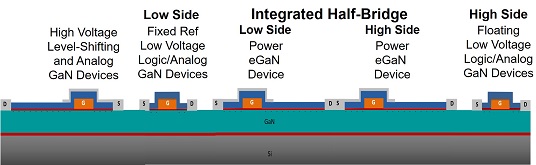

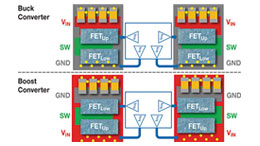

하지만 궁극적인 목표는, 단일 칩으로 전체적인 전원 변환 솔루션에 필요로 하는 모든 기능을 통합하는 것이었다. 전원 변환 토폴로지가 다양한 만큼, 가능한 솔루션 또한 다양하다. 그런데 대부분의 경우에 공통적으로 사용되는 빌딩 블록이 하프 브리지이다. 하프 브리지는 벅 컨버터, 부스트 컨버터, LLC 컨버터, 버스 컨버터, 모터 드라이브, 그 외의 다양한 컨버터 토폴로지에 사용된다. 그러므로 하프 브리지 주변으로 통합을 이루는 것이 합리적일 것이다. 그림 4는 어떻게 다양한 요소들을 통합할 수 있는지 보여준다.

GaN은 특성적으로 절연성이므로, 상측 및 하측 FET을 서로 가까이 배치할 수 있다. 게이트와 드레인 단자 사이의 거리를 줄일 수 있으므로, 고전압 FET 가까이로 극소형 저전압 FET을 형성할 수 있다. 이러한 소신호 디바이스들을 사용해서 디지털 기능뿐만 아니라 아날로그 기능을 구현할 수 있다. 그림 4에서 가장 왼쪽에 있는 고전압 레벨 쉬프트 소자를 사용해서 상측과 하측을 연결할 수 있다.

그림 3에서 보는 것과 같은 1세대 EPC eGaN® IC는 시행착오를 거치면서 경험적 추측에 토대해서 수작업으로 제작되었다. 신뢰할 수 있는 최상의 성능을 달성하기 위해서는 기술 플랫폼을 풍부한 모델 셋으로 변환하는 것이 필요하다. 이러한 모델 셋은 스케일링 가능하고, 기생 상호작용을 포함하고, 모든 온도, 전압, 전류 조건으로 특성분석을 하고, 기생 프로세스 변화를 포함해야 한다. 이것은 결코 만만한 작업이 아니며, 빠르게 향상되는 디스크리트 FET 성능과 격차가 있을 수 있다. 기술 플랫폼을 철저하게 특성분석을 하기 위해서는 시간과 노력이 들어가고, 또 한편으로 기술 플랫폼이 특성분석 프로세스보다 더 빠르게 변화하면 IC 제품이 성능이나 비용적 경제성에 있어서 디스크리트 디바이스에 비해서 뒤쳐질 수 있다.

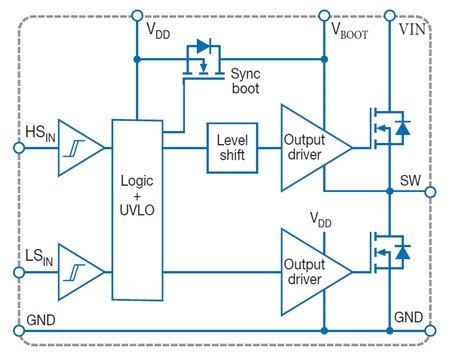

이와 같이 좀더 형식화된 접근법의 성과가 2020년 3월에 처음으로 모습을 드러내게 되었다. 모든 구동 및 레벨 쉬프트 기능에 부트스트랩 기능까지 통합한 완전 모노리딕 하프 브리지를 출시한 것이다. 그림 5는 전원 스테이지의 모든 기본 기능들을 포함하는 회로 다이어그램을 보여준다. 그림 6은 실제 디바이스 사진이다.

오늘날의 디지털 프로세서에 비하면 단순하지만, 이 단일칩 전원 스테이지 제품은 최초로 모든 주요 기본 기능들을 통합했다. 단일 서브스트레이트 상으로 비교기, IC로 의사결정을 위한 중앙 빌딩 블록, 출력 동작 제어를 위한 피드백, 입력 및 출력 절연을 위한 래칭, 어셈블리 견고성을 위한 ESD 내성, 상측 및 하측 간에 전압 절연을 비롯한 다양한 기능을 통합하고 있다.

이러한 빌딩 블록들을 사용해서 어떠한 IC든 만들 수 있다. 계속해서 빠른 속도로 디자인 개선과 향상이 이루어질테지만, 이 첫 번째 데모는 GaN IC의 무한한 가능성을 보여주며 갈륨 나이트라이드가 전원 변환 분야로 가져올 일대 변화들을 예고하는 것이다. EPC의 이 제품(EPC2152)은 벅 컨버터나 모터 드라이브 토폴로지에 사용하도록 설계된 것이다.

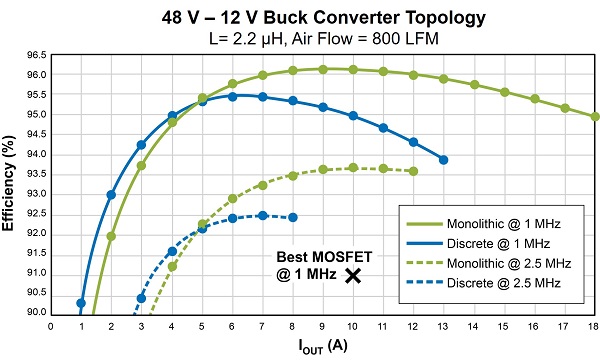

그림 7은 1MHz로 48VIN 및 12VOUT으로 10A로 벅 컨버터로 동작할 때 모노리딕 전원 스테이지의 시스템 효율(녹색 선)을 보여준다. 그림 7에서 X 지점에서 1MHz로 최신 실리콘 솔루션과 성능을 비교해 볼 수 있다. GaN 모노리딕 전원 스테이지가 실리콘 솔루션에 비해서 전력 손실이 50% 낮다.

그림 7에서는 또한 동일 칩으로 드라이버와 전력 FET을 통합함으로써 얻을 수 있는 이점을 확인할 수 있다. 파란색 선은 동일한 하프 브리지로 디스크리트 GaN FET과 드라이버에 레벨 쉬프트를 위한 또 다른 별도의 SiC 기반 IC를 사용했을 때의 측정 효율이다. 이처럼 효율을 크게 향상시킬 수 있는 이유는 두 가지를 들 수 있다. (1) 드라이버와 전력 디바이스가 동일 칩 상에서 가까이 인접할 때 게이트 루프로 인덕턴스가 감소하고, (2) 두 전력 FET을 모노리딕으로 통합함으로써 전반적인 전력 루프 인덕턴스를 반으로 줄이기 때문이다.

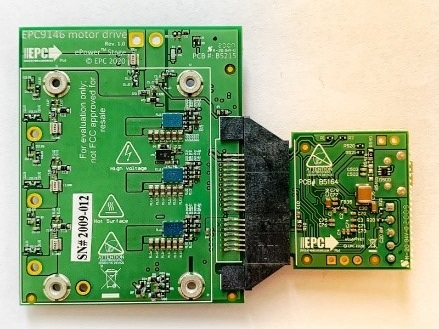

EPC2152는 벅 컨버터 애플리케이션 외에도 절연형 DC/DC 컨버터의 일차측이나 BLDC 모터 드라이브에 사용하기에 적합하도록 설계되었다(그림 8).

GaN 통합의 미래

앞으로의 과제는 최신 GaN 기술 플랫폼을 기반으로 잘 정의된 풍부한 모델 셋을 사용해서 단일 칩으로 계속해서 더 많은 기능들을 추가하는 것이다. 최종적인 목표는, 마이크로컨트롤러로부터 단지 단순한 디지털 입력만을 필요로 하고 전력 출력을 발생시켜서 부하를 효율적으로 구동하고 모든 조건으로 신뢰하게 동작하고 최소한의 공간만을 차지하고 경제성을 높이는 단일 IC를 달성하는 것이다.

이 목표를 달성하기 위해서는 이 칩으로 전류와 온도를 측정하기 위한 센서를 추가해야 한다. 또한 더 많은 디지털 제어 기능을 추가함으로써 성능을 향상시키고, 비용을 낮추고, 전원 시스템 디자이너에게 요구되는 전반적인 엔지니어링을 줄일 수 있다. 앞으로 몇 년 내에 이러한 기능들이 추가될 것이다.

실리콘 기반이든 GaN-on-Si 기반이든 디스크리트 전력 트랜지스터는 쇠퇴의 길로 접어들고 있다. 통합적인 GaN-on-Si는 성능을 높이고, 풋프린트를 줄이고, 비용을 낮추고, 필요한 엔지니어링을 줄일 수 있다. 그림 9는 2014년에 최초의 모노리딕 하프 브리지에서 시작해서 다양한 전원 변환 애플리케이션 용으로 다중스테이지 및 다중위상 IC들을 거쳐서 궁극적으로 완전 모노리딕 시스템온칩(SoC)으로 나아가기 위한 여정을 보여준다.

참고문헌 2. Nakamura, S.,”GaN growth using GaN buffer layer,” Jpn. J. Appl. Phys, 30 (10A) L1705-L1707 (1991) 3. A. Lidow, M. de Rooij, J. Strydom, D. Reusch, J. Glaser, GaN Transistors for Efficient Power Conversion, 3rd Edition, J. Wiley 2020. Available from https://epc-co.com/epc/Products/Publications/GaNTransistorsForEfficientPowerConversion.aspx 4. A. Lidow, “Gallium Nitride Integration: Going Where Silicon Power Can’t Go [Expert View],” IEEE Power Electronics Magazine, Vol. 5, Issue: 3, Sept 2018. pp 70-72.

1. B. Scharff, James D. Plummer, “A MOS-controlled TRIAC Device”, IEEE International Solid State Circuits Conference Digest of Technical Papers 1978.

(끝)

<저작권자(c) 반도체네트워크, 무단 전재-재배포 금지>

5세대에 이르기까지의 개발 여정

조회수 71회 / Alex Lidow

EPC의 5세대 eGaN® 기술 “새로운 차원의 성능으로 비약적 도약”

조회수 90회 / Alex Lidow

GaN FET에 실리콘 MOSFET 게이트 드라이버를 사용하기 위한 방법

조회수 214회 / Alejandro Pozo

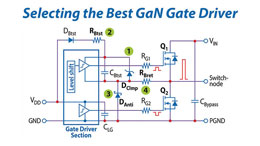

최고의 GaN 게이트 드라이버 선택

조회수 237회 / 류창우

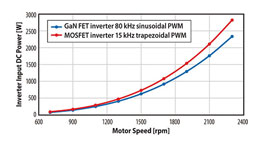

GaN 모터 구동 인버터를 활용한 농업용 드론 혁신

조회수 271회 / EPC

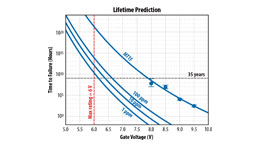

GaN 신뢰성 및 수명 예측: 15단계(8)

DC-DC 컨버터(Ⅱ)

조회수 293회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(7)

DC-DC 컨버터(I)

조회수 338회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(6)

“test-to-fail” 방법론을 사용...

조회수 499회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(5)

조회수 561회 / Ricardo Garcia 외 5인

PDF 다운로드

회원 정보 수정