GaN FET에 대한 전압 및 전류 스트레스 테스트

글/Alex Lidow Ph.D., CEO & Co-Founder of Efficient Power Conversion Corporation

통상적으로 반도체에 대한 검증 테스트는, 데이터시트에서 표기하고 있는 한계로 또는 그에 근접하는 조건으로 일정한 시간 동안 또는 일정한 횟수의 사이클로 디바이스로 스트레스를 가해서 결함을 나타내지 않는지 확인하는 것으로 이루어진다.

디바이스를 한계 조건으로 테스트함으로써 데이터 시트 한계 이상으로 필요한 마진을 이해할 수 있으며, 좀더 중요하게는 반도체의 근본적인 결함 메커니즘을 이해할 수 있다. 결함 메커니즘, 결함의 원인, 그리고 시간, 온도, 전기적 또는 기계적 스트레스에 대해서 디바이스 동작을 이해함으로써 전반적인 동작 조건들로 제품의 안전한 동작 수명을 예측할 수 있다[1].

스트레스 요인과 결함 메커니즘

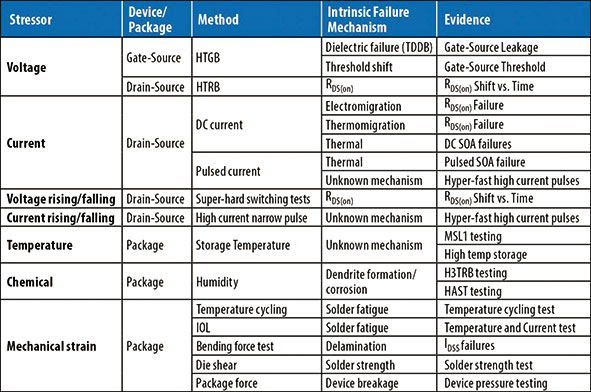

전력 트랜지스터로 주요한 스트레스 요인들로는 전압, 전류, 온도, 습도를 들 수 있다. 표 1은 이러한 스트레스 요인들을 열거하고 있다.

[표 1] eGaNⓇ FET으로 스트레스 요인과 결함 메커니즘

이러한 각각의 요인들에 대해서 디바이스로 스트레스를 가해서 결함이 발생되는 것을 살펴봄으로써, 테스트 대상 디바이스(DUT)의 주요한 결함 메커니즘을 이해할 수 있다. 합리적인 시간 안에 결함을 발생시켜서 확인해 보기 위해서는 스트레스 조건을 데이터 시트에서 표기하고 있는 한계보다 훨씬 높게 해야 한다.

이 글에서는 이러한 스트레스 요인으로서 전류에 초점을 맞춰서 살펴본다. eGaN FET의 탁월한 견고성을 입증하기 위해서 부품을 두 가지 조건으로 테스트했다. 첫째, SOA(safe operating area)를 알아보기 위해서 eGaN FET을 지정된 펄스 지속시간으로 높은 전류(ID)와 높은 전압(VDS)에 노출시켰다. 둘째, 단락 회로 견딤 시간을 알아보기 위해서 eGaN FET으로 게이트를 최대 전압으로 턴온해서 단락 회로를 겪게 했다.

SOA(안전 동작 영역)

SOA 테스트의 주된 목적은 FET이 데이터 시트 SOA 그래프 내의 모든 지점(ID, VDS)으로 결함을 일으키지 않고서 동작할 수 있는지 확인하기 위한 것이다. 안전 영역을 벗어나서 결함을 일으키는지 테스트해서 안전한 여유 마진을 확인하는 용도로도 사용될 수 있다.

SOA 테스트 시에 다이 내에서 높은 전력 소모로 인해서 접합부 온도가 급격하게 상승하고 온도 변화가 있을 수 있다. 전력이 충분히 높거나 펄스 지속시간이 길면 디바이스가 과열되고 심각한 결함을 일으킬 것이다. 이것을 열 과부하 결함이라고 한다. Si MOSFET으로는 SOA 테스트 시에 이차 항복(Spirito 효과[2])이라고 하는 또 다른 결함 메커니즘이 관찰되었다. 이 결함 모드는 높은 VD와 낮은 ID일 때 발생하는 것으로서, 접합부 온도와 임계 VTH 사이의 불안정한 피드백으로 인해서 발생되는 것이다.

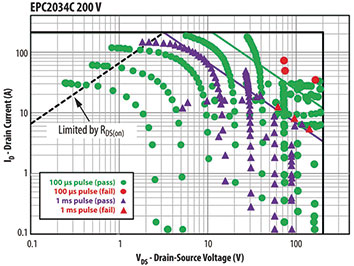

그림 1은 200V EPC2034C의 SOA 데이터를 보여준다. 이 플롯에서는 개별적인 펄스 측정들을 (ID, VDS) 공간에 점들로 표시하고 있다. 이 점들을 데이터 시트 SOA 그래프와 겹쳐서 보여주고 있다. 100μs와 1ms 펄스로 측정된 데이터들을 볼 수 있다. 100μs 측정으로, 낮은 VDS에서부터 VDS;max(200V)에 이르기까지 어떠한 결함을 일으키지 않는 넓은 SOA 영역을 확인할 수 있다(모두 초록색 동그라미). 모든 결함(빨간색 동그라미)은 초록색 선으로 표시된, 데이터 시트 그래프 상의 SOA 바깥에서 발생된다. 1ms 펄스 데이터도 마찬가지다(보라색과 빨간색 삼각형). 모든 결함은 데이터 시트 SOA 바깥에서 발생되고 있다.

[그림 1] EPC2034C의 SOA 플롯. ‘Limited by RDS(on)’선은 150℃로 데이터 시트 RDS(on) 최대 사양 한계이다. 1ms(보라색 삼각형)와 100μs(초록색 동그라미) 펄스로 측정한 것을 보여준다. 빨간색 삼각형(1ms)과 빨간색 동그라미(100μs)로 표시된 측정들은 결함을 나타낸다.

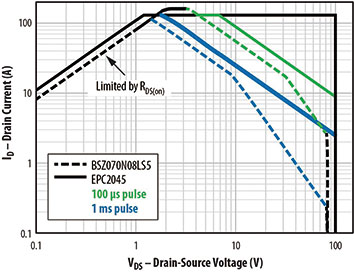

그림 2에서는 비슷한 정격으로 시중에 출시된 전력 MOSFET(점선)과 EPC2045 eGaN FET(실선)의 SOA 데이터를 비교하고 있다. Si 전력 MOSFET으로는 1ms 펄스로 10VDS의 낮은 드레인 전압 지점에서 이차 항복이 발생된다는 것을 알 수 있다.

[그림 2] BSZ070N08LS5 MOSFET과 EPC2045 eGaN FET의 SOA 비교

단락 회로 테스트

단락 회로 견고성은 FET이 전원 컨버터로 ON(전도) 상태일 때 발생될 수 있는 예기치 않은 결함 조건을 견딜 수 있는 능력을 말한다. 이러한 상황에서는 디바이스로 최대 버스 전압이 가해지고 전류 또한 트랜지스터 자체의 근본적인 포화 전류와 회로 기생 저항에 의해서만 제한된다. 이러한 단락 회로 상태를 보호 회로를 사용해서 억제하지 않는다면, 전력 소모가 극단적으로 높아지고 FET으로 과열 문제를 일으킬 것이다.

단락 회로 테스트는 이러한 조건으로 디바이스가 견딜 수 있는 시간을 측정하는 것이다. 통상적인 보호 회로는 2~3μs에 과전류 조건을 감지하고 대처할 수 있다. 그러므로 eGaN FET이 5μs나 혹은 그보다 더 길게 억제되지 않은 단락 회로 조건을 견딜 수 있어야 한다.

대표적으로 2개 eGaN FET에 대해서 이 테스트를 실시했다. EPC2203(80V) 4세대 자동차용(AEC) 디바이스와 EPC2051(100V) 5세대 상업용 디바이스이다.

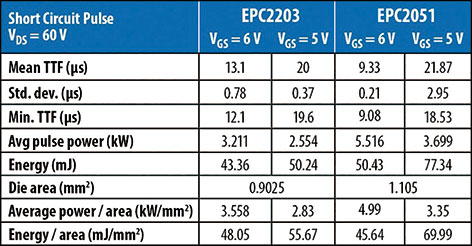

견딤 시간에 대한 통계를 얻기 위해서 8개 디바이스를 테스트했다. 표 2는 이 결과를 보여준다. 5V(권장 게이트 구동)와 6V(VGS(max))로 테스트했을 때 EPC2203은 평균 견딤 시간이 각각 20μs와 13μs로 측정되었다. 6V로 견디는 시간이 더 짧다는 것을 알 수 있는데, 이것은 포화 전류가 더 높기 때문이다. EPC2015는 6V로 결함을 일으키기까지 걸리는 시간이 9.3μs로 EPC2203보다 약간 짧다. 이것은 이 디바이스의 좀더 공격적인 스케일링과 전류 밀도 때문인 것으로 보인다. 하지만 모든 경우로 견딤 시간이 대부분의 단락 회로 보호 회로로 디바이스 결함에 대처하고 방지하기 위해서 충분히 길고 안정적이다. 뿐만 아니라 견딤 시간이 부품들 간에 큰 차이가 없다는 것을 알 수 있다.

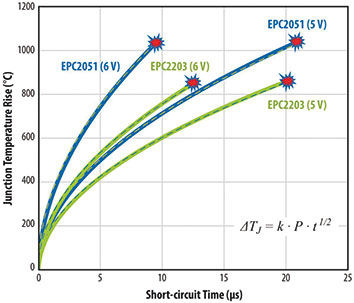

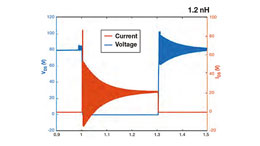

표 2의 아래 칸들에서는 다이 크기에 대해서 펄스 전력과 에너지를 볼 수 있다. 이들 수치와 결함까지의 시간 사이에 상관관계를 이해하기 위해서 시간 종속적 열 전달을 구하고 단락 회로 펄스 시에 접합부 온도 상승 ∆TJ를 계산했다. 그림 3은 이 결과를 보여준다.

[표 2] EPC2203과 EPC2051로 단락 회로 견딤 시간 통계. 표본 집단의 평균 펄스 전력과 에너지도 볼 수 있다.

[그림 3] EPC2051과 EPC2203으로 5V 및 6V VGS로 단락 회로 펄스 시에 시간에 따른 접합부 온도 상승. 빨간색 마크는 측정된 결함 시간을 나타낸다.

펄스가 가해지는 동안에 집중적인 전력 밀도로 인해서 GaN 레이어와 부근의 실리콘 서브스트레이트가 빠르게 뜨거워진다. EPC2203은 5V와 6V로 동일하게 접합부 온도 상승이 850℃인 지점에서 결함이 발생된다. EPC2051도 마찬가지로 두 조건으로 1050℃의 동일한 ∆TJ에서 결함이 발생된다.

맺음말

정확한 결함 메커니즘을 파악하기 위해서는 추가적인 분석이 필요할 것이다. 하지만 이 글에서 살펴본 시험 결과만으로도 극단적인 전압 및 전류 스트레스에 대해서 eGaN FET이 어떻게 우수한지 확인할 수 있다.

참고 문헌

[1] ZVEI Robustness Validation Working Group, Eds., Handbook for Robustness Validation of Semiconductor Devices in Automotive Applications, Third edition: May 2015, Published by ZVEI - Zentralverband Elektrotechnik - und Elektronikindustrie e.V. Available at

https://www.zvei.org/fileadmin/user_upload/Presse_und_Medien/Publikationen/2015/mai/Handbook_for_Robustness_Validation_of_Semiconductor_

Devices_in_Automotive_Applications__3rd_edition_/Robustness-Validation-Semiconductor-2015.pdf

[2] G. Breglio, N. Rinaldi, P. Spirito, “Thermal Mapping and 3D Numerical Simulation of New Cellular Power MOS Affected by Thermal Instability,” Microelectronics Journal, Vol. 31, Issues 9-10, October 2000, pp 741-746.

5세대에 이르기까지의 개발 여정

조회수 73회 / Alex Lidow

EPC의 5세대 eGaN® 기술 “새로운 차원의 성능으로 비약적 도약”

조회수 91회 / Alex Lidow

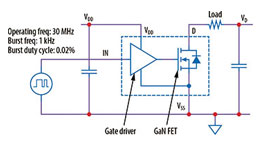

GaN FET에 실리콘 MOSFET 게이트 드라이버를 사용하기 위한 방법

조회수 216회 / Alejandro Pozo

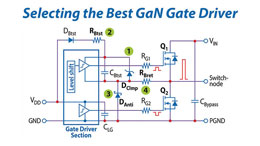

최고의 GaN 게이트 드라이버 선택

조회수 237회 / 류창우

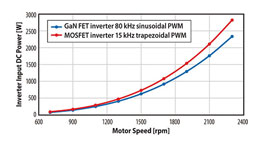

GaN 모터 구동 인버터를 활용한 농업용 드론 혁신

조회수 272회 / EPC

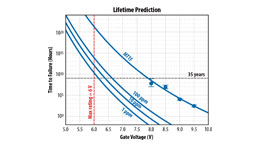

GaN 신뢰성 및 수명 예측: 15단계(8)

DC-DC 컨버터(Ⅱ)

조회수 293회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(7)

DC-DC 컨버터(I)

조회수 339회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(6)

“test-to-fail” 방법론을 사용...

조회수 502회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(5)

조회수 562회 / Ricardo Garcia 외 5인

PDF 다운로드

회원 정보 수정