래티스, 새로운 IP 에코시스템 및 설계 환경으로 FPGA 기반 프로세서 설계 가속화

래티스 반도체는 저전력 소형 폼팩터의 래티스 FPGA를 기반으로 하는 독창적인 애플리케이션 개발을 가속화하는 새로운 소프트웨어 솔루션 ‘래티스 프로펠(Lattice Propel™)’을 출시한다고 밝혔다. 새로운 설계 환경은 RISC-V 프로세서 코어와 많은 주변장치들을 포함하는 강건한 IP 라이브러리로부터 구성요소들을 손쉽게 조립할 수 있게 함으로써, 초보 개발자부터 전문가까지 어떠한 기술 수준의 개발자든 래티스 FPGA 기반의 애플리케이션 설계를 쉽고 빨리 수행할 수 있게 해준다. 프로펠 설계 환경은 통신, 컴퓨팅, 산업, 자동차, 컨수머 시장과 관련한 애플리케이션 개발을 자동화한다.

보다 복잡한 시스템 설계에 FPGA의 병렬 처리 능력을 이용하기 위해 FPGA를 처음 활용하는 개발자들은 힘들여 배우지 않아도 쉽게 사용할 수 있고 유연하면서도, 새롭게 떠오르는 애플리케이션 개발에 필요한 모든 설계 소프트웨어와 IP를 통합하고 있는 애플리케이션 설계 솔루션을 원한다. 래티스 프로펠의 정확하게 구성화된 개발 툴은 설계 프로세스의 상당 부분을 자동화함으로써 전반적인 시스템 개발을 간소화한다. 래티스 프로펠은 시스템 하드웨어와 소프트웨어 설계를 단일 툴 프레임워크에 통합하고 있기 때문에, 소프트웨어 개발자는 최종 하드웨어를 확보하기 전에 시스템 소프트웨어 개발을 먼저 시작할 수 있어 제품 출시를 더욱 앞당길 수 있다.

래티스 반도체의 지안루카 마리아니(Gianluca Mariani) 기술 매니저는 “래티스는 사용자가 특정 기업 고유의 기술 및 표준에 얽매이지 않고, 강력한 프로세서 IP 에코시스템을 활용할 수 있도록 공개 표준을 지원하는 견고한 설계 환경을 제공한다”고 밝히고 “FPGA의 재프로그램 능력을 결합한 래티스 프로펠 설계 환경은 기존 하드웨어와 소프트웨어의 업그레이드가 간편해, 예컨대 플랫폼 펌웨어 리질리언시(Platform Firmware Resiliency, PFR) 같은 새로운 기술 동향과 업계 표준을 지원하기가 수월하다. 래티스 프로펠 출시로, 우리는 소형 폼팩터, 저전력 임베디드 솔루션 관련 로드맵에 착수할 수 있게 됐다”고 말했다.

래티스 반도체의 로저 도(Roger Do) 제품 라인 담당 선임 매니저는 “이번 프로펠 설계 환경 발표는 개발자들에게 래티스 저전력 FPGA 기반 애플리케이션 개발을 간소화 및 가속화하는 완벽한 소프트웨어 솔루션을 제공하기 위한 래티스의 지속적인 투자를 보여주는 또 하나의 사례”라며, “초보 FPGA 개발자인 경우, 래티스 프로펠 GUI를 활용하면 자신의 설계에 필요한 IP 블록을 래티스 IP 라이브러리로부터 드래그-앤-드롭 방식으로 쉽게 적용할 수 있어 전반적인 설계 프로세스를 간소화할 수 있다. 베테랑 개발자라면, 래티스 프로펠을 보다 세분화한 설계 최적화를 위한 스크립트 레벨 편집에 활용하거나 또는 기존 설계를 보다 강력한 래티스 FPGA 솔루션 기반 시스템으로 이식하기 위한 업데이트 작업에 활용할 수 있다”고 설명했다.

래티스 프로펠 설계 환경의 주요 구성요소는 다음과 같다:

• Lattice Propel Builder – 완벽한 GUI 세트와 명령 라인 툴의 지원과 함께, 풍부한 자원을 갖추고 있는 시스템 IP 통합 환경. 래티스 프로펠 빌더는 개발자가 래티스 FPGA 기반 설계 상에 새로운 IP를 불과 수 분 내에 구현할 수 있게 해주는, 견고하면서 정기적으로 업데이트되는 IP 서버에 접속할 수 있게 해준다. 이번 발표 시점을 기준으로, 이 서버에서는 RISC-V RV321 호환 프로세서 코어를 포함한 8개의 프로세서와 주변기기 IP 코어를 제공한다. 래티스는 간단한 드래그-앤-드롭 시스템 빌더 환경에서 RISC-V 기술을 활용할 수 있는 SRAM 및 플래시 기반 FPGA를 업계 최초로 제공한다. 보다 복잡한 시스템에서 IP의 연결 및 관리를 간소화할 수 있도록, 래티스 프로펠 빌더를 통해 활용이 가능한 모든 IP 코어들은 AMBA 온칩 인터커넥트 규격을 준수한다.

• Lattice Propel SDK – 래티스 프로펠 설계 환경에서 구현되는 설계를 더욱 가속화하기 위해, 래티스 프로펠 SDK는 최종 시스템 하드웨어가 확보되기 전에 소프트웨어 개발을 시작할 수 있게 해준다. 이 프로펠 SDK는 업계 표준 소프트웨어 개발 툴, 소프트웨어 라이브러리, 개발보드 지원 패키지를 포함하고 있기 때문에 개발자는 자신의 애플리케이션 소프트웨어를 쉽고 빠르게 구축, 컴파일, 분석, 디버그 할 수 있다.

현재 래티스 프로펠 설계 환경은 래티스 사용자들에게 공급되고 있다.

래티스, 새로운 Avant-G 및 Avant-X 미드레인지 FPGA

조회수 204회 / Lattice

래티스, 차량용 애플리케이션 개발 가속화하는 소프트웨어 포트폴리오 ...

조회수 332회 / 래티스 반도체

래티스, 새로운 FPGA 플랫폼으로 유효 시장 두 배 확대

조회수 417회 / 래티스 반도체

래티스반도체, 신제품 발표로 제어 FPGA 리더십 강화

조회수 693회 / Lattice Semiconductor

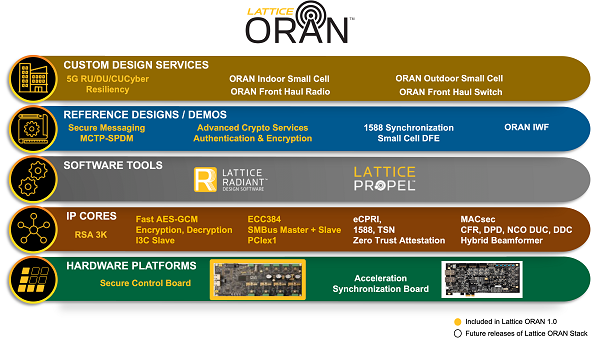

래티스, 5G ORAN 솔루션에 맞춤화된 저전력 FPGA 기반 스택 출시

조회수 502회 / 래티스 반도체

래티스, 차세대 클라이언트 기기 개발을 가속화하는 sensAI 솔루션 스택...

조회수 560회 / Lattice

래티스, 높은 I/O 밀도와 소형 폼 팩터를 갖춘 자동차용 등급의 FPGA

조회수 690회 / Lattice Semiconductor

래티스, 4배-65%-100배-6.5배 향상? 범용 FPGA 제품군

조회수 718회 / Lattice Semiconductor

래티스, 공장 자동화 시스템 개발이 쉬워졌어요

조회수 854회 / 래티스 반도체

PDF 다운로드

회원 정보 수정