래티스 반도체, CrossLinkTM 프로그래머블 ASSP IP 솔루션 확장

최신 IP와 개발 플랫폼, 추가 자원을 활용함으로써 다양한 MIPI 인터페이스를 지원하는 새로운 비디오 브리징 기능 제공

• 최신 프로세서, 디스플레이 및 센서를 사용하는 혁신적인 비디오 브리징 애플리케이션의 개발 촉진

• 뛰어난 설계 유연성, 독창적인 프로그램 가능성, 우수한 성능을 지원하여 컨수머, 산업, 자동차를 포함한 폭넓은 시장에 적합

• CrossLink IP 기반의 설계 제품은 이전 버전보다 로직 자원을 최대 40% 적게 사용하여 전력 소비는 줄이고 더 많은 기능을 구현

주문형 스마트 커넥티비티 솔루션 전문 기업인 래티스 반도체(지사장 이종화)는 새로운 비디오 브리징 기능을 지원하도록 자사의 CrossLink™ 프로그래머블 ASSP(pASSP) 솔루션을 확장한다고 발표했다. 이번에 선보인 솔루션은 3개의 CrossLink IP(intellectual property)와 2개의 CrossLink 데모 플랫폼이며, 2개의 데모 플랫폼은 각각 MIPI® DSI에서 LVDS로, CMOS에서 MIPI CSI-2로의 인터페이스 브리징을 시연할 수 있다. 컨수머, 산업, 자동차 애플리케이션용 브리징 솔루션 공급을 강화하고 있는 래티스는 이번 솔루션 확장과 관련하여 기존 CrossLink IP를 최적화함으로써 로직 자원 사용을 줄이는 한편, 전력 소비도 낮췄다.

래티스의 CrossLink 제품은 오늘날 급변하는 I/O 시장과 관련한 여러 과제들을 해결하도록 설계됐으며, 설계자들이 고성능, 저전력, 소형 브리징 솔루션을 개발할 수 있도록 새로운 방법을 제시한다. 래티스가 지난해 CrossLink를 처음 선보인 이후, 많은 고객들이 이 제품에 관심을 나타내고 있다. 특히, CrossLink 제품이 초기의 전형적인 애플리케이션을 넘어서 더 간단한 인터페이스 변환이나 이미지 센서, 애플리케이션 프로세서, 디스플레이의 결합 및 먹싱(muxing) 등으로 애플리케이션을 확장하는 것에 대해 많은 기대를 나타냈다.

래티스는 기존 IP를 최적화하는 한편 새로운 IP와 개발 플랫폼 및 추가적인 자원을 활용함으로써 FPGA의 유연성 및 빠른 타임투마켓 성능과 ASSP의 전력 및 기능 최적화 특성을 모두 갖춘 솔루션들을 확장하고, 이들 솔루션을 광범위한 브리징 애플리케이션을 위해 공급할 수 있게 되었다.

래티스 반도체의 모바일 및 컨수머 사업부 마케팅을 담당하는 C.H. Chee 시니어 디렉터는 “새로운 CrossLink IP와 솔루션들은 고객들이 카메라와 디스플레이 제품에 최신 모바일 인터페이스 기술을 적용하여 전반적인 시스템 비용과 전력소비, 크기를 줄임과 동시에 자신들의 차세대 제품 설계 주기를 가속화할 수 있게 할 것”이라며, “프로그래머블 브리징 디바이스의 최초 개발사이자 세계에서 가장 빠른 MIPI D-PHY 브리징 디바이스 개발사인 래티스는 최고의 대역폭, 최저의 전력소비 및 최소의 풋프린트를 가진 저가의 브리징 솔루션을 공급하기 위해 최선을 다하고 있다”고 말했다.

새로운 CrossLink pASSP IP 솔루션의 주요 특징은 다음과 같다:

새로운 CrossLink IP

• 1:1 입출력 MIPI CSI-2 카메라 인터페이스 브리지는 커넥터, 대형 PCB, 연성 케이블에 대해 더 우수한 커넥티비티와 향상된 신호무결성을 지원한다. 이와 함께 데이터 패킷 보수 또는 추가적인 패킷 전송을 위한 프로그래밍도 가능하다.

• 1:2 입출력 MIPI CSI-2 카메라 스플리터 브리지는 하나의 이미지 센서로부터 2개의 소스 장비로 비디오 데이터를 전송할 수 있게 해준다.

• 4:1 MIPI CSI-2 카메라 어그리게이터 브리지는 4개의 CSI-2 카메라를 프로세서 상의 1개의 CSI-2 인터페이스에 연결할 수 있게 해준다. 이미지 센서는 2개가 한쌍으로 결합되어 좌/우 포맷에 연결된다. 이때, GPIO 핀이 2개씩 묶인 2쌍의 이미지 센서 세트를 다중화할 수 있다.

새로운 데모 플랫폼 기술

• CMOS 대 MIPI CSI-2 카메라 브리징 시연

o MIPI DPI CMOS 타입 픽셀 버스를 지원하는 일반적인 이미지 센서를 애플리케이션 프로세서(AP) 상의 CSI-2 입력단에 연결

o MIPI DSI 대 LVDS 디스플레이 브리징 시연

o 애플리케이션 프로세서를 듀얼 링크 LVDS 디스플레이에 연결

• MIPI DSI 대 LVDS 인터페이스 브리징 시연

o 모바일 애플리케이션 프로세서를 대형 포맷의 LVDS 디스플레이에 연결

o 산업용 디스플레이가 대량의 고성능 모바일 애플리케이션 프로세서와 연결될 수 있는 기능 시연

추가 자원

• CrossLink IP의 전체 스위트는 다음 링크에서 확인할 수 있다: http://bit.ly/2k84sQb

• Clarity Designer에서 구매할 수 있는 새로운 CrossLink IP는 Lattice Diamond 3.9와 함께 다음 링크에서 다운로드 할 수 있다:

http://www.latticesemi.com/en/Products/DesignSoftwareAndIP/FPGAandLDS/LatticeDiamond.aspx

새로운 IP를 지원하는 CrossLink 평가보드는 현재 래티스와 래티스 대리점을 통해 구매가 가능하다. 보다 자세한 정보는 www.latticesemi.com/CrossLink 참조.

래티스, 새로운 Avant-G 및 Avant-X 미드레인지 FPGA

조회수 201회 / Lattice

래티스, 차량용 애플리케이션 개발 가속화하는 소프트웨어 포트폴리오 ...

조회수 330회 / 래티스 반도체

래티스, 새로운 FPGA 플랫폼으로 유효 시장 두 배 확대

조회수 416회 / 래티스 반도체

래티스반도체, 신제품 발표로 제어 FPGA 리더십 강화

조회수 690회 / Lattice Semiconductor

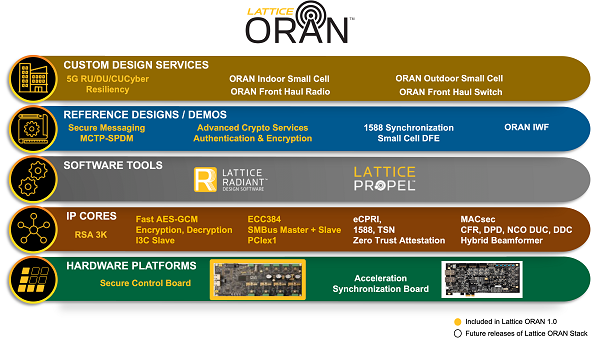

래티스, 5G ORAN 솔루션에 맞춤화된 저전력 FPGA 기반 스택 출시

조회수 498회 / 래티스 반도체

래티스, 차세대 클라이언트 기기 개발을 가속화하는 sensAI 솔루션 스택...

조회수 559회 / Lattice

래티스, 높은 I/O 밀도와 소형 폼 팩터를 갖춘 자동차용 등급의 FPGA

조회수 689회 / Lattice Semiconductor

래티스, 4배-65%-100배-6.5배 향상? 범용 FPGA 제품군

조회수 715회 / Lattice Semiconductor

래티스, 공장 자동화 시스템 개발이 쉬워졌어요

조회수 851회 / 래티스 반도체

PDF 다운로드

회원 정보 수정