3D NAND 성능, 신뢰성 및 수율을 개선하기 위한 고려사항

글/마크 푸톡(Mark Puttock), 인테그리스 디렉터

NAND 플래시 기술은 수십 년 동안 전 세계에 비휘발성 메모리를 제공해 왔다. 플래시 드라이브에서부터 노트북, 스마트폰, 태블릿 및 현재 클라우드 스토리지 운영에 사용되는 솔리드 스테이트 저장 장치 등의 응용 분야로 NAND 플래시 기술의 사용 분야가 확장되었다. 시간이 지남에 따라 증가하는 저장 공간 용량, 스케일링 및 신뢰성 요구를 충족할 수 있도록 새로운 구조가 도입이 되었고, 이전 세대의 솔리드 스테이트 메모리 기술보다 비트당 더 낮은 비용으로 향상된 성능과 낮은 소비 전력을 제공함으로써 그 가치를 입증하였다.

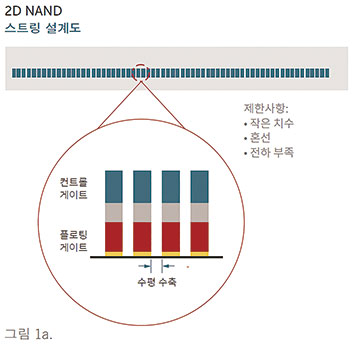

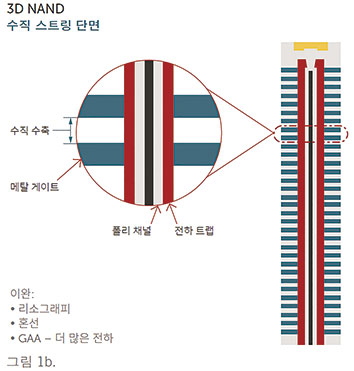

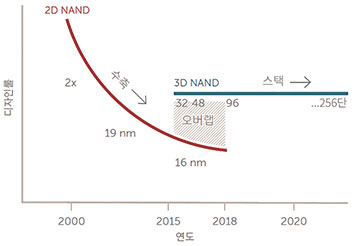

초기에는 NAND 플래시 메모리 제조업체가 멀티 패터닝 기법을 사용하여 점진적으로 배선폭을 줄여 메모리 밀도를 증가시켜 해당 비용이 감소했다. 하지만 안타깝게도, 2D(평면) NAND 플래시 메모리는 15nm 노드 근처에서 스케일링 한계에 도달했다. 그래서 제조업체는 GAA(gate-all-around) NAND 셀 층을 쌓아 새로운 성능 목표를 달성하는 혁신적인 접근 방법을 채택했다. 이로써 스케일링에 대한 접근 방식의 근본적인 전환을 가져오는 오늘날의 3D NAND 구조가 시작되었다. 이 기술에서는 2차원 평면에서의 수평 스케일링 대신 3차원에서의 확장을 도입하였다. 자세한 내용은 그림 1a와 1b를 참조하면 된다. 3D NAND 기술은 비트당 더 높은 밀도와 더 낮은 비용을 제공한다.

[그림 1a 및 1b] 3D NAND 설계에서는 메모리 셀을 수직으로 여러 단으로 쌓아서 2D NAND 스케일링 문제를 해결하고 비트당 더 낮은 비용으로 밀도를 높일 수 있다.

그러나 이런 모든 장점에도 불구하고 3D NAND 제조의 공정 복잡성과 자본 집약도 때문에 제조 시 공정 제어, 수율 및 비용 증가 등의 문제로 인해 개발에 어려움이 있다[1]. 그래서 경쟁력 있는 비트당 비용을 실현하고자 막대한 투자를 통해 24단, 32단 및 48단 3D NAND를 위한 제조 공정을 개발했다. 여러 가지 이유로 64단 이상의 3D NAND 구조가 비용 절감에 가장 효율적으로 여겨진다.

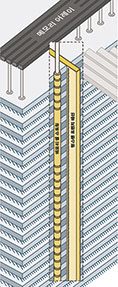

[그림 2] 3D NAND 아키텍처에서는 메모리 밀도를 늘리기 위해 수평 스케일링에 의존하지 않고 메모리 셀을 쌓음으로써 문제를 해결한다.

3D NAND 기술의 초기 적용은 2007년에 Toshiba (BICS, bit cost scalable)와 삼성(V-NAND)에서 시작되었다. Micron/Intel과 SK Hynix가 그 뒤를 빠르게 뒤따랐으며 YMTC China는 새롭게 진입한 기업이다. 이들 기업은 3D NAND 제조의 주요 생산 업체이다. 최초의 대용량 3D NAND 제조는 2013년에 삼성에서 진행되었으며 최근에 생산이 가속화되고 있다. 2017년 말에는 삼성의 3D NAND 플래시 생산 비율이 총 NAND 플래시 생산의 70%를 초과할 것으로 예측되었다. 2017년 4사분기에는 해당 분기의 80%를 초과했다[2].

3D NAND 기술이 빠르게 안정되고 있고 메인스트림 기술이 되고 있지만 칩 생산업체는 매우 복잡한 환경에서 더 낮은 비용으로 전 세계의 소비자 및 비즈니스 데이터 요구를 충족하기 위해서는 아직 해야 할 일이 많다는 것을 알고 있다. 칩 생산업체에서 장비 제조업체 및 소재 공급업체에 이르는 전체 반도체 산업이 협력을 통해 다음 단계인 더 낮은 비용으로 더 높은 성능의 3D NAND 플래시 메모리 제조 수율을 높이는 과제를 달성해야 한다는 것이 분명해 보인다. 이전 기술과 마찬가지로 공정 효율성, 소재 혁신, 오염 관리에 집중함으로써 제조 공정을 최적화하여 성능을 개선하고, 수율을 높이고, 비용을 절감해야 한다. 이 백서에서는 특히 에칭 및 증착 과제와 오염 문제를 해결하기 위한 몇 가지 주요 영역을 살펴본다.

소재 개발을 통한 HAR 에칭 최적화

평면 NAND 기술에서는 대부분 리소그래피가 스케일링을 주도하였다. 3D NAND 스케일링에 있어서 높은 HAR(High-Aspect-Ratio)의 복잡한 3D 구조를 구현하기 위해서는 고도의 정밀도와 공정 재현성이 필요하다. 따라서 3D NAND로 성공적인 결과를 얻으려면 편차를 최소화하는 혁신적인 패터닝 솔루션이 필요하다.

HAR 구조의 에칭 정밀도는 셀을 주변 CMOS 회로에 연결하는 계단 구조 아키텍처뿐 아니라 셀 접근을 위한 채널 홀 및 트렌치를 최적화하는 데 매우 중요하다. 지금까지의 비정질 탄소는 일반적으로 HAR 에칭에 사용되는 하드 마스크 소재이다. 이 소재는 채널 홀 AR가 증가하면서 한계에 도달하게 된다. 도핑된 비정질 탄소 또는 기타 하드 마스크 소재를 포함하여 비정질 탄소의 선택성을 높이기 위해 여러 방식이 개발 중이다.

최신 치수 정보에서는 약 100nm의 수직 거리와 약 5μm의 스택 두께를 제안하며, 여기서 AR 은 약 50:1에 해당한다. 또한, 셀 스택은 셀 영역의 질화규소(Si3N4)와 셀을 격리하는 이산화규소(SiO2)로 구성되어 있어 건식 에칭 엔지니어가 연속적으로 똑바른 프로파일을 만들면서 구조의 바닥에 도달했을 때 비정질 탄소 하드 마스크에 대한 충분한 선택성을 유지하기가 매우 어렵다. 따라서 이 영역에서는 이러한 문제를 해결하기 위해 상당한 소재 개선 또는 새로운 소재를 고려해야 한다.

또한 다층 스택 높이가 증가하면 메모리 배열의 상단과 하단에서 균일한 에칭 및 증착 프로파일을 만들기가 어려워진다. 예를 들어, 50:1 정도의 비율인 경우 습식 에칭으로 Si3N4를 선택적으로 제거하는 데 있어 문제가 발생한다. SiO2를 에칭하지 않고 상, 하단 및 웨이퍼 전체에서 Si3N4를 균일하게 제거하는 것이 어렵다. 96단 미만에서 이 작업은 고온(최대 160℃)의 인산으로 가능했지만 96단 이상에서는 공정 마진을 높이기 위해 특별히 배합된 습식 에칭 케미컬이 필요하다.

하드 마스크를 제거하기 위한 습식 에칭 공정은 배합된 케미컬이 필요한 습식 공정의 또 다른 예가 될 수 있다. 극한의 공정은 에칭에 좀 더 잘 견딜 수 있는 하드 마스크가 필요하다. 그러한 하드 마스크는 에칭 후 제거에 대해 어려움이 더 커질 수 있다. 건식 에칭 장비와 공정 혁신도 필요하지만, 공정 안정성, 재현성, 최적화를 위한 하드 마스크, 소재 기인 후속 스텝의 개발도 필요하다.

[그림 3] SiO2에 비례한 선택적 Si3N4 제거. 이는 셀 스택 제조의 중요한 단계로 상단과 하단 모두에서 사양을 충족해야 한다.

소자 속도 저하 방지

3D NAND에서는 스택이 높아지고 실리콘 채널이 길어지면 채널의 전자의 이동성 감소에 의해 소자 동작이 제한된다. 제조업체는 전도성 실리콘 채널에 도펀트(dopant) 주입을 통해 실리콘 채널의 전자의 이동성을 높여 이 둔화를 상쇄할 수 있다. 게르마늄 도핑은 전자 이동성을 개선할 수 있다고 알려진 한 방법이며 3D NAND 제조를 위해 현재 개발되고 있다. 공정의 요구 사항은 직경이 약 50nm이고 깊이가 수 μm HAR 실리콘 채널을 따라 균일한 도핑을 하는 것이다. 소스 공급업체는 이를 위해 게르마늄 도펀트를 제공하는 더 효율적인 방법을 찾기 위해 노력하고 있다. 가능성이 높은 접근 방식은 수소에 희석된 게르마늄을 공급하는 현재 방법을 순수 게르마늄을 사용하는 공정으로 대체하는 것이다.

앞서 언급한 것처럼 3D NAND의 계단 모양 구조의 목적은 NAND 스택 하단의 셀까지 외부 주변 회로에서 셀 제어 게이트에 접근할 수 있는 워드라인을 형성할 수 있게 하는 것이다. 워드라인의 폭이 감소함에 따라 전체 장치 성능을 유지하기 위해 좁은 배선 폭에서 비저항이 더 낮은 코발트, 루테늄 또는 몰리브덴과 같은 대체 메탈을 현재 사용 중인 텅스텐 대신 적용해야 할 수도 있다. 이러한 극단적인 HAR 조건에서 ALD(Atomic Layer Deposition) 공정을 구현하여 셀 스택의 상단과 하단에 균일한 필름을 생성할 수 있는 전구체에 대한 개발 작업이 진행 중이다. 이와 별도로 W 워드라인의 습식 식각 마진 확보를 위해서 배합된 새로운 케미컬이 유용할 수 있다.

[그림 4] 실리콘 채널이 길어지면 전자의 이동성 증가가 중요해진다.

공급업체에서부터 조기 defect 제어 확립

공정 순도 및 defect 제어는 3D NAND 공정에 매우 중요하다. 실제로, 3D 스택에서 트랜지스터의 수가 증가하면 하나의 defect가 둘 이상의 셀을 차단하고 전체 장치의 성능에 영향을 미칠 수 있다. 따라서, 모든 잠재적인 오염을 확인하고 에칭 챔버, 소재 불순물, 적절하지 않은 케미컬 여과, 웨이퍼 캐리어 장치, 포토레지스트 기포 생성 등에서 기인하는 결함을 방지하기 위한 적절한 단계를 수행해야 한다.

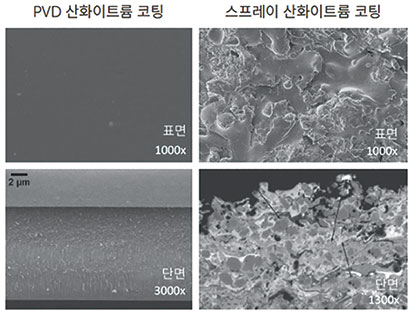

HAR 플라즈마 에칭 단계에서는 내부 에칭 챔버 부품이 긴 고출력 고온 공정에 노출, 부식되어 파티클이 떨어질 수 있다. 전통적으로 강도 높은 플라즈마로부터 보호하기 위해 에칭 챔버 부품에 산화이트륨(Y2O3)을 분사해서 한 겹의 코팅막을 만들었다. 그림 5에서 보여주는 바와 같이 이 막을 초소형 전자 현미경으로 확인해 보면 매우 거칠어 보이다. 이러한 roughness 때문에 작은 파티클과 오염물질이 많이 떨어진다. PVD(물리적 증기 증착) 또는 플라즈마 화학 증기 증착(PECVD)과 같은 기법으로 증착된 더 높은 품질의 Y2O3 층이 요구된다. 이렇게 증착된 물질의 밀도가 높고 표면이 매끄러울수록 웨이퍼 결함이 적어진다.

[그림 5] 플라즈마 분사 표면과 비교한 PVD 표면

ALD 공정의 경우도 마찬가지이다. 최근에 점점 더 견고한 코팅 시험에 대한 요구가 ALD 챔버 및 장비 부품으로까지 확대되었다. ALD 공정은 전하를 저장하는 셀 층을 증착하므로 금속 오염원에 매우 민감한다. 전구체와 접촉하는 모든 표면은 잠재적인 오염원이다. 이동 시스템, 파이프, 밸브 및 게이지에는 코팅 기법을 사용하여 오염으로부터 보호해야 할 수 있는 내부 부품이 포함되어 있다.

부품 코팅은 고도로 맞춤화된 공정이다. 경우에 따라 PVD만으로도 충분하지만 극한의 스텝 커버리지가 필요한 부품에는 ALD 공정이 사용된다. 에칭 및 증착 챔버 부품의 품질에 대한 이 같은 각별한 주의는 3D NAND 사양으로 인해 시작되었지만 점차적으로 첨단 로직 반도체 소자 제조 업체에서도 요구하고 있다. 일반적인 소자 패턴 사이즈 감소와 같이 3D NAND도 세대가 증가할수록 오염에 더 민감하게 된다. defect는 소자 성능에 중대한 영향을 미치므로 소재 순도가 매우 중요하다. 순도 제어에는 더 많은 주의가 필요하다.

뿐만 아니라 메모리 셀 구조의 오염 관리는 최적의 웨이퍼 수율 및 신뢰성을 달성하는 데 매우 중요하다. 오염 관리는 모든 웨이퍼와 직접 접촉하는 케미컬에서부터 시작한다. 소자 제조업체는 계속해서 케미컬 공급업체에게 더 높은 순도를 제공하라는 요청을 하고 있다. 케미컬 순도 증가는 공정 청정도를 달성하고 제조 공정의 소자 수율을 개선하는 첫 번째 단계이다. 이 단계에서는 고도화된 품질 관리, 깨끗한 패키징 및 운송(예: 온도 관리 포함)을 포함한 대용량 제조 scale-up을 지원할 수 있는 공급업체와 협력하는 것이 중요하다.

많은 홀(칩당 20억 개 이상)과 최신 3D NAND 소자의 스택 두께 증가를 고려하면, 에칭 단계에서 생성된 부산물의 양이 각 기술 세대에서 점점 더 많아지는 것을 알 수 있다. 또한 공정 단계가 오래 걸리기 때문에 웨이퍼는 일반적으로 FOUP(front-opening unified pod, 전면 개방형 통합 포드)에서 더 많은 대기 시간을 보내게 된다. 이러한 경우 대기 시간 동안 부산물이 내부 FOUP 표면에 흡착되어 웨이퍼로 옮겨져 defect가 발생할 수 있다. 이러한 부산물이 재흡착되는 것을 방지하기 위하여 내부 배리어 소재로 코팅된 폴리카보네이트 FOUP를 사용하는 혁신적인 솔루션을 개발했다. 이 솔루션은 부산물을 더 효율적으로 배출할 수 있으므로 defect 발생을 줄일 수 있다.

깊은 에칭 구조의 경우 비정질 탄소 하드 마스크 층을 구현하기 위해 매우 두꺼운 고점도 포토레지스트 층(1,000cps)이 필요하다. 이 정도의 점도 수준은 포토레지스트 분사 도중 미세기포 형성을 유발하여 후속 패터닝 과정에서 defect를 만들 수 있다. 웨이퍼의 기포 형성은 배선폭이 큰 소자 제조에서는 중요하지 않지만, 3D NAND 공정은 치수가 더 작으므로(예: 채널 직경 최대 50nm) 리소그래피 defect에 더 민감하다. 기포를 최소화하려면 고점도 포토레지스트를 펌핑해서 내보낼 수 있는 새로운 방법이 필요하다.

이를 위해 여과, 기포 제거, 고점도 포토레지스트 분사를 위한 펌핑 시스템을 개발했다. 이러한 시스템의 중요한 특징은 펌프 사이에 필터가 있는 2단계 펌프이다. 유휴 상태에서는 포토레지스트가 필터를 거쳐 두 번째 스테이지로 들어가므로 흐름을 제한하거나 기포를 생성하지 않고 배출할 수 있다. 이상적으로는 이 펌프에 네트워크 연결 기능이 있어 통합 유량 측정기가 분사 용량을 제조 공장 매개변수 모니터 시스템에 업로드할 수 있다.

기포 형성 가능성을 줄이기 위한 대체 접근 방식은 bag-in- a-bottle 개념이다. Bottle 속에 있는 깨끗한 bag(liner)에 포토레지스트를 담는다. bottle과 bag(liner) 사이의 공간에 압력이 작용해 포토레지스트를 효과적으로 압착해 장비로 내보낼 수 있다. 포토레지스트와 bottle 사이의 접촉이 없어 오염 문제를 피할 수 있으며 bottle 안의 포토레지스트가 공기와 접촉할 수 있는 공간이 사라져 기포가 생성되는 것을 줄일 수 있다.

현재 진행되는 최신 오염 제어는 첨단 소자 개발을 위해 적층을 높이고 및 배선폭을 줄이는 데 필요한 공정 순도를 달성하기 위해 중요하다. 순도를 극대화하기 위해 전체 반도체 에코시스템이 협력하여 잠재적인 오염원을 확인하고 적절한 솔루션을 개발해야 한다.

요약

2D 평면 NAND 플래시 메모리의 스케일링 한계에 도달하고, 3D로 NAND 셀을 적층하는 기술이 도입되면서 스택과 관련된 새로운 공정 문제가 발생한다. 이러한 문제를 해결하는 것은 다음에 대한 혁신으로 이어진다.

• 하드 마스크 및 부산물 관리 등의 모든 주변 공정부 혁신을 고려한 HAR 에칭

• defect를 줄이기 위한 고도의 오염 제어 요구 해결

• 소자 속도 저하 문제를 해결하기 위한 전자 이동성 및 전도성 강화

• 극한 구조에서 메모리 셀을 정밀하게 구성할 수 있는 솔루션

소자 제조업체, 장비제조업체, 소재 제조업체/오염 전문가 사이의 긴밀한 협력을 통해 3D NAND가 지속적으로 개발될 수 있도록 공정 혁신을 이루어 나가야 한다. 업계는 128단, 256단 및 그 이상에 수직 셀 스택 아키텍처를 사용하여 용량이 더 높고 비트당 비용이 더 낮은 성능과 신뢰성이 뛰어난 장치를 구현할 것이다.

3D NAND 성능, 신뢰성 및 수율을 개선하기 위한 Entegris 솔루션

Entegris는 최첨단 반도체 제조를 위한 첨단 소재, 소재 관리 및 오염 제어 솔루션을 개발하는 글로벌 리더이다. Entegris는 3D NAND 설계 및 제조의 고유한 문제를 이해하고 고객과 협력하여 에칭 및 세정 공정을 위해 특별히 배합된 케미컬을 개발하고 최적화할 뿐 아니라, 공정의 무결성을 보장하는 솔루션을 개발하기 위해 고객의 공정 및 잠재적인 오염원을 이해하는 데 집중하고 있다.

Entegris는 액체, 고체 및 기체 케미컬에 대한 안전하고 효율적인 케미컬 이동 시스템과 최신 여과 기술 및 특수 코팅에 이르기까지 순도에 대한 열정을 가지고 있으므로 설계에서 공급과 소재 관리, 제조 및 제공에 이르는 플래시 메모리 제품 체인의 모든 측면에 영향을 미치는 문제를 해결하고 있다.

[참조]

1. Overcoming Challenges in 3D NAND Volume Manufacturing, 솔리드 스테이트 기술 웹사이트: http://electroiq.com/blog/2017/07/overcoming-challenges-in-3d-nand-volume-manufacturing/

2. Signaling End of Flat NAND Flash Era, 한국 사업부 웹사이트: http://www.businesskorea.co.kr/english/news/ict/20216-signaling-end-flat-nand-flash-era- percentage-3d-nand-flash-production-exceeds-80

자율 주행 차량의 LiDAR용 GaN FET

조회수 74회 / Kenton Williston

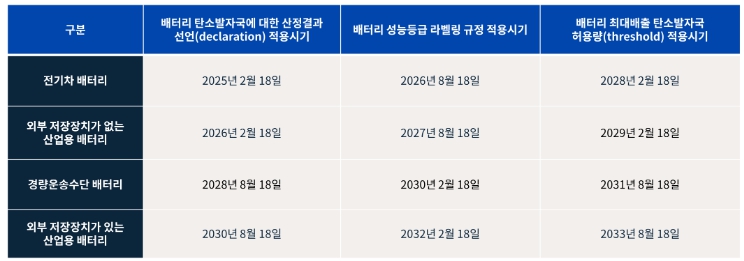

EU 배터리 규정(EU BATTERY REGULATION)이란?

조회수 99회 / TUV

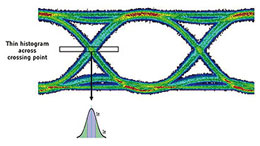

지터가 고속 링크에 미치는 영향

조회수 96회 / Bill Schweber

패널 실장 인코더 - 기본 사항 이해

조회수 335회 / Jeff Smoot

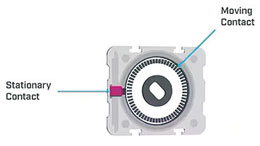

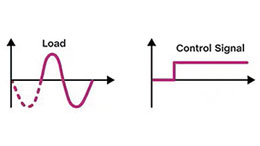

전기 기계 계전기와 무접점 계전기 비교

조회수 282회 / Jeff Smoot

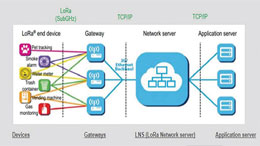

인증된 LoRaWAN 모듈을 사용하여 장거리 연결 개발 가속화

조회수 307회 / Stephen Evanczuk

다양한 응용 제품을 위한 스위치 솔루션

조회수 232회 / Ryan Smoot

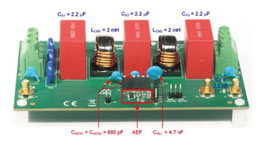

독립형 능동 EMI 필터 IC가 공통 모드 필터 크기를 줄이는 방법

조회수 326회 / 티모시 헤가티

컨베이어 걸림에 대한 오경보 방지로 공장 자동화 생산성 향상

조회수 236회 / Steven Keeping

PDF 다운로드

회원 정보 수정