대량 생산에서 수율 관리를 가능하게 하는 STT-MRAM의 자기 테스트

글/Hprobe의 설립자 겸 CTO 샤막 살리미

STT-MRAM(Spin Transfer Torque Magnetic Random Access Memory ; 스핀 전달 토크 자기 메모리)은 빠르고 휘발성이 없으며 내구성이 뛰어날 뿐 아니라 저전력의 확장가능한 새로운 메모리 기술로 최근 빠르게 각광받고 있다. eFlash를 대체할 강력한 대안인 동시에 자동차와 IoT 를 비롯한 저전력 애플리케이션에 특히 매력적인 이 소자의 대량 생산에 필수적인 높은 수율을 지원하기 위해서는 새로운 테스트 접근 방식이 필요하다.

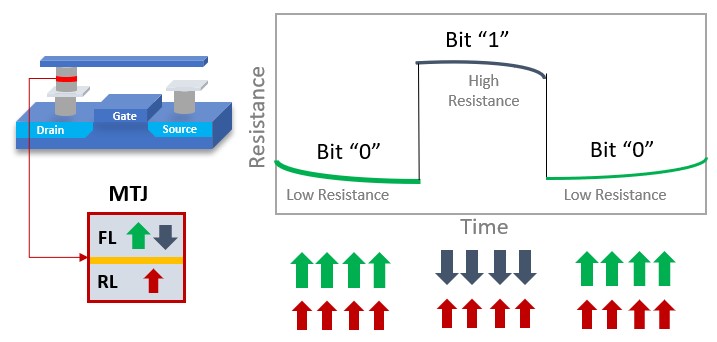

STT-MRAM 기술은 소자의 자기 상태를 이용해 정보(비트)가 저장되는 저항 메모리이다. 이 소자는 비변동성, 고속, 신뢰성, 확장성 및 저전력 소비를 동시에 연결하는 기본 스핀트로닉 소자인 자기 터널 정션(Magnetic Tunnel Junction: MTJ)을 기반으로 한다. MTJ는 CMOS 제조 공정의 상호 연결 수준에서 집적된 것으로 샌드위치처럼 구조화되어 있으며 자유층(FL)과 참조층(RL)이라고 불리는 두 개의 강자성 층이 터널 장벽 역할을 하는 얇은 절연체에 의해 분리되어 있다.

이 소자는 자유 층과 참조 층의 자화가 같은 방향(Parallel: P) 일때 낮은 저항 상태로 되며 반대 방향(Anti-Parallel: AP) 일 때 높은 저항 상태로 된다. 칩 동작에서 STT-MRAM은 트랜지스터 기반 메모리 기술과 같이 전기적으로 프로그래밍된다. 그러나 STT-MRAM에 저장된 정보의 자기 특성으로 인해 STT-MRAM 칩 제조 과정에서는 외부 자기장을 적용해야 하는 몇 가지 새로운 전기 테스트가 필요하다. 이러한 테스트는 물리적 매개 변수를 추출하고 테스트 속도를 가속화하며 자기 내성을 평가하는 것을 목표로 한다.

STT-MRAM의 기본 매개 변수

STT-MRAM은 두 가지 저항 상태(P와 AP)를 가지는데 그림에서 보듯이 이 두 상태 간의 비율은 RAP 과 RP이 AP와 P 상태에서 각각 저항 값을 가지는 터널 마그네토 저항(Tunnel Magneto Resistance: TMR)으로 정의된다.

P에서 AP 상태로 전환하기 위해서는 두 상태 간의 에너지 장벽 EB 을 초과하는 최소 전류가 필요하다. 제조 공정과 관련된 파라미터에 의존하는 EB 는 열 안정성 계수를 통해 메모리 포인트의 보존 시간 성능에 핵심적인 역할을 하게 된다.

kB가 볼트만 상수인 경우 T는 온도이고 t0는 역 시도 주파수이다. ∆ 값이 높을수록 MTJ의 자기 상태가 더 안정적으로 되는데 프로그래밍하기 위해 더 많은 에너지를 지속적으로 필요로 한다. 열 안정성 계수는 대상 애플리케이션에 따라 최적화될 수 있다. 예를 들어 구동 메모리 애플리케이션을 위한 데이터 보존 시간 요구 사항은 주로 확장성(고밀도 집적) 과 작동 속도를 요구한다. 그러나 자동차 또는 산업용 스토리지 메모리의 경우 열악한 환경에서 견고한 저장 용량이 주요 관심사가 된다.

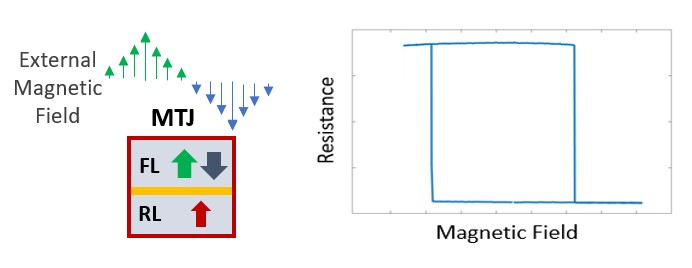

STT-MRAM MTJ의 TMR, 스위칭 능력, 안정성 요소는 MTJ 저항을 감지하며 소자표면(FL 및 RL에 평행)에 수직으로 외부 자기장을 변화시키면서 측정된 MTJ 측정의 히스테리시스 곡선을 통해 추출된다.

제조 공정에서의 MRAM 소자 수준 테스트 요구 사항

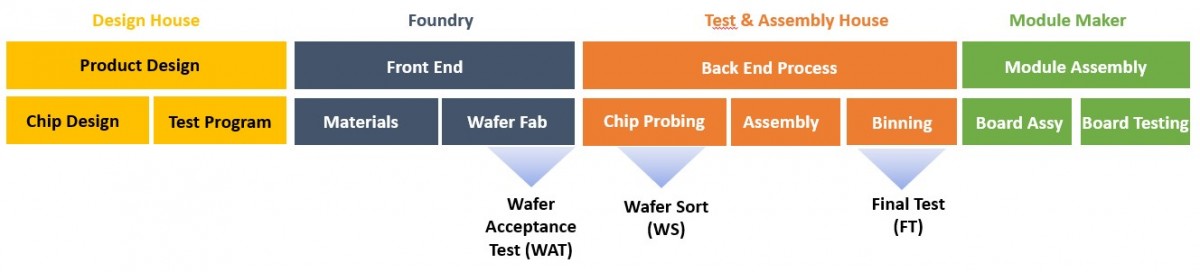

STT-MRAM을 집적하는 CMOS 또는 FD-SOI 기술에서 MTJ 전체 스택은 웨이퍼 팹 프로세스(전공정)의 마지막 단계에서 마무리된다.

소자 수준 테스트의 첫 번째 단계는 WAT(Wafer Acceptance Test: 웨이퍼 수용 테스트)에서 Rp, Rap, TMR 및 ∆ 와 같은 지정된 매개 변수 뿐 아니라 고장 전압을 포함한 여러 가지 매개 변수를 통해 제조 공정을 제어하는 것이다. 이 단계에서 STT-MRAM 칩을 대표하는 MTJ 테스트 구조는 자기 및 전기적 자극을 통해 히스테리시스 곡선을 추출하는 테스트 장치로 사용된다. 이 테스트에서 STT-MRAM 웨이퍼가 정렬된다. WAT에서의 경쟁력있는 테스트 시간을 달성하는 핵심 요소는 최단 시간에 히스테리시스 곡선을 측정하기 위해 소자 상단에 있는 자기장을 신속하게 변형하는 것이다.

후공정 프로세스에서는 웨이퍼 수율 관리를 위해 웨이퍼상의 칩을 테스트해야 한다. 이 테스트는 조립 공정 전의 칩 비닝을 목표로 하는 웨이퍼 정렬(Wafer Sort: WS) 테스트단계에서 수행된다. 최종 테스트(Final Test: FT)에서는 제품 제조 수율을 관리하기 위해 패키징으로 완성된 칩들이 테스트된다.

WS 테스트는 임베디드 로직 메모리의 기능성을 평가한다. 메모리 배열의 각 비트가 프로그래밍 및 읽기로 반복되는데 이 때 제조 프로세스 문제에서 발생한 영구 스위칭 오류의 비트 분류 목적으로 식별된다. STT-MRAM 스핀 전송 토크 스위칭의 확률적 성격에 의한 비지속성 스위칭 오류 현상은 ppm 범위를 초과하지 않도록 정량화, 확증된다.

STT-MRAM 어레이에서 각 비트의 보존 시간을 추출하는 것도 필수이다. 자동차 또는 스토리지 급 메모리와 같은 일부 응용 프로그램의 경우 10년 이상의 보존 시간이 필요하므로 테스트 기간 또한 길어질 수밖에 없다. 보존 테스트의 테스트 시간을 압축하기 위해서는 온도, 방해 전류, 외부 자기장과 같은 가속 계수가 중요한 변수가 된다.

FT는 칩을 방해하기 위해 외부 필드의 적용을 포함하는 자기 내성 테스트의 추가함으로써 WS를 보완한다. 외부 필드의 조건이 변경되는 동안 메모리 판독은 저장된 정보가 특정된 수준의 내성 범위보다 낮은 세기의 기생 필드에 의해 영향을 받지 않는다는 것을 검증하도록 반복된다.

Hprobe는 외부 필드 적용 조건 하에 구동되는 MRAM용 자기 자동 테스트 장비 개발 전문회사이다. Hprobe 마그네틱 테스터는 WAT, WS 및 FT 제어 단계를 위해 특별히 설계되었으며 STT-MRAM을 위한 최첨단의 효율적인 원가절감형 테스트 솔루션을 제공한다.

PDF 다운로드

회원 정보 수정