고속 제한 사항이 적용된 전자제품 설계시 고려해야 할 3가지 주의사항

글/PATRICK CARRIER, MENTOR GRAPHICS CORP.

서론

고속 전자제품을 설계할 때는 여러 가지 문제에 직면하게 된다. PCI-Express, DDRx, Serial ATA와 같은 고속버스는 수백 MHz에서 GHz 이상의 주파수로 동작하므로 타이밍 마진(timing margin)이 빠듯하다. 미세형상 실리콘(Fine-geometry silicon)을 사용하면 에지 레이트가 빨라진다. 게다가 점점 더 작고 저렴한 제품을 요구하는 시장의 압박이 심해지면서 PCB 레이아웃의 밀도는 점점 높아지고 있다. 고속 PCB를 성공적으로 설계하려면 이런 요인을 모두 감안해야 한다.

고속 설계 제한 사항이 적용되는 전자제품을 만들 때 특히 주의해야 하는 점은 신호 품질, 타이밍 및 누화(crosstalk), 이렇게 세 가지로 정리할 수 있다.

• 신호 품질에는 오버슈트(overshoot), 링백(ringback)과 비단조성(non-monotonicity) 등이 포함된다. 이는 수신기를 손상시키거나 데이터 오류를 유발하는 요인이 된다.

• 시스템 레벨에서 규정 준수를 보장하려면 종단(termination), 수신기 로딩 및 트레이스 임피던스와 길이의 효과 등을 포함한 타이밍을 PCB 레벨에서 엄격하게 분석해야 한다.

• 누화(Crosstalk)란 한 트레이스에서 다른 트레이스로 원치 않는 노이즈를 유도하는 것으로, 신호 품질과 타이밍 모두에 영향을 미칠 수 있는 요소이다.

이러한 영역을 분석하여 제품 신뢰성과 품질을 향상시킬 수 있다. 그리고 조건-결과(what-if) 시나리오를 테스트하여 라우팅 제약 조건을 만들고 레이아웃에서 이를 검증하여 전기적인 요구 사항을 만족하는지 보장할 수 있다. 분석을 통해 트레이스 길이, 토폴로지, 간격, 부품 배치에 대해 현명한 결정을 내릴 수도 있고 보드 스택업, 트레이스 너비 및 동박 무게와 같은 항목에 제한 사항을 적용할 수도 있다.

신호 품질

Digital logic은 데이터를 일련의 1과 0으로 변환한다. 이는 실제 시스템에서 고전압과 저전압으로 표현된다. 수신기가 전압이 1과 0중 어떤 값을 나타내는지를 판단하려면 해당 전압이 수신기의 로직 임계값(threshold)을 초과하거나 임계값 미만이어야 한다. 또한 해당 전압이 수신기 한계를 초과하면 수신기가 손상될 수 있다. 이 두 가지 요구 사항은 신호 품질 분석에 두 가지 근본적인 제한 사항을 제시한다. 하나는 링백, 다른 하나는 오버슈트이다.

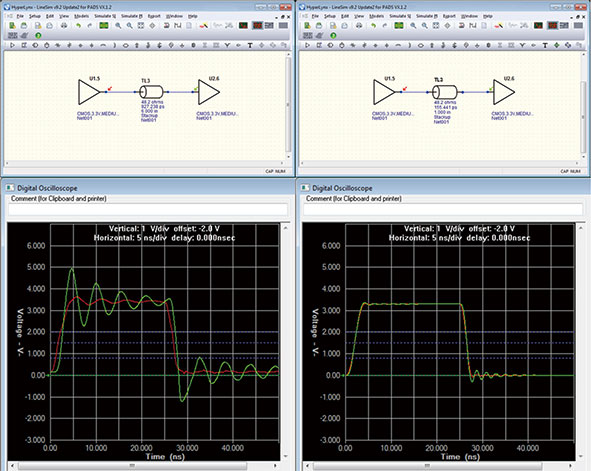

설계자나 엔지니어가 송신기를 수신기에 연결하면 왼쪽의 그림 1에 표시된 파형과 같은 결과가 나온다. 여기서는 링백과 오버슈트 모두 위반된 것을 알 수 있다. 이 파형에는 1V를 초과하는 음의 오버슈트가 발생하였다. 또한 이 파형은 로직의 낮은 임계값(lower logic threshold)인 0.8V로 링백한다. 이 토폴로지를 있는 그대로 사용하여 PCB를 설계하면 데이터 스트림 내에서 오류가 발생하며 수신기가 손상될 수 있다.

[그림 1] 신호 품질 문제가 있는 토폴로지(왼쪽)와 길이가 축소된 토폴로지의 깨끗한 신호의 토폴로지(오른쪽).

토폴로지 길이가 신호 에지(edge)의 길이보다 훨씬 아래로 줄어드는 경우, 수신기 파형이 극적으로 깨끗해진다. 이것을 오른쪽의 그림 1에서 확인할 수 있다. 다만 안타깝게도 이런 길이가 보통 인치 단위이므로, 설계에서 실현할 수 없는 경우가 많다.

수신기에서 신호를 깨끗하게 만드는 또 한 가지 방법으로는 종단(termi-nation)을 사용하여 드라이버와 수신기의 임피던스를 보드 트레이스와 일치시키는 것이다. 이렇게 하면 오버슈트와 링백 문제를 발생시키는 반사(reflection)를 제어할 수 있다. 또한 종단을 하면 토폴로지 길이를 훨씬 유연하게 조절할 수 있는데, 이는 트레이스 길이가 비현실적인 최대치에 제한되지 않으면서 더욱 깨끗한 신호를 얻을 수 있기 때문이다.

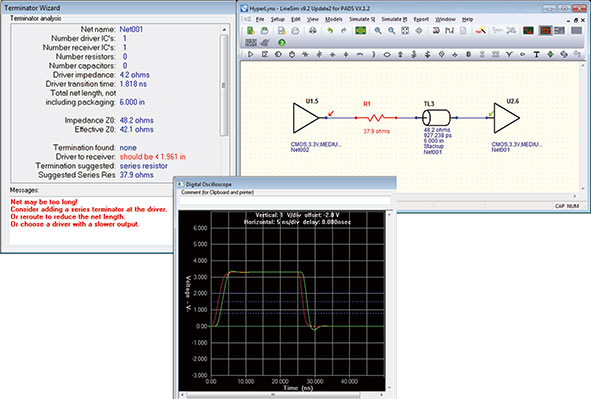

종단 값은 버스 설계 가이드라인에서 참고하거나, 관련 가이드라인이 없다면 분석 결과를 통해 결정해도 된다. PADS 플로우에 통합된 강력한 HyperLynx 기술은 이 방식을 한 단계 더 발전시켜 종단 마법사(Termination Wizard)라는 기능으로 구현하였다. 이 기능은 토폴로지를 보고 이상적인 종단 값을 자동으로 결정해준다. 트레이스 토폴로지 내에 포함된 터미네이터의 위치 또한 길이를 변화시켜 가며 결과를 분석해서 결정할 수 있다. 이 분석을 통해 터미네이터의 배치 위치를 결정하기 위한 최대 길이 규칙을 만드는 것이다. 마찬가지로 토폴로지 내의 다른 트레이스에 적용할 길이 제한 사항도 이를 통해 결정할 수 있다. 그림 2는 이에 대한 예시를 나타낸 것이다. 이러한 여러 가지 길이를 다양하게 탐구함으로써 신호 품질 요구 사항에 부합하면서도 가장 광범위한 솔루션 공간을 만들 수 있다.

[그림 2] 종단 처리된 깨끗한 신호의 토폴로지

타이밍

설계에 적용되는 대부분의 길이 제한 사항은 타이밍 요구 사항에 기인한다. 타이밍 요구 사항은 데이터가 특정한 간격을 두고 수신기에 ‘클럭 인’된다는 데서 비롯된다. 시스템이 데이터를 필요할 때 데이터가 없다면 시스템이 제대로 작동하지 않는다.

버스 타이밍 구조에는 크게 두 가지 종류가 있는데, 하나는 공통 클럭, 다른 하나는 소스 동기이다. 이 때문에 두 가지 유형의 레이아웃 제한 사항이 생긴다. 최소/최대 및 길이 매칭이다. 최소 및 최대 지연 제한 사항은 공통 클럭 버스 구조로 인해 생기는 제한 사항이다.

PCI가 이 종류의 한 예인데, 여기서는 공통 클럭 신호에 송신기로부터 데이터가 나와서 수신기로 전달된다. 데이터가 너무 일찍 도착하지 않도록 하고, 홀드 시간(hold time) 요구 사항을 위반하지 않도록 하려면 최소 길이 제한 사항을 만들어야 한다. 마찬가지로 데이터가 너무 늦게 도착하지 않도록 하기 위해 최대 길이 제한 사항을 만든다. 이러한 제한 사항은 단순히 선로의 길이를 근거로 하는 것은 아니다.

수신기 로딩이나 신호 품질 문제와 같은 다른 여러 가지 고려할 사항이 송신된 데이터가 수신기에서 유효하게 인정되는 시점을 결정한다. 따라서 이러한 길이를 적절하게 계산하려면 정확한 신호 분석이 매우 중요하다.

지연(delay) 일치 제한 사항은 소스 동기 버스에 기인한 제한 사항이다. 이런 버스(예: DDRx)는 데이터가 수신기에서 ‘클럭 인’하기 위해 데이터와 함께 클러킹 신호 또는 ‘스트로브(strobe)’를 보낸다. 이렇게 하면 드라이버와 수신기 사이의 복잡한 타이밍 관계가 없어지고, 스트로브가 데이터에 일치하기만 하면 된다. 다만 이런 인터페이스에는 다른 우려 사항이 동반되게 마련이다. 예를 들어 데이터의 유효 시점을 좌우하는 신호 품질이 대표적이다. 이와 같은 버스의 주된 타이밍 제한 사항은 지연(delay) 일치 제한 사항이다. 이 제한 사항은 버스 속도가 빨라지거나 신호 품질 문제가 생기면 더욱 까다로워진다.

누화(CROSSTALK)

트레이스 사이의 간격도 설계 레이아웃의 중요한 제한 사항이다. 이것은 신호 사이에 발생하는 누화의 양에 따라 결정된다. 누화에 영향을 미치는 요인은 여러 가지가 있다. 예를 들어 드라이버의 에지 레이트, 보드 스택업, 트레이스 사이 병렬 처리의 양, 그리고 트레이스 사이의 간격 등이 대표적이다.

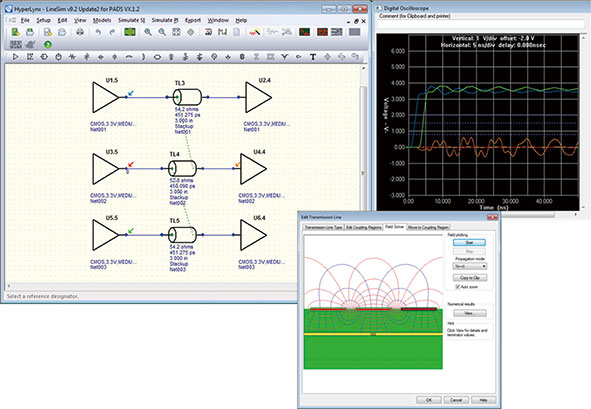

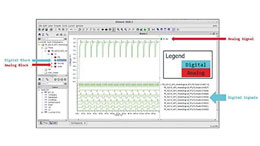

누화는 신호 품질과 타이밍 모두에 영향을 미치며, 주어진 net에서 허용된 누화의 양은 시뮬레이션을 통해 판단할 수 있다. 그림 3은 누화 시뮬레이션을 예시로 나타낸 것이다.

[그림 3] PADS Standard Plus와 PADS Professional의 누화 분석

누화 분석은 보통 ‘빅팀(victim)’ 트레이스 하나와 ‘어그레서(aggressor)’ 트레이스 두 개로 구성된다. 어그레서를 더 많이 포함할 수도 있지만, 대부분의 경우 누화의 95%는 가장 가까운 두 net에서 발생한다. 드라이버, 수신기에 모델 및 보드 스택업을 설정하고 트레이스 사이의 간격을 수정하며 시뮬레이션 돌리면 허용 가능한 누화 수준을 판단할 수 있다. 또한 서로 평행한 트레이스의 길이를 수정하고 그 효과를 관찰할 수도 있다.

이런 분석은 주로 트레이스 사이의 간격 지정 규칙을 도출하기 위해 실시하는 것이다. 이렇게 정한 간격 규칙을 지킬 수 없거나, 레이아웃을 좀 더 유연하게 구성하고자 하는 경우, 간격을 더 조밀하게 하고 최대 병렬성 제한 사항을 적용하여 규칙을 하나 만들 수 있다. 이와 같은 한 쌍의 제한 사항은 누화 분석을 통해 만들고, 수요의 변화에 따라 수정하면 된다.

배선 후(POST-ROUTE) 검증

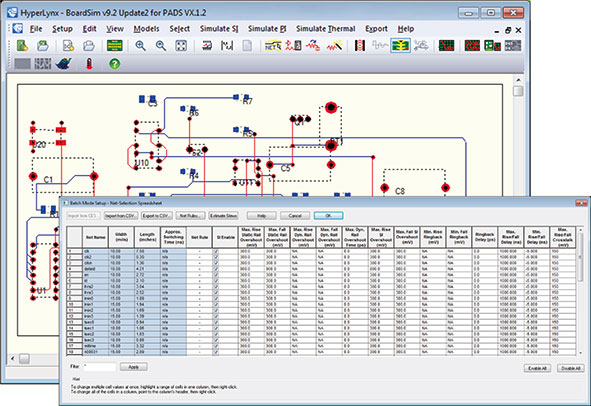

필요한 라우팅 제한 사항을 모두 만들고 해당 제한 사항을 사용해 보드를 라우팅한 뒤에는 보드가 해당 제한 사항을 유발한 전기적 요구 사항에 부합하는지 검증하는 것이 좋다. 보드상의 모든 net을 대상으로 배선 후(post-route) 분석을 실시하면 완벽한 마무리가 되는 셈이다. 그림 4는 PADS의 배치 모드(Batch Mode) 마법사를 예시로 나타낸 것이다.

그림 4를 보면 PADS에서 HyperLynx를 이용하여 레이아웃 데이터에 대해 직접 시뮬레이션을 실시한 다음 오버슈트, 지연 및 누화 제한 사항에 대해 설계를 검증한다는 것을 알 수 있다. 이와 같은 제한 사항을 위반하는 net이 발견되는 경우, 이러한 net을 한 번에 하나씩 시뮬레이션하여 좀 더 자세히 살펴볼 수 있다.

[그림 4] 배선후(post-route) 분석을 실시하면 라우팅된 보드가 전기적 요구사항 및 고속 제한사항에 부합하는지 확인 가능.

배선 후(post-route) 검증은 설계 주기 초반에 실시하는 엄격한 배선 전(pre-route), 즉 ‘가정(what-if)’ 분석을 훌륭하게 보완한다. 이는 또한 고속 버스를 분석하기 위해 수행하는 일련의 작업 중 한 단계이기도 하다. 이러한 유형의 분석 및 결과로 생성된 제약 조건 없이는 현대 디지털 시스템은 오늘날의 비용, 크기 및 성능 요구를 충족 시키도록 설계될 수 없다.

PADS의 유용한 활용

PADS 제품 제작 플랫폼은 전기 제품을 설계할 때 수반되는 문제를 해결하기 위해 필요한 툴을 제공하여 모든 설계자와 전기 엔지니어에게 경쟁 우위를 부여한다. PADS는 개념부터 제조까지 설계 주기 전반에 걸쳐 품질과 신뢰성을 확보하는 데 도움이 된다.

각자의 요구 사항과 예산에 맞는 완벽한 구성을 선택하여 사용할 수 있다. 확장 가능하고 직관적인 솔루션을 통해 PCB 중심 전자제품을 설계, 검증 및 제조하는 데 필요한 동력을 제공하고, 사용이 간편한 스위트 형식으로 제공되어 가끔 사용하는 설계자도 생산성을 높이는 데 필요한 시간을 단축할 수 있다.

글로벌 기업에 근무하는 고객은 물론 기가비트 단위, SERDES, 전자기 및 전기 규칙 설계 문제를 다루는 고객을 위해 다양한 솔루션이 준비되어 있다. 자세한 정보는 담당 영업 직원에게 문의하시기 바란다.

아날로그 설계를 위한 EDA 툴은 어떻게 진화하고 있는가?

조회수 807회 / Siemens EDA

전자제품 인터페이스의 설계 라이프사이클

조회수 598회 / David Wiens

전기 디자인 룰 체크(DRC)를 자동화하는 방법

조회수 1253회 /

지멘스EDA 수석부사장.jpg)

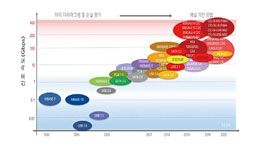

2022년 시스템 및 설계 툴, 방법론의 시장 전망

조회수 1247회 / 지멘스

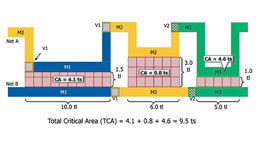

임계 영역을 이용한 자동차 IC의 테스트 품질 향상

조회수 1682회 / RON PRESS

SERDES 디자인을 위한 더 효율적인 솔루션이 있을까요?

조회수 1752회 / Neil Fernandes

지멘스 EDA 포럼 2021 열려, ‘Silicon to Systems’ 주제로 최신 설계 방...

조회수 1149회 / Joseph Sawicki

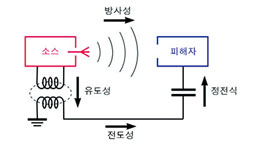

자동화된 EMC 분석을 PCB 레이아웃에 추가

조회수 1229회 / SIEMENS

DFT를 향한 성능 저하 없는 상향식 접근방식

조회수 2547회 / Geir Eide

PDF 다운로드

회원 정보 수정