SoC 디자인의 동적 전력을 정확히 추정하기 위한 새로운 접근 방법

글/라우로 리자티(Lauro Rizzatti), 검증 컨설턴트

새로운 툴들은 파일 기반의 플로우를 없앰으로써완전한 RTL 전력 방식 모색과 정확한 게이트 레벨의 전력 분석 프로세스를 제공한다.

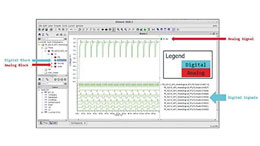

필자는 최근 올린 글에서 동적 전력소비를 추정하기 위한 현재의 접근 방법이 갖고 있는 본질적인 한계를 집중 조명한 바 있다. 간단히 말하자면, 이 접근 방법은 두 단계를 거쳐 진전되는 파일 기반의 플로우로 구성되어 있다. 첫째, 시뮬레이터나 에뮬레이터가 스위칭 동작을 추적하는데, 이는 전체 실행이 스위칭 동작 상호교환 포맷(SAIF) 파일에 누적 방식으로 기록되거나, 혹은 각각의 신호가 고속 신호 데이터베이스(FSDB) 파일에 주기별(cycleby-cycle) 기반으로 기록된다. 나중에 SAIF 파일이 입력된 전력 추정 툴에서 전체 회로의 평균 전력 소비를 계산하거나 혹은 FSDB 파일을 이용하여 해당 디자인의 시공간 상의 최고 전력을 계산하게 된다(그림 1).

이러한 기법들은 검사 대상 디자인(DUT)이 비교적 작고(대략 수백만 게이트 이하의) 분석이 최대 백만 클럭 주기 정도의 제한된 시간대 내에서 수행될 경우에는 허용될 수 있다. 이 같은 시간대는 DUT가 적응형 기능 테스트벤치를 이용해 테스트될 경우 전형적으로 볼 수 있다.

그러나 운영체제를 부팅하거나 수십억 사이클을 필요로 하는 애플리케이션을 실행하는 경우와 같은 임베디드 소프트웨어를 실행하는 게이트 수가 수천만 개나 수억 개에 이르는 오늘날의 대형 SoC 디자인 중 하나에 적용될 경우에는 다음 세 가지 문제로 인해 기존의 접근 방법으로는 실행이 불가능하다.

1. SAIF는 말할 것도 없고 FSDB 파일의 크기가 엄청나게 커져 관리가 불가능해진다.

2. 파일 생성 프로세스가 굼벵이처럼 느려져 몇 시간이 걸리거나 심지어는 하루 해를 넘길 수도 있다.

3. 전력 추정 툴에 파일을 로드하는 데 며칠 또는 일주일 이상도 걸릴 수 있다.

이는 도저히 가망이 없는 일처럼 보인다.

하지만 2015년 5월 27일에 멘토 그래픽스가 Veloce Power Application을 발표하면서 상황은 바뀌었다. 이 소프트웨어 패키지는 Veloce Activity Plot과 Veloce OS3 위에 놓여있는 Dynamic Read Waveform API(application programming interface)로 구성되어 있다(그림 2).

Veloce Power Application은 기존의(논란의 소지가 많은) 전력소비 추정 접근 방법에 영향을 미치는 핵심 문제들을 해결해 준다. 이것은 Veloce에뮬레이터를 전력분석 툴에 긴밀하게 통합시킴으로써 2단계의 파일 기반 플로우를 없애준다.

따라서 설계 팀들은 더 이상 거대한 파일들과 씨름할 필요가 없다. 즉, 더 이상 낭비되는공간도 없고 파일을 생성하고 로드 하느라 며칠을 낭비할 필요도 없는 것이다. 이 새로운 접근방법은 오늘날의 SoC 디자인이 소비하는 전력을 신속하고도 철저하게 추정하기 위한 빠르고 깨끗하며 매우 효과적인 방법을 제공한다.

Veloce Activity Plot

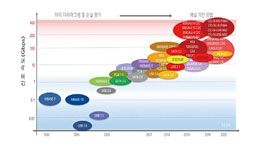

Veloce Activity Plot은 간단한 차트 하나에 시간 경과에 따른 전역적 설계 스위칭 동작을 발생과 동시에, 예컨대 OS를 부팅하고/하거나 라이브 애플리케이션을 실행하면서 매핑해 넣는다(그림 3).

이 플롯으로부터 설계 팀에게 전력 상의 문제를 안겨줄 수 있는 활발한 스위칭 동작이 발생하는 시간 프레임들을 식별할 수 있다. 이 차트 자체는 특별한 것이 아니지만, 그 생성 속도는 파일 기반의 전력 차트 생성 속도보다 수십 배나 빠르다. 데이터 포인트로서, Veloce가 1억 게이트 디자인에 대해 7,500만 클럭 사이클 동안의 Activity Plot을 생성하는 데 걸리는 시간은 15분이다. 전력 분석 툴로 이와 비슷한 정보를 생성하려면 일 주일 이상이 걸릴 수 있다. 게다가 이처럼 대용량의 데이터는 아예 다루지 못할 수도 있다.

그렇다면 다음 질문은 DUT에서 발생하는 최고 값들이‘어디에’있으며, ‘무엇이’이를 야기하는가 하는 것이다. 이 문제는 Dynamic Read Waveform API에 의해 다뤄진다...(중략)

아날로그 설계를 위한 EDA 툴은 어떻게 진화하고 있는가?

조회수 814회 / Siemens EDA

전자제품 인터페이스의 설계 라이프사이클

조회수 598회 / David Wiens

전기 디자인 룰 체크(DRC)를 자동화하는 방법

조회수 1259회 /

지멘스EDA 수석부사장.jpg)

2022년 시스템 및 설계 툴, 방법론의 시장 전망

조회수 1247회 / 지멘스

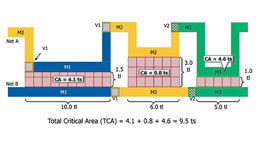

임계 영역을 이용한 자동차 IC의 테스트 품질 향상

조회수 1682회 / RON PRESS

SERDES 디자인을 위한 더 효율적인 솔루션이 있을까요?

조회수 1753회 / Neil Fernandes

지멘스 EDA 포럼 2021 열려, ‘Silicon to Systems’ 주제로 최신 설계 방...

조회수 1149회 / Joseph Sawicki

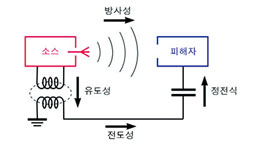

자동화된 EMC 분석을 PCB 레이아웃에 추가

조회수 1230회 / SIEMENS

DFT를 향한 성능 저하 없는 상향식 접근방식

조회수 2552회 / Geir Eide

PDF 다운로드

회원 정보 수정