메인스트림시스템및플랫폼디자이너에게획기적인 생산성 향상을 선사하는 비바도(Vivado) HLx 에디션

비바도 디자인 수트 HLx 에디션

비바도 디자인 수트(VivadoⓇ Design Suite)는 차세대 C/C++ 및 IP 기반 디자인의 생산성을 획기적으로 향상시켜주는 새로운 접근법을 제공한다. 새로운 HLx 에디션은 HL 시스템 에디션 및 HL 디자인 에디션,HL WebPACKTM 에디션을 포함하고 있다. 사용자는 새로운 UltraFastTM 하이-레벨 생산성 디자인 방법론 가이드(High-Level Productivity Design Methodology Guide)를 이용해 기존의 접근방식 대비 10배에서 15배의 생산성 향상을 실현할 수 있다.

주로 디자인 프로세스 후반부에 대부분의 디자인 작업이 집중되어야 하는 기존의 RTL 기반 디자인과 달리, C 및 IP 기반 디자인은 검증 및 구현, 디자인 컨버전스 등의 개발주기를 단축시켜주기 때문에 디자이너들은 로직의 차별화에 주력할 수 있다. 플로우는 다음과 같다:

•필요한 소프트웨어스택과 함께 빠른 플랫폼 커넥티비티 디자인

•하이-레벨 디자인을 이용해 빠르게 차별화된 로직 개발. 또한 뛰어난 디자인 재사용 능력 제공

•RTL과 비교해 하이-레벨 언어로 검증 시간을 획기적으로 단축

디자인 팀은 하이-레벨 추상화를 이용해 신속하게 전반적인 성능을 향상시키거나, 성능, 전력, 활용도 측면에서 동일한 품질 결과(QoR; Quality of Results)를 얻을

수 있다.

UltraFast 하이-레벨 생산성 디자인 방법론 가이드

기존 디자인 개발방법은 숙련된 시스템 설계자와 함께 새로운 기술을 어떻게 구현해야 할지 평가하고, 하이-레벨 모델링 구성방식으로 보다 뛰어난 차별화된 로직과 시스템 커넥티비티 요건을 모두 파일화하여 시작하게 된다. 그런 다음 RTL 디자인에서 이러한 요건을 구현한다. RTL 디자인 사이클은 보통 각 블록은 물론,.....

알베오 U55C의 출시로 HPC 업계에 많은 가치 제공할 것

조회수 813회 / Nathan Chang

엣지 센서에서 CPU 가속기까지 ‘버설 AI 엣지 시리즈’

조회수 1020회 / Rehan Tahir

적응형 컴퓨팅, 포스트-무어의 법칙 시대에서 성장을 주도하다

조회수 1363회 / Victor Peng

데이터센터 혁신을 위한 장벽 없는 FPGA 솔루션

조회수 1005회 / Kartik Srinivasan 외 2인

자동차 시장의 혁신을 선도하는 자일링스의 DNA

조회수 741회 / Yousef Khalilollahi

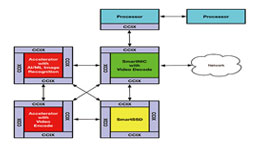

CXL, CCIX 기반 PCIe 5와 SmartNIC은 어떻게 가속 솔루션을 혁신하고 있...

조회수 6811회 / Scott Schweitzer

대규모 5G 무선 구축을 위한 혁신적인 징크 RFSoC DFE

조회수 1495회 / Gilles Garcia

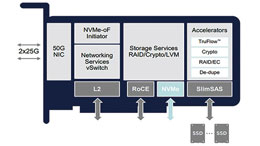

SmartNIC 아키텍처: 가속기로의 이행, 그리고 FPGA가 우위를 점하는 이유

조회수 4471회 / Scott Schweitzer

SmartNIC이 일반 NIC보다 뛰어난 이유는?

조회수 1869회 / Scott Schweitzer

PDF 다운로드

회원 정보 수정