비용에 최적화된 포트폴리오: BoM 비용 절감의 핵심 요소

글/자일스 페캄(Giles Peckham), 아담 테일러(Adam Taylor), 자일링스

임베디드 시스템은 기존 마켓은 물론, 새롭게 부상하는 신규 마켓에서도 빠르게 성장하고 있다. 시장 분석가들은 임베디드 시스템 시장이 오는 2021년까지 2,250억 달러 규모에 이를 것으로 전망하고 있다. 이러한 성장세는 IoT(Internet of Things)를 비롯해 IIoT(Industrial IoT), 인더스트리 4.0(Industry 4.0), CPS(Cyber Physical System)와 같은 업계의 주요 이슈들의 지속적인 개발과 첨단 비전 기반 시스템이 확산되면서 가속화되고 있다.

대부분의 이러한 애플리케이션은 에지 상에 고성능 시스템을 배치해야 한다. 구축량이 방대한 애플리케이션의 경우, 솔루션의 반복적인 엔지니어링 비용이 특히 중요하며, 이는 솔루션의 실현 가능성을 좌우하기도 한다.

반복되는 엔지니어링 비용을 줄일 수 있는 한 가지 방법은 구성요소 통합을 비롯해 시스템 레벨의 더욱 긴밀한 통합을 구현하는 것이다. 일반적인 임베디드 시스템은 프로세서와 디지털 로직, 인터페이스, 휘발성 및 비휘발성 메모리와 혼합신호 부품, 센서를 비롯해 클럭이나 전원공급장치와 같은 지원 소자들로 구성된다. 따라서 더욱 긴밀한 통합을 통해 복잡성을 줄임으로써 PCB와 어셈블리 비용을 절감할 수 있다.

비용에 최적화된 포트폴리오를 제공하는 자일링스의 FPGA(Field Programmable Gate Array)와 같은 올 프로그래머블(All Programmable) 디바이스와 이기종 SoC(System on Chip)는 성능 요건을 충족하면서도 보다 긴밀한 시스템 통합을 구현할 수 있게 해준다. 또한 이러한 디바이스는 다양한 애플리케이션 요구사항에 맞게 조정이 가능하다:

• I/O 최적화 - 스파르탄-6(SpartanⓇ-6) 및 스파르탄-7 제품군에서 제공

• 트랜시버 최적화 - 기가비트 트랜시버를 제공하는 아틱스(ArtixⓇ) 제품군에서 지원

• 시스템 최적화 - 듀얼 코어 Cortex™-A9 및 단일 코어 Cortex-A9을 지원하는 징크-7000(ZynqⓇ-7000) SoC 제품군에서 제공

이러한 포트폴리오는 클라우드 컴퓨팅에서 이미지 프로세싱, 센서 융합, 정밀 제어, 안전 및 보안 애플리케이션까지 모두 처리할 수 있다.

이러한 디바이스 제품군을 사용하면, 다음과 같은 기능을 수행할 수 있어 긴밀한 시스템 통합이 가능하다:

• 프로세서 통합 - 동일한 디바이스 내에 프로세서와 디지털 로직을 통합. 이는 마이크로블레이즈(MicroBlaze™) 소프트코어 32bit 프로세서나 징크-7000 Cortex-A9 코어를 이용해 구현할 수 있다.

• 혼합신호 통합 - 7 시리즈 디바이스 내의 아날로그 기능을 활용. XADC 아날로그 혼합신호 모듈은 17개의 디퍼렌셜 입력 간 내부 멀티플렉싱이 가능한 듀얼 1MSPS ADC를 제공한다.

• 인터페이스 간소화 - 프로그래머블 로직은 I/O 구조에서 직접 지원되는 다양한 표준을 통해 모든 인터페이스를 지원할 수 있다. 또한 프로그래머블 로직 내에서 프로토콜 기능도 구현할 수 있어 기존 인터페이스는 물론, 맞춤형 및 표준 인터페이스를 쉽게 구현할 수 있다. 이러한 유연성을 통해 HDMI나 MIPI DPHY와 같은 필요한 디스크리트 PHY 디바이스 수를 줄일 수 있다.

• 메모리 아키텍처의 간소화 - 통합 접근방식을 이용하면, 애플리케이션 소프트웨어 및 FPGA 비트스트림을 동일한 비휘발성 메모리에 저장할 수 있다. 또한 DDR과 같은 휘발성 메모리는 프로세서와 FPGA 애플리케이션 간에 공유할 수 있다.

• 클럭킹 아키텍처의 간소화 - 단일 디바이스로 통합하면 디지털 로직 및 프로세서를 위한 별도의 오실레이터가 필요하지 않으며, 클럭킹 관리 타일과 PLL(Phase locked loop) 및 MMCM(Mixed-Mode Clock Manager) 프로비전을 이용해 추가 시스템 클럭을 생성하고, 신속하게 출력 주파수 및 위상을 조정할 수 있다.

이러한 통합 애플리케이션 개발을 위해 비바도(VivadoⓇ) 라이브러리 내에서 제공되는 다양한 IP 코어를 활용할 수 있다. 또한 알고리즘 및 이미지/신호 프로세싱 애플리케이션의 경우 C나 C++과 같은 하이-레벨 언어를 이용해 기능을 정의할 수 있는 HLS(High-Level Synthesis)를 사용할 수 있으며, 이를 통해 전반적인 개발 시간을 단축할 수 있다...(중략)

알베오 U55C의 출시로 HPC 업계에 많은 가치 제공할 것

조회수 811회 / Nathan Chang

엣지 센서에서 CPU 가속기까지 ‘버설 AI 엣지 시리즈’

조회수 1016회 / Rehan Tahir

적응형 컴퓨팅, 포스트-무어의 법칙 시대에서 성장을 주도하다

조회수 1362회 / Victor Peng

데이터센터 혁신을 위한 장벽 없는 FPGA 솔루션

조회수 1003회 / Kartik Srinivasan 외 2인

자동차 시장의 혁신을 선도하는 자일링스의 DNA

조회수 739회 / Yousef Khalilollahi

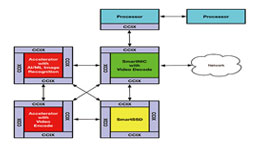

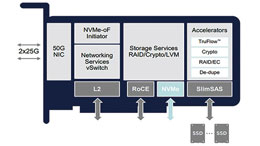

CXL, CCIX 기반 PCIe 5와 SmartNIC은 어떻게 가속 솔루션을 혁신하고 있...

조회수 6794회 / Scott Schweitzer

대규모 5G 무선 구축을 위한 혁신적인 징크 RFSoC DFE

조회수 1492회 / Gilles Garcia

SmartNIC 아키텍처: 가속기로의 이행, 그리고 FPGA가 우위를 점하는 이유

조회수 4465회 / Scott Schweitzer

SmartNIC이 일반 NIC보다 뛰어난 이유는?

조회수 1864회 / Scott Schweitzer

PDF 다운로드

회원 정보 수정