RFSoC , 5G 무선통신을 위한 획기적인 통합 및 아키텍처 혁신

글/스티브 글레이저(Steve Glaser) 기업전략마케팅 그룹 수석부사장

아론 버만(Aaron Behman) 임베디드 비전 부문 전략 마케팅 그룹 이사

업계가 5G 표준에 점점 집중하면서 모바일 장비 제조업체는 기술 시험 및 개념 입증 테스트에 상당한 관심을 보이고 있다. 이러한 구현의 상용 가능성은 현재 평가 중에 있지만, 프로토타입핑(prototyping)에 사용되는 기술의 상당 부분이 상용화 단계로 옮겨가지는 못할 것이다. 그 목적이 스펙트럼 효율성과 초고밀화, 새로운 스펙트럼을 통해 저전력에서 네트워크 용량을 늘리는 것이기 때문에 제조사들은 소프트웨어와 하드웨어, 시스템 레벨에서 획기적인 발전을 기대하고 있다.

매시브 MIMO 안테나 어레이는 이러한 기술 중에서도 공격적인 네트워크 용량 목표를 충족하는 데 중요한 기술이다. 안테나 어레이에 인터페이스 되는 전파 장치는 매우 공격적인 전력 및 풋프린트(footprint) 요건을 충족해야 하는데, 이러한 목표는 시스템 통합에서 혁신 없이는 힘들다. 자일링스는 5G 및 5G 이전 기술의 구현과 시험, 상용화에서 끊임없이 중요한 역할을 하며 네트워크 설계의 유연성과 프로그래밍 능력을 높이고 있다.

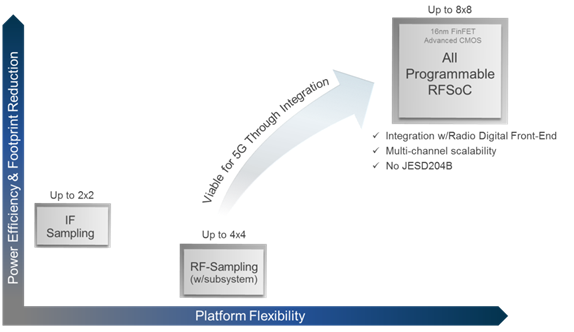

자일링스는 매시브 MIMO 시스템을 상용화하기 위해 RF급 아날로그 기술을 적용한 최초의 올 프로그래머블 RFSoC를 출시하며, SoC에 고성능 ADC 및 DAC를 성공적으로 통합시켰다. 직접적인 RF 샘플링 기술로 단품 데이터 컨버터를 제거한 RFSoC는 50-75%의 전력 및 풋프린트를 줄이고 매시브 MIMO 5G 전파 및 밀리미터파 무선 백홀의 핵심을 제공한다. 한편 SoC와 직접적인 RF 신호 처리의 조합은 디지털 도메인에서 완벽한 유연성을 발휘해 무선 인프라에서 상용 가능한 소프트웨어 정의 전파에 더 가깝게 다가가고 있다.

전력 및 풋프린트 – 5G 상용화의 핵심

기존의 4G RAN(radio access networks)은 일반적으로 손실이 큰 동축 케이블을 통해 원격 전파 헤드에 유선으로 연결하는 방식이다. 이 원격 전파 아키텍처는 3G에서 진화된 것이지만 여전히 접근 방식에는 문제가 있다. 여전히 안테나에서 원격 전파 헤드까지의 전력 소실이 크고, 시스템의 부피 때문에 조밀한 배치가 어렵다.

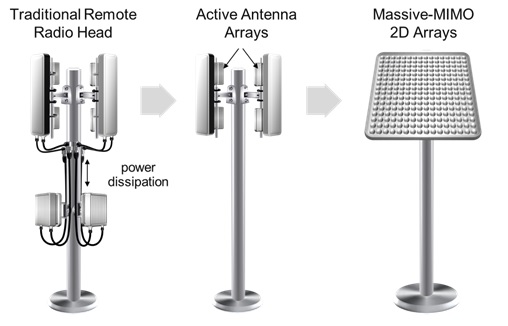

그림 1처럼, RAN 진화 과정의 다음 단계는 액티브 안테나 어레이를 활용한 디지털 및 아날로그 전파 장치를 그 안테나에 더 가깝게 이동시켜 공간을 절약하고 케이블 손실 및 관련 전력 손실을 피해 예산을 개선하는 것이다. 액티브 안테나 어레이는 4G에서 성공했지만, 5G 요건 중 일부의 연결 디바이스 수 및 사용자 데이터 속도의 증가는 해결하지 못했다.

그림 1: 리모트 라디오 헤드와 안테나 시스템의 진화

매시브 MIMO 및 빔포밍 기술은 이 솔루션에서 큰 부분이다. 그림 1에서 “매시브” MIMO 구성은 2D 어레이에서 32개, 256개, 최대 1024개의 개별 [물리적] 안테나를 통합하는 경향이 있다. 이러한 단계별 어레이 속성으로 고해상도 빔의 조정과 낮은 전력 소비가 가능해지며, 이것은 셀 당 용량을 크게 늘려줄 수 있는 초고밀도 설치를 가능하게 한다.

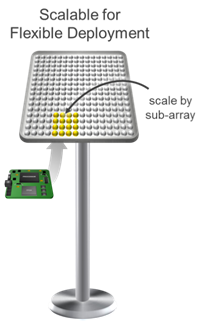

그림2: 유연한 배치를 위한 서브 어레이의 확장

2D 어레이 구조에서는 ‘타일’을 통해 건물 측면이나 형태가 불규칙한 옥외광고판, 간판 등에 고정시키는 등 기존의 레이아웃과는 다른 새로운 네트워크 토폴로지가 가능하다. 대규모 MIMO 어레이를 지원하기 위해 원격 전파 장치는 유연하고 확장 가능한 안테나 구성으로 서브 어레이를 지원하는 기능과 소형화가 필요하다.

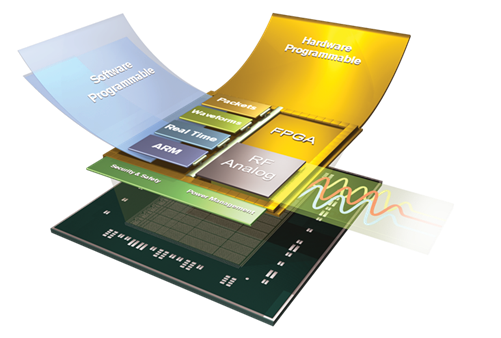

최초의 올 프로그래머블 RFSoC

올 프로그래머블 RFSoC는 다음과 같은 문제를 해결한다. 이 디바이스는 디지털 처리 서브시스템, 강력한 ARM급 처리 시스템, FPGA 패브릭과 같은 통신 등급 RF 샘플링 데이터 컨버터를 모두 하나의 모놀리식 디바이스에 결합한다. 최종 결과는 획기적인 통합이다. 특히 아날로그 디지털 신호 체인은 아날로그 설계자가 유연하게 구성할 수 있도록 강화된 DSP 서브시스템에 의해 지원된다. 이를 통해 시스템 전력 및 시스템 풋프린트가 50-75% 감소하고, 진화하는 사양과 네트워크 토폴로지에 맞추는데 필요한 유연성도 제공한다.

그림 3: 최초의 올 프로그래머블 RFSoC 출시

전력과 폼팩터(form factor), 설계 사이클의 감소

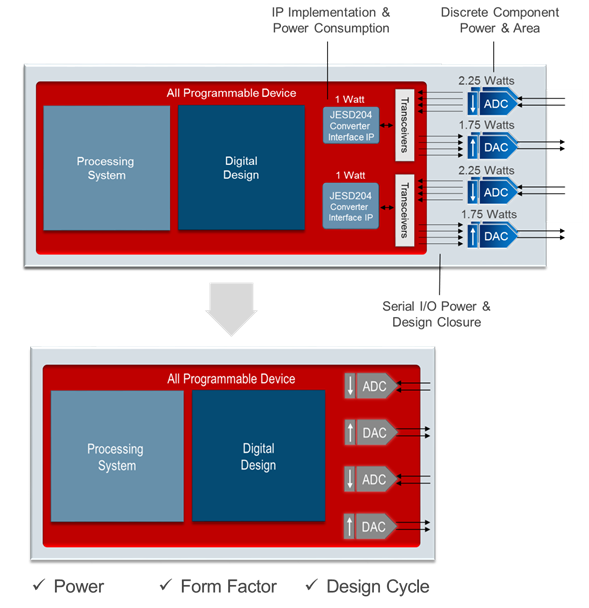

기존 전파 시스템에는 프로세스, 구성 가능한 로직, 커넥티비티 IP, 데이터 컨버터가 있다. 일반적인 단일 채널 ADC는 높은 RF 주파수에서 작동할 때 ~2W를 소비하고, DAC는 ~1.25W를 소비한다. 통합을 통한 부품 감소로 인해 전력 및 폼팩터가 감소하고, 높은 채널 수 시스템에서 그 영향이 극적으로 커질 수 있다. 그러나 이러한 장점 외에도 통합이 시스템 설계를 크게 단순화시킨다.

다수의 단품 컨버터에 인터페이싱 하는 것이 적지않은 I/O 문제가 있기 때문이다. 대역폭으로 확장하기 위해 대부분의 최신 컨버터는 JESD204B 프로토콜을 기반으로 최대 12.5Gb/s까지 고속 직렬 인터페이스를 사용한다. 이 방식의 문제점은 많다. 첫째, JESD204B IP 코어는 구현에 시간이 많이 들고, 이전의 FPGA 패브릭을 사용하며, 상당한 전력을 소비한다. 둘째, 직렬 I/O 전력은 높은 데이터 속도에서 크게 증가한다. 그러나 가장 큰 어려움은 직렬 링크를 연결하는 것이다. 12.5Gb/s에서 신호 왜곡이 문제가 되며, 주로 저가의 손실이 많은 구리 상호 연결로 높은 회선 속도를 실행하기 때문이다. 이 프로세스가 귀찮기 때문에 아날로그 설계자는 이를 없애고 싶어한다.

그림 4: 통합을 통한 전력, 폼팩터, 설계 주기의 감소

컨버터의 통합으로 JESD204B IP 코어와 직렬 트랜시버가 필요하지 않아, 설계 사이클과 개발 시간이 크게 단축된다.

최대 50%의 전력 감소

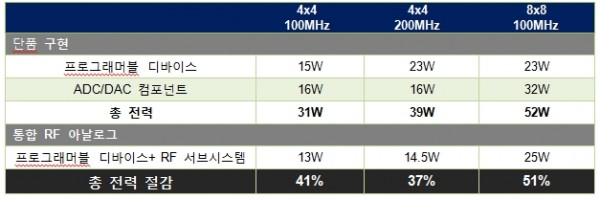

전형적인 4-송신, 4-수신(4Tx/4Rx) 안테나 구성에서는 단품 ADC와 DAC가 소비하는 전력이 매우 커서, 표 1처럼 통합해 전력을 40% 줄일 수 있다. 채널 수가 증가하면 단품 컨버터의 전력은 8Tx/8Rx 시스템에서 50% 이상으로 전력 감소가 됨을 알 수 있듯이, 무선 디지털 프론트 엔드 자체의 출력을 초과할 수 있다.

표 1: 통합 서브시스템을 이용한 디지털 라디오(DPD 이용)에서의 전력 감소

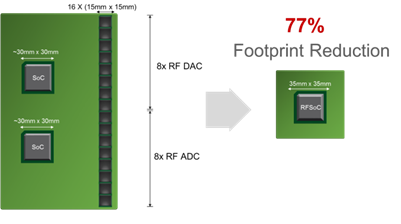

최대 75%의 폼팩터 감소

폼팩터는 트랜시버 및 안테나 수에 따라 당연하게 더욱 줄일 수 있다. 더 많은 컨버터가 제거되기 때문이다. 전형적인 RF ADC나 DAC는 시중의 디바이스 기준으로 채널 당 보드에서 최대 15x15mm를 차지할 수 있다. 4Tx4Rx 라디오의 경우 폼팩터를 약 50% 정도 줄일 수 있지만, 그림 5의 더 큰 라디오 구조의 경우, 8Tx/8Rx 폼팩터에서 급격히 폼팩터를 줄일 수 있어 완전히 배치 가능한 멀티 채널 시스템은 75% 이상 줄일 수 있다. 5G에서 멀티 서브 어레이로 구성된128Tx/128Rx 시스템을 고려하면 면적 감소가 극적으로 커질 수 있다. 그리고 10, 20, 30개 이상 디바이스를 필요로 하는 프로토타입의 경우 개별 안테나 구성 요소가 매우 작고 이용 가능한 면적이 최소화되므로 면적은 더욱 극적으로 줄어 들어야 한다.

그림 5: 8Tx8Rx 전파의 폼팩터 감소

직접적인 RF 샘플링의 가치

폼팩터와 전력, 생산성 외에도, 첨단 RF 샘플링 기술 기반의 컨버터 서브시스템의 자체 장점도 있다. 이러한 현대적인 샘플링 방식에서 입출력 RF 신호는 사전에 아날로그 부품을 이용한 신호 조절 없이 ‘다이렉트’ 샘플링 된다.

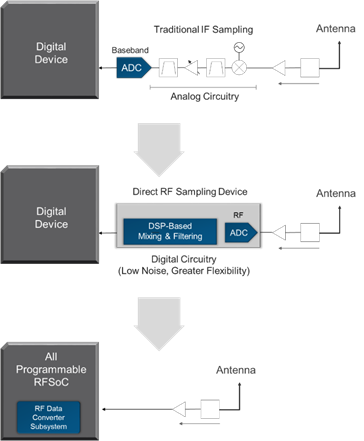

그림 6: 다이렉트 RF 샘플링과 시스템의 안테나로 이동

현재까지 대부분의 시스템은 중간 주파수(Intermediate Frequency)(‘IF’ 또는 ‘Zero-IF’) 샘플링이라는 아날로그 기반 전략을 구현한다. 여기서 원래의 신호가 ADC 샘플 속도에 의해 지원되는 주파수로 다운 변환된다. 다운 변환 회로는 믹서, 고품질 오실레이터, 기타 아날로그 부품으로 이루어져 있다. 이 아날로그 회로는 비교적 유연성이 떨어져 특화된 설계와 복잡한 부품 선정을 필요로 한다.

새로운 직접적인 RF 샘플링 방식에서는 입력되는 RF 신호가 초기의 다운 변환 없이 직접 샘플링 된다. 이 신호가 디지털화 되면, 다운 변환과 신호 처리는 디지털 신호 처리를 이용해 보다 유연하고 프로그래밍 가능한 디지털 도메인에서 이루어진다. 이 RF ADC가 지원하는 샘플 속도가 높을수록, 디지털 도메인에서의 우수한 필터링 기술로 다이내믹 레인지, 신호 품질(SNR), 신호 대역폭 간의 균형이 개선된다.

자일링스는 디지털 도메인에서 완벽한 유연성을 누리면서도 라디오 프로세싱을 안테나에 더 가까이 이동시키기 위해 SoC 통합으로 이 방식을 한 단계 더 발전시켰다. 동일한 디바이스를 이용해 다양한 Tx/Rx 안테나 구성 및 진화된 표준을 처리할 수 있어 모바일 장비 공급업체는 시장 역학 및 기회에 신속하게 대응할 수 있다. 5G의 경우 단일 유형의 아키텍처는 차세대 라디오 액세스 네트워크의 다양한 요구를 해결하지 못한다.

유연성을 위한 완전한 데이터 컨버터 서브시스템

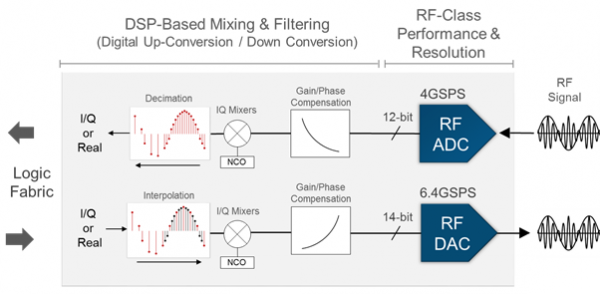

RF 데이터 컨버터 서브시스템에는 각 채널마다 믹서, 오실레이터(NCO), 데시메이션/인터폴레이션, 기타 디지털 신호 처리 기법이 포함되어 있으며, IQ 프로세싱을 위한 복잡한 신호를 지원한다. 이 컨버터는 5G에 필요한 높은 샘플 속도와 큰 다이내믹 레인지, 해상도를 구현할 수 있다. 경우에 따라 데이터가 로직 패브릭에 직접 전달되기 전에는 어떤 FPGA 리소스도 DDC(digital down-conversion)에 필요하지 않다.

그림 7: RFSoC의 통합 RF 서브시스템

단품 RF 부품 비교 및 16나노 FinFET의 장점

Direct RF 샘플링은 점진적으로 채택되었다. 사실 IF 샘플링은 면적 및 전력 효율이 높기 때문에, 여전히 기존 IF 방식이 일반적이다. 이 솔루션은 예전 실리콘 프로세스(예: 65나노)에서도 비용 효율적이다. RF 설계 커뮤니티가 기존 아날로그 사용 모델에 익숙하다는 점을 감안하면, 가장 적합한 방식일 것이다. 단품 기반 Direct RF 데이터 컨버터는 여전히 ‘하이엔드’로 여겨지고 있으며, 일반적으로 보다 진화된 프로세스 노드에 기반한다. 디지털 프로세싱 능력이 풍부한 단품 디바이스로서 Direct RF에서 유연성이 더 커졌지만, 높은 샘플 속도를 요구한다는 점으로 인해 아날로그 방식 구현보다 전력에서 불리할 수 있다.

아래에서 알 수 있듯이, Direct RF 샘플링의 독자적인 유연성은 사실이지만, 단품 부품으로서 상승 곡선은 궁극적으로 ‘증분적(incremental)’이라 여전히 균형이 필요하다. 한편 무선 제조사는 5G로 가기 위해 점진적인 개선보다 그 이상의 것을 필요로 한다. 유연성과 더불어 전력 및 풋프린트 감소에서 가장 의미 있는 도약은 완전한 시스템 통합이다. RF 프론트엔드 및 라디오 프론트엔드를 같은 디지털 도메인에 통합시켜 시스템과 아날로그 설계가 한층 더 유연해졌다. 결과적으로 통합을 통해 RF 샘플링은 더욱 채택 가능성 높은 기술이 되었고, 산업은 완전한 소프트웨어 정의 라디오(software defined radio)에 한 발 더 다가가게 되었다.

놀라운 아날로그 특성을 보여준 TSMC의 16나노 FinFET 공정 기반의 RFSoC에서 컨버터 서브시스템의 전력 대비 성능은 놀랍다. RF 서브시스템과 전체 신호 체인을 첨단 CMOS에 구축해 RFSoC는 아날로그에 무어의 법칙을 적용시켰다.

그림 8: 5G 무선에서 데이터 컨버터 솔루션의 비교

RF 아날로그 통합에 관한 자일링스의 경험

RFSoC의 전신인 고성능 ADC/DAC는 2012년 7 시리즈 FPGA에 통합되었다. 확인과 특징 정의, 고객 검증을 통해, 이 테스트 칩은 유연성과 JESD204 인터페이싱 제거를 통한 생산성 이득, 채널 수의 확장성 등을 보여주었다. 이 개념 입증에서는 올 프로그래머블 RFSoC를 개발하기 위한 애플리케이션 중심적 방식도 유도했다.

요약: 5G 무선을 위한 혁신적인 기술

자일링스는 RF급 아날로그 기술을 도입하여 시스템 통합을 계속 이어가고 있다. 실리콘 및 시스템 레벨에서 모바일 제조사는 지나치게 대형 5G 테스트 베드와 프로토타입을 보다 소형의 상용화 시스템으로 전환하기 위한 획기적인 기술을 필요로 한다. 즉, RFSoC가 딱 맞는 시기에 출시되어 5G 개발의 긴급한 문제를 해결하는 것이다.

알베오 U55C의 출시로 HPC 업계에 많은 가치 제공할 것

조회수 811회 / Nathan Chang

엣지 센서에서 CPU 가속기까지 ‘버설 AI 엣지 시리즈’

조회수 1016회 / Rehan Tahir

적응형 컴퓨팅, 포스트-무어의 법칙 시대에서 성장을 주도하다

조회수 1362회 / Victor Peng

데이터센터 혁신을 위한 장벽 없는 FPGA 솔루션

조회수 1003회 / Kartik Srinivasan 외 2인

자동차 시장의 혁신을 선도하는 자일링스의 DNA

조회수 739회 / Yousef Khalilollahi

CXL, CCIX 기반 PCIe 5와 SmartNIC은 어떻게 가속 솔루션을 혁신하고 있...

조회수 6791회 / Scott Schweitzer

대규모 5G 무선 구축을 위한 혁신적인 징크 RFSoC DFE

조회수 1491회 / Gilles Garcia

SmartNIC 아키텍처: 가속기로의 이행, 그리고 FPGA가 우위를 점하는 이유

조회수 4465회 / Scott Schweitzer

SmartNIC이 일반 NIC보다 뛰어난 이유는?

조회수 1863회 / Scott Schweitzer

PDF 다운로드

회원 정보 수정