SPICE를 사용한 SAR ADC 드라이버 증폭기 및 RC 필터 회로 안정화 최적화

글/루이스 치오에(Luis Chioye), 텍사스 인스트루먼트

SAR(연속 근사 레지스터) ADC로 최대의 성능을 이끌어내기 위해서는 드라이버 증폭기와 저항-커패시터(RC) 필터 프론트 엔드 회로를 최적화 할 필요가 있다. 이 글에서는 SPICE 시뮬레이션을 사용해서 SAR 드라이버 증폭기 및 RC 필터 안정화 성능을 최적화하는 것을 보여준다.

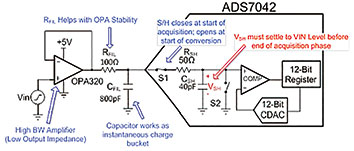

그림 1은 전형적인 SAR ADC 드라이버 회로와 ADC의 내부적인 샘플-앤-홀드 구조를 보여준다. SAR ADC는 포착 단계와 변환 단계, 두 단계에 걸쳐서 변환을 한다. 포착 단계일 때는 샘플-앤-홀드 스위치 S1이 닫히고 외부 구동 회로가 ADC의 샘플-앤-홀드 커패시터 CSH를 아날로그 입력 전압으로 충전한다.

포착 단계가 완료되면 S1이 열리고 ADC가 이진 탐색(binary search) 알고리듬을 사용하여 디지털 코드 변환을 실시한다. 드라이버 회로는 포착 시간(tacq) 동안에 CSH를 완전히 충전하고 ADC의 최하위 비트(LSB) 분해능의 절반 이내에 안정되어야 한다.

[그림 1] SAR ADC 드라이버 회로와 ADC의 샘플-앤-홀드 구조

SAR ADC 아날로그 입력은 고(high) 임피던스 포트라기 보다는 샘플-앤-홀드 회로가 스위칭하는 것에 따라서 동적 부하로 나타난다. 다시 말해서 SAR 입력의 전류 요구량은 샘플링 속도에 비례해서 증가한다. SAR의 포착 시간(피리어드)은 디바이스마다 다를 수 있으며, 많은 경우에 샘플링 속도에 반비례한다. 높은 속도인 경우에는 포착 시간이 수십 나노초 대로 짧을 수도 있다.

드라이버 회로를 보면, CFIL이 전하 버킷(charge bucket)으로서 동작해서 드라이버 증폭기가 CSH로 순간 전하를 회복할 수 있도록 돕는다. 샘플-앤-홀드가 스위칭할 때 전하 킥백 현상과 전압 저하를 최소화하려면 CFIL을 CSH보다 몇 배 더 큰 값으로 정해야 한다. CFIL은 공식 1에 따라서 선택할 수 있다:

![]()

RFIL은 절연 저항으로서, 구동 증폭기를 안정화 시킨다. RFIL 값이 높으면 증폭기를 안정화 시키는 점에서 유용하다. 하지만 과도하게 큰 저항을 사용하면 안정화 문제를 일으키거나, 왜곡을 일으키거나, 부정확한 변환 결과값을 초래할 수 있다. ADC의 포착 시간(tacq)과 LSB 분해능이 주어졌을 때 공식 2를 사용해서 RFIL의 범위를 구할 수 있다:

![]()

Vstep은 샘플-앤-홀드가 닫힐 때 CFIL로의 전압 저하로서, CFIL/CSH 비율과 샘플링된 전압에 따라서 15mV부터 100mV까지 될 수 있다.

증폭기가 커패시티브 부하를 구동하면서 안정적이어야 하며, 포착 간격 시에 CSH를 충전하고 안정화하기 위해서 충분한 대역폭이고 폐쇄 루프 출력 임피던스가 낮아야 한다. 공식 3을 사용해서는 최소한의 기준을 충족하는 증폭기 단위-이득 대역폭(UGBW)을 구할 수 있다.

![]()

공식 1부터 공식 3까지는 소자 값을 선택하기 위한 시작점이다. 이 값들을 토대로 해서 회로 시뮬레이터를 사용해서 증폭기와 RC 필터 회로를 최적화할 수 있다.

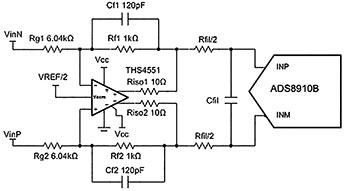

그림 2의 완전 차동 증폭기(FDA) 감쇠기와 SAR ADC 포착 시스템을 살펴보자.

[그림 2] FDA 감쇠기와 완전 차동 SAR ADC

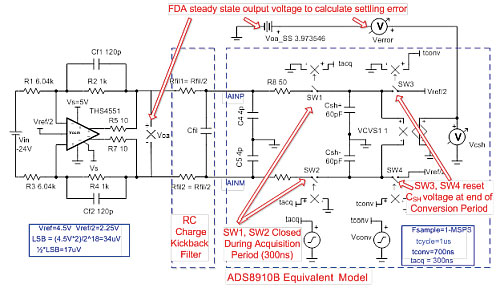

해당 디바이스의 데이터 시트에서 표기하고 있는 등가 입력 회로 모델로부터의 샘플-앤-홀드 파라미터와 원하는 포착 및 변환 타이밍 사양을 사용해서 ADC SPICE 모델을 구축한다. 그림 3은 ADS8910B의 TINA-TI SPICE 모델을 보여준다.

[그림 3] ADS8910B 샘플-앤-홀드 회로의 TINA-TI SPICE 모델

그림 3에서는, 샘플-앤-홀드 스위치 SW1-2가 300ns 포착 시간에는 닫히고 700ns 변환 시간에는 열린다. 매 변환을 할 때마다 CSH로 약간의 전하 손실이 발생된다. 모든 ADC가 CSH 상의 전압을 리셋하는 것은 아니지만, 매 사이클이 끝날 때마다 CSH 전압을 리셋하는 것으로 모델링하면 전하 손실을 좀더 보수적으로 모델링할 수 있다. 변환이 끝날 때마다 스위치 SW3-4가 CSH 전압을 중간 지점(Vref/2)으로 리셋한다. Verror 전압 프로브는 포착이 완료될 때마다 샘플-앤-홀드로의 안정화 오차를 계산한다.

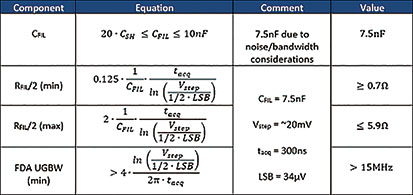

표 1은 RC 필터 값 범위와 최소 FDA 대역폭을 계산한 것을 보여준다.

[표 1] RC 필터 값과 FDA 최소 대역폭 계산

ADS8910B 데이터 시트에서는 필터 커패시터를 1.2nF < CFIL < 10nF의 범위로 권장하고 있다. 그러므로 잡음과 대역폭 요구를 감안해서 CFIL = 7.5nF 커패시터로 선택한다. THS4551의 FDA(150MHz)는 최소 주파수 요구를 초과한다.

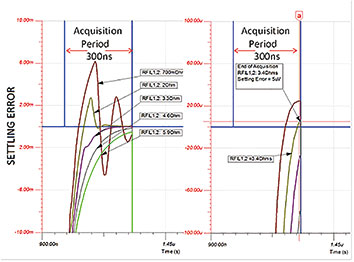

그 다음에는 반복적으로 SPICE를 사용해서 RC 값을 최적화한다. 그림 4는 CFIL = 7.5nF로 RFIL/2 저항에 대해서 스텝 파라미터 스윕을 실시해서 얻어진 TINA-TI 과도현상 결과를 보여준다.

[그림 4] RFIL 스텝 파라미터 스윕을 사용한 TINA-TI 과도현상 시뮬레이션

그림 4는 CSH 안정화 오차 전압 시뮬레이션을 보여준다. RFIL < 3.3?을 사용한 첫 번째 시뮬레이션에서는 과도한 링잉이 발생되지만, RFIL/2 = 3.4?을 사용한 두 번째 시뮬레이션은 5?V 이내의 안정화 오차로서(< 1/2 LSB) 안정된 결과를 보여준다. 그러므로 RFIL/2 = 3.4?과 CFIL = 7.5nF으로 선택하는 것이 이 설계를 위한 최적의 RC 필터이다.

TI Precision Labs ? SAR ADC 입력 드라이버 설계 비디오 시리즈에서는 SAR ADC SPICE 모델을 작성하고 TINA-TI 소프트웨어를 사용해서 RC 필터 값을 최적화하는 것에 대해서 단계적으로 설명하고 있다. 또 아나로그 설계자 회로 Cookbook의 ? SAR ADC 용의 고 입력 임피던스, 완전 차동, 아날로그 프론트 엔드(AFE) 감쇠기 회로에서는 이 회로에 관한 분석과 시뮬레이션 파일들을 볼 수 있다.

이 글에서는 SAR ADC의 드라이버 과도현상 안정화 시뮬레이션에 대해서 설명했다. SPICE를 사용하는 SAR 포착 시스템에서 드라이버 회로의 안정화 성능을 최적화하고 검증할 수 있다.

전기차 시스템 혁신을 이끄는 GaN 기술

조회수 289회 /

자동차 인포테인먼트 클러스터 시스템 구동

조회수 199회 / Timothy Hegarty

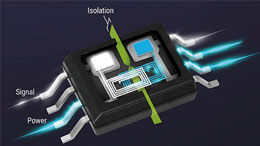

절연 기술 개발과 고전압 설계 문제의 해결

조회수 431회 / Krunal Maniar

AEC-Q100 MSPM0 MCU를 사용하여 오토모티브 차체 전자 장치 설계 최적화

조회수 287회 / Henok Taffere

정밀 ADC로 전기차 충전기 계측

조회수 437회 / Jiyah Starks

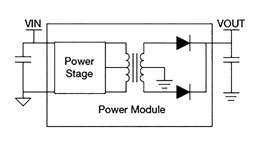

절연형 DC/DC 바이어스 전원 솔루션

조회수 574회 / Taxas Instruments

옵토커플러를 업그레이드하자

조회수 592회 / 김태호

급성장하는 HEV/EV 시장에서 오토모티브 HVAC 설계를 최적화하는 방법

조회수 903회 / Osamah Ahmad 외 1인

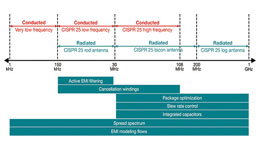

전원 공급 장치의 EMI 절감을 위한 시간 및 비용 효율적 혁신

조회수 1160회 / Yogesh Ramadass 외 2인

PDF 다운로드

회원 정보 수정