dv/dt로 인한 4-스위치 비반전 벅-부스트 컨버터 오동작 문제 고찰

자료제공/온세미컨덕터

게이트 제어 설계에 대한 검토

USB는 적은 양의 전력만이 공급 가능한 데이터 인터페이스에서 시작하여 현재는 데이터 인터페이스에 주요 전력 공급원이 되는 단계까지 발전했다. 최신 USB 3.x 프로토콜은 훨씬 높은 단계의 전류를 지원한다. USB-C 포트는 디폴트 값으로 5V 전압을 사용하며 플러그인 방식의 기기와 함께 포트전압을 20V까지 상승시킬 수 있다.

새로운 전력공급의 요구조건에서 특이사항은 4.5V~32V 배터리 전압을 사용해서 어떻게 직류 신호버스라인에 5V ~20V를 공급할 수 있냐는 것이다. 4-스위치 벅-부스트 컨버터는 벅이나 부스트 전압변환을 제공해주는 적절한 토폴로지이다. 넓은 변압범위, 양극성, 고효율성 그리고 설계자들과 고객사들이 요구하는 소규모의 폼팩터 방법을 가능하게 하기 때문이다.

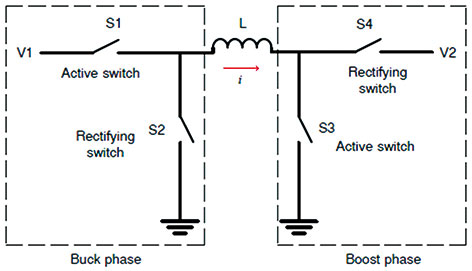

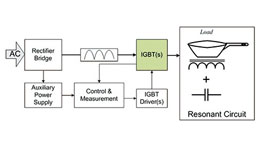

비반전 벅-부스트 컨버터의 전력단계는 네 가지의 스위치들과 인덕터로 구성되어 있다. Figure 1에서 볼 수 있듯이 4개의 스위치는 벅 단계(S1 & S2)와 부스트 단계(S3 & S4)로 통합되어 분리된다. 각 단계 별로 하나의 액티브 스위치와 하나의 정류 스위치(rectifying switch)가 있다. 온세미컨덕터의 NCP81239컨트롤러와 같은 컨트롤러를 사용한다면 이 토폴로지는 동기형 벅 방식 혹은 동기형 부스트 방식에서 가동할 수 있게 된다.

[그림 1] 비반전 벅-부스트 컨버터 도해

dv/dt로 유발된 오동작

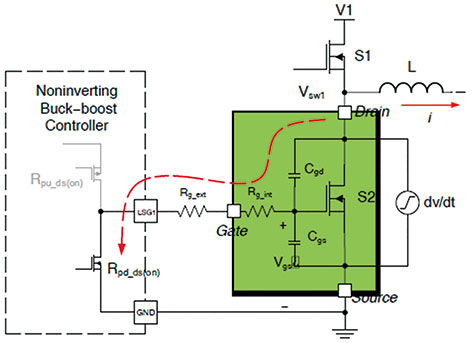

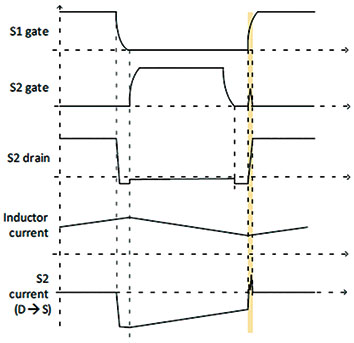

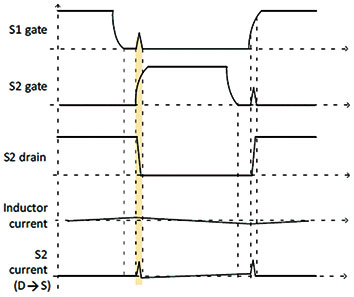

동기형 벅 방식 컨버터에는 ‘로우사이드(low-side) 오동작’ 혹은 ‘dv/dt가 유발한 오동작’으로 불리는 잘 알려진 현상이 있다. 이는 스위치 자체에 데미지를 줄 가능성이 있고, 컨버터 전체의 신뢰도까지도 위험해질 수 있다. 이 현상은 하이사이드(high-side) (액티브) 스위치가 켜지고 로우사이드 (정류) 스위치의 드레인-투-소스(drain-to-source) 전압이 급격히 증가할 때 일어난다. 이러한 급격한 전압의 증가는 게이트와 드레인 간 기생 용량(parasitic capacitance) (밀러 용량, Cgd) 전압을 변환하며, C x dv/dt 변위전류를 생성한다. 만약 변위전류 때문에 Vgs(th)을 초과하는 전압이 게이트와 전력원 사이에 생성되면 바로 이것이 정류 스위치의 오동작을 야기한다. 이것과 동일한 회로가 그림 2에 나와 있으며, 파동의 형태는 그림 3에 나와있다.

[그림 2] 비반전 벅-부스트 컨버터 벅 단계의 오동작과 동일한 회로

[그림 3] 정상적으로 가동 중일 때 dv/dt가 유발하는 오동작 파형의 형태

dv/dt가 유발하는 비반전 벅-부스트 컨버터의 오동작 문제점에 관련하여 현재까지 발간된 정보는 적다. 따라서 이 주제에 대해 이해하기 쉽게 설명한다면 관련 업계에 유용할 것으로 보인다. 설계자들이 벅 컨버터의 회로요소를 단순히 비반전 벅-부스트 컨버터의 단계들로 복제하기만 한다면 오류가 생길 수 있다. 이러한 토폴로지가 더 많은 곳에 적용되기 시작하면서 dv/dt가 유발하는 오동작 문제점은 반드시 이해해야만 하는 주제가 되고 있다.

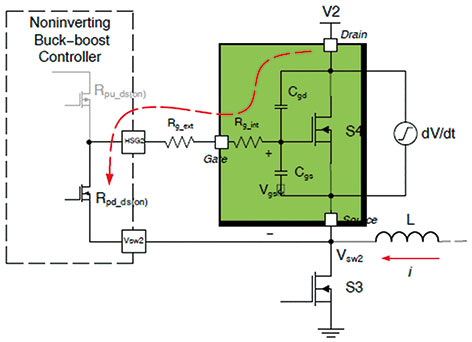

그림 4는 비반전 벅-부스트 컨버터 부스트 단계의 높은 쪽 MOSFET을 그림으로 나타낸 것인데, 이 시점은 드레인에서 전력원까지의 회로의 중계선에서 양극의 dv/dt 변환이 나타나는 시점이다. 낮은 쪽 MOSFET이 켜지면 높은 쪽 MOSFET의 드레인에서 전력원까지의 전압은 급격히 증가한다. 이러한 MOSFET이 꺼진 상태에서는 드레인 전압의 급격한 상승이 드레인과 게이트 사이의 밀러 용량 Cgd의 전압을 변환하고, C*dv/dt 변위전류를 발생시킨다. 만약 이러한 변위전류 때문에 Vgs(th)를 초과하는 전압이 게이트와 전력원 사이에 생기면, MOSFET의 잘못된 오동작 신호를 유발하게 된다. 결과적으로 MOSFET은 일부분만 켜져 있으면서 공급전압과 GND(접지)사이의 낮은 저항성의 경로를 생성할 수 있게 되는 것이다. 최악의 상황에서는 기기 내에 높은 전력의 소산이 생기게 되어 결국에는 기기 전체를 파손하는 고장이 발생된다.

[그림 4] 비반전 벅-부스트 컨버터 부스트 단계의 오동작과 동일한 회로

공식 1번은 이 방식의 게이트와 전력원 간의 전압을 나타낸다. 여기서는 ‘Dt/Cgs >> Rpd_ds(on) + Rg_est + Rg_int’로서, Cgd를 타고 흐르는 변위전류의 대부분이 게이트에서 나와서 게이트 드라이버 레지스터로 들어갈 것이라는 이론적인 가정을 하였다.

![]() (1)

(1)

만약 Vgs’의 Vgs(th)보다 작으면, MOSFET이 켜지지 않을 것이다. 따라서 설계를 할 때 어떠한 조건에서도 dv/dt 가 유발하는 전압을 Vgs의 최고치로 제한하도록 설계상의 목표를 두어야 한다. 공식 2번은 그 방법을 나타낸다:

![]() (2)

(2)

공식 2번을 충족시키기 위해 우리가 조정할 수 있는 여러 변수들이 있다는 것을 주목해서 봐야 한다. Rpd_ds(on)은 컨트롤러에서 나오는 것이다. Rg_int과 Cgd는 MOSFET로부터 나온다. 이들은 부품이 정해지면 조정이 되지 않는다. 따라서 컨버터의 dv/dt 면역성을 향상시키기 위해 극히 낮은 임피던스를 적용한 게이트 드라이브 회로를 사용해야 하고, 더 높은 Vgs(th)이 보다 바람직하다. 드라이브 회로에 낮은 임피던스가 적용되면 원가가 상승하고, Vgs(th)를 높이는 것은 Rds(on)의 동반 상승 효과를 가져온다. Vgs(th)가 부온도계수를 가지므로 온도가 상승하면 오동작의 확률이 증가한다. 일반적으로 게이트 전압은 Vgs(th)를 초과하지 않고, 높은 기기 저항성은 기기내의 전류를 제한한다. 오동작으로 인하여 기기의 파손으로 이어지는 경우는 아주 드물다.

특수 사례: 경부하와 낮은 리플 전류 조건

상기의 분석은 정류 스위치가 켜지기 전에 인덕터 전류가 기생전력 커패시터를 방전시킬 정도로 많아서 액티브 스위치의 시동은 하드 스위칭이고 정류 스위치의 시동은 소프트 스위칭이라는 전제를 토대로 한 것이다. 커패시터를 완전히 방전시키기 위한 최소 인덕터 전류는 아래와 같다:

![]() (3)

(3)

위에서 Is_min은 액티브 스위치가 꺼졌을 때의 인덕터 전류이다. Coss1/2는 액티브 스위치의 출력 정전용량이며, tdead는 액티브 스위치의 동작이 끝나고 정류 스위치의 시동까지의 정지시간을 나타낸다.

특수한 사례는 공식 3번이 충족되지 않을 때 발생한다. 이는 입력압력과 출력압력이 서로 비슷하고 부하가 거의 0에 가까울 때를 의미한다. 이 상황에서는 인덕터 전류가 너무 적어서 스위치들의 출력 커패시터를 완전히 방전시킬 수 없다. 벅 단계를 예로 들면 이 상황에서 동기형 정류 스위치가 켜지면 낮은 쪽 (정류) 스위치의 드레인에서 전력원 간 전압은 계속 높게 유지된다. 따라서 이 전압은 정류 스위치가 켜지는 순간 급격히 0으로 떨어지게 된다. 그 결과, 상호 보완적이도록 액티브 스위치의 D-S 전압은 V1까지 급격히 증가한다. 드레인과 게이트 간 기생 용량 (밀러 용량, Cgd)에 적용되는 이러한 급격한 전압 상승 (높은 dv/dt)은 i= Cgd x dv/dt의 변위전류를 생성한다. 만약 Vgs(th)을 초과하는 변위전류가 게이트 전압을 발생시키면, 액티브 스위치의 오동작이 촉발될 수 있다.

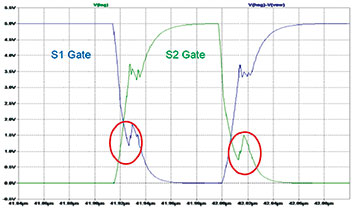

마찬가지로, 액티브 스위치가 켜질 때에도 dv/dt가 유발하는 오동작 문제점은 계속 생길 수 있다. 다시 말해서 액티브 스위치가 켜지면 정류 스위치의 게이트에 오동작 범프(파형편차)를 보게 된다는 것이다. 이러한 파동은 그림 5에 그려져 있다. 이 분석은 그림 6의 시뮬레이션 결과로서 뒷받침된다.

특수한 사례의 부스트 단계 분석도 위와 유사하다. 하지만 본 연구에서는 설명하지 않기로 한다.

[그림 5] 경부하와 낮은 리플 전류 조건하의 dv/dt가 유발하는 오동작 파형의 형태

[그림 6] 경부하와 낮은 리플 전류 조건하의 시뮬레이션 결과

Dv/dt 슬루레이트(slew rate) 감소

공식 2번은 본 문제를 해결하기 위한 가이드라인을 주었다. 이 문제는 dv/dt로 인해 유발되는 것이므로 첫번째 직관적인 해결방법은 dv/dt를 감소시키는 것이다. Dv/dt 통제는 게이트 드라이버 회로를 조정하여 쉽게 수행할 수 있다. 액티브 스위치의 풀업(pull up) 저항성과 외부 게이트의 저항성은 정류 스위치의 저항성 보다 커야 한다. 이는 액티브 스위치가 동작되는 현상을 줄일 수 있고 효과적으로 공식 2번의 dv/dt 요인들을 감소시킬 수 있다.

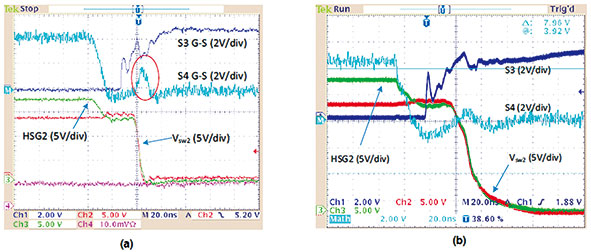

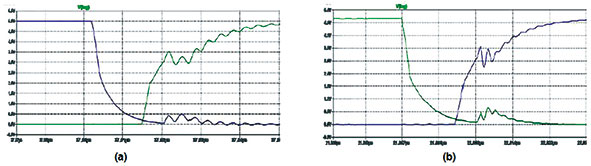

그림 7 (a)는 오동작 전압이 스위칭 노드에서 1.9V일 때 dv/dt는 1.5 V/ns와 같다는 사실을 보여준다. 그림 7 (b)는 오동작 최고 전압을 1.0V로, dv/dt는 0.75 V/ns로 하향 조정한 내용을 보여준다. 본 오동작 문제점 크기의 규모는 dv/dt에 영향을 주는 외부 게이트 저항기를 조정하여 완화할 수 있다는 것이 입증되었다.

두번째 해결책으로는 스위칭 노드 Vsw1과 Vsw2에 RC 스너버(snubber) 회로를 추가하는 것이다. 이것은 dv/dt 값을 감소시키는 가장 직접적인 방법이 되겠다. 이 방법의 부작용은 손실이 증가한다는 것이다.

[그림 7] 게이트 신호와 다양한 외부 게이트 저항기의 스위칭 노드 dv/dt 값

마지막 해결책이지만 앞의 해결책만큼 중요도가 있는 방법으로는 비록 공식 2번에서 나타나지 않지만 정류 스위치가 동작을 멈춘 시점부터 액티브 스위치가 동작을 시작한 시점까지의 tdead시간 또한 잘 관리하는 것이다. tdead시간이 오동작의 크기에 직접 영향을 주지는 않지만 액티브 스위치가 동작을 시작하기 전에 정류 스위치 게이트 전압이 0으로 떨어지는 것을 보장해준다. 만약 tdead시간을 넉넉하게 설정하였다 하더라도 액티브 스위치가 켜지면 dv/dt가 유발하는 시동은 그대로 존재한다는 것을 염두에 두어야 한다.

MOSFET 선택

알맞은 MOSFET을 선택하는 것 또한 dv/dt가 유발하는 오동작 문제의 영향을 줄이는 데 도움이 될 수 있다. 한가지 방법으로는 높은 게이트 Vgs(th)의 MOSFET를 선택하는 것인데 이는 Rds(on)를 상승시킬 수 있다.

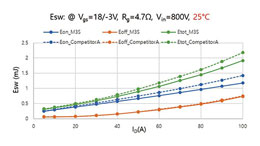

Dv/dt가 유발하는 시동을 막기 위해서는 정류 스위치를 선택하는 기준은 Qgd/Qgs(th)비율에 기반하여야 한다. Qgs(th)는 게이트 전압이 Vgs(th)수치에 도달하기 전에 게이트에서 전력원까지의 전력량이다. 공식 2번에 따르면, Cgd를 낮추는 것은 dv/dt가 유발한 전압의 규모를 줄일 수 있다. 게다가 이것은 dt/Cgs, Vds와 Vgs(th) 수치에도 의존한다. Dv/dt가 유발한 오동작 문제점을 해석하는 하나의 방법은 Vds가 입력 전압에 도달하면 밀러 전력량은 Vth 수준의 Cgs의 총 전력량보다 작아야 하며, 따라서 정류 스위치가 켜지지 못하게 막는 것이다. 그러면 우리는 다음과 같은 관계식을 찾을 수 있다:

![]() (4)

(4)

![]() (5)

(5)

우리는 게이트 전력량만을 사용하여 dv/dt가 유발하는 시동에 대한 정류기기의 저항성을 평가할 수 있다. 원칙적으로는 충분한 여유를 두기 위해 Qgd의 전력량은 Qgs(th)수치보다 커서는 안된다.

대체 가능한 드라이버 회로 설계안

공식 2번에 따르면 dv/dt가 유발하는 오동작 전압의 규모를 낮게 만들기 위해 게이트 드라이브 저항성인 Rg_ext수치는 항상 낮게 유지되어야 한다. 따라서 정류 스위치가 동작을 빠르게 시작하고 종료하게 되며, 이것은 소프트 스위칭인 경우에 문제가 되지 않는다. 하지만 상기의 특수한 사례에서 설명했듯이 소프트 스위칭이 실현되지 않으면 오동작 범프를 야기할 것이다.

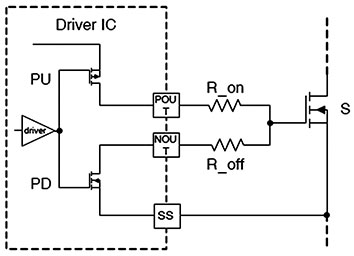

어떤 컨트롤러는 그림 8에서 나타나듯이 오픈 드레인이나 오픈 전력원의 구성을 제공하기도 한다. 이것은 고객사들이 독립적으로 동작을 시작하는 속력과 동작을 끝내는 속력을 통제할 수 있도록 해준다.

[그림 8] 동작을 시작할 때와 끝낼 때의 다른 게이트 저항

외부 게이트 저항성에 더하여, 컨트롤러 내부의 게이트 드라이브 회로도 검토되어야 한다. Rg_ext의 고려사항과 마찬가지로, 정류 스위치 내부 풀 다운(pull down)저항도 작은 수치여야 한다.

현재 네거티브 턴 오프(negative turn off) 전압과 같은 별도의 부품이 필요한 다른 복잡한 회로 기술들이 여럿 존재한다. 본 연구에서는 다루지 않을 것이다.

특수 사례를 위한 게이트 드라이브 설계 고려사항

이전의 단락에서 설명한 것처럼 경부하와 낮은 리플 전류 게이트 드라이브 회로 조건은 작은 HS 게이트 레지스터와 큰 LS 게이트 레지스터를 필요로 한다. 이는 정상적인 가동 하에서 필요조건과 정반대이다. 따라서 정상적인 경우와 특수한 사례의 가동 간의 균형을 잘 고려해야 한다. HS 게이트 레지스터는 부스트트랩 커패시터가 장착된 레지스터로 교체될 수 있다. LS 게이트 레지스터는 0으로 유지되어야 한다. 게다가 액티브 스위치의 MOSFET을 선택할 경우 상기의 ‘MOSFET 선택’ 단락에서 언급한 지시사항을 준수하여야 할 것이다.

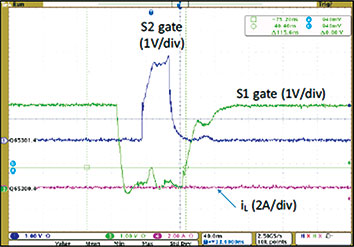

그림 9 (a)는 HS의 가동 종료에서 LS 가동 시작을 시뮬레이션한 파동의 형태를 그림으로 나타낸 것이다. 그림 9 (b)는 LS의 가동 종료에서 HS 가동 시작을 시뮬레이션한 파동의 형태를 그림으로 나타낸 것이다. Dv/dt가 유발한 오동작 범프 중 어느 것도 MOSFET의 가동 시작의 Vgs(th)를 초과하지 않는다.

[그림 9] 경부하와 낮은 리플 전류 조건하에서 시뮬레이션한 향상된 스위칭 파동의 형태

[그림 10] 경부하와 낮은 리플 전류 조건하에서 실험한 향상된 스위칭 파동의 형태

결론

비반전 벅-부스트 컨버터에서 Dv/dt가 유발한 오동작문제는 벅 단계와 부스트 단계 모두에서 동기형 정류 MOSFET에서의 드레인에서 전력원까지의 전압이 급격히 증가하여 발생한다. 설상가상으로 부하 전류와 리플 전류가 낮으면 액티브 스위치와 정류 동기형 스위치에서 모두 이 문제가 발생할 수 있다. 결국, 원하지 않는 전류가 돌진하여 양쪽의 단계의 레그를 타고 흐르게 되기 때문에 전체 시스템 효율성이 악화된다. 전력 공급 설계자들에게 필요한 경제적인 회로 해결안들이 여러 가지 가능한데, 예를 들면 정류 스위치의 가동종료 게이트 드라이브의 저항을 최소화하는 방법, 액티브 스위치의 가동시작 게이트 드라이브의 저항을 상승시키는 방법, 혹은 스위칭 노드에 RC 스너버 회로를 추가하는 방법이 있다. 또한, 작은 Qgd/Qgs(th)비율과 높은 Vgs(th)의 MOSFET을 선택한다면 dv/dt가 유발하는 오동작의 확률을 감소시킬 수 있다.

고속 스위칭 애플리케이션에 온세미 기술을 선택해야 하는 이유

조회수 257회 / Fatih Cetindag

실리콘 카바이드(SiC)를 바로 아는 것이 핵심

조회수 479회 / Ajay Hari

IGBT 이해하기: 언제, 어디서, 어떻게 사용될까

조회수 1784회 / Jinchang Zhou

태양 충전 에너지를 이용한 전기 자동차(EV) 고속 충전

조회수 709회 / Jon Harper

인도어 포지셔닝과 실시간 위치 추적 시스템의 백본으로 PoE 사용하기

조회수 901회 / Parthiv Pandya

넷 제로(net-zero)를 위한 21세기 전력 기술

조회수 1017회 / Asif Jakwani

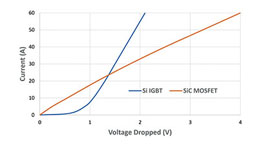

태양광 인버터에서의 IGBT 및 SiC MOSFET 성능 비교

조회수 5184회 / Steven Shackell

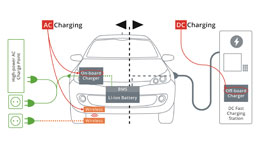

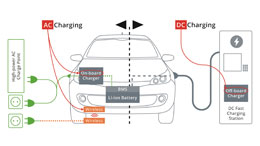

전기차를 위한 DC 충전 기술

조회수 3331회 / onsemi

전기차를 위한 DC 충전 기술

조회수 4256회 / 온세미

PDF 다운로드

회원 정보 수정