MOSFET 게이트 앞에 100Ω 저항을 사용하는 것이 꼭 필요할까?

글/Aaron Schultz, LPS 사업부 애플리케이션 엔지니어링 책임자, ADI

머리말

오늘 수업의 선생님이 되어줄 구룩스(Gureux) 같은 경험 많은 전기 엔지니어들에게, MOSFET 게이트 앞에 무엇을 사용해야 하느냐고 물으면 누구든 ‘약 100Ω 저항’이라고 말할 것이다. 그럼에도 불구하고 누군가는 왜 그래야 하는지 궁금증이 일어날 수 있다. 오늘은 바로 이 궁금증을 해소할 수 있도록 그에 관련된 질문들을 하나하나 풀어보려고 한다. 뉴빈(Neubean)은 신참 애플리케이션 엔지니어로서, 안정성을 위해서 MOSFET 게이트 앞에 100Ω 저항을 사용하는 것이 정말 꼭 필요한 것인지 파헤쳐보려고 한다. 구룩스는 30년 경력의 애플리케이션 엔지니어로서, 뉴빈이 시험하는 것을 지켜보고 경력자로서 조언을 한다.

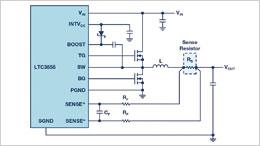

상측 전류 검출

그림 1의 회로는 전형적인 상측 전류 검출 회로를 보여준다. 부궤환을 통해 VSENSE 전압이 이득 저항 RGAIN에 걸리도록 한다. RGAIN을 통과한 전류는 P-채널 MOSFET(PMOS)를 거쳐서 저항 ROUT으로 도달한다. 이 저항 상에서 접지 참조 출력 전압이 구축된다. 전체적인 이득은 다음과 같다:

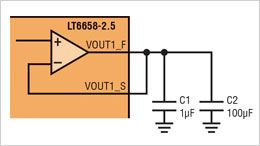

저항 ROUT 곁의 선택적인 커패시턴스 COUT은 출력 전압을 필터링하는 역할을 한다. PMOS의 드레인 전류가 검출 전류를 빠르게 추종한다고 하더라도 출력 전압은 단일 극점 지수 궤적을 나타낸다.

이 회로에서 저항 RGATE는 증폭기를 PMOS 게이트로부터 차단한다. 이 저항 값은 얼마일까? 경험 많은 동료인 구룩스는 말할 것이다. “당연히 100Ω이지.”

다양한 저항 값 시험

뉴빈은 구룩스의 학생이 되어서 이 게이트 저항에 대해서 곰곰히 생각한다. 게이트에서 소스로 충분히 높은 커패시턴스나 또는 충분히 높은 게이트 저항을 사용하면 안정성 문제가 발생될 것이라고 그는 생각한다. RGATE와 CGATE가 해로운 쪽으로 상호작용하는 것이 확실해지기만 한다면, 100Ω이든 혹은 어떤 게이트 저항이든 자동으로 적절하다고 하는 믿음을 깰 수 있을 것이다.

그림 2는 회로 동작을 살펴보기 위해서 사용된 LTspice 시뮬레이션이다. 뉴빈은 RGATE를 높이면 안정성 문제가 발생될 것이라고 생각하고 이것을 보여주기 위한 시뮬레이션을 실시한다. 어쨌든 RGATE에서 CGATE로의 극점이 개방 루프와 관련해서 위상 마진을 깎아먹을 것이다. 그런데 의아하게도 어떤 값의 RGATE도 시간 도메인 응답으로 어떤 문제도 나타내지 않는다.

그렇게 단순한 회로가 아니다.

주파수 응답을 살펴본 뉴빈은 개방 루프 응답을 구분하는 것이 필요하다는 것을 깨닫는다. 루프를 형성하는 포워드 경로가 단위 부궤환과 결합하면 차이에서 시작해서 결과적인 음 입력 단자에서 끝난다. 그런 다음 뉴빈은 VS/(VP-VS) 다시 말해서 VS/VE를 시뮬레이트하고 플롯을 그린다. 그림 3은 이 개방 루프 응답의 주파수 도메인 플롯을 보여준다. 그림 3의 보드 플롯에서는 교차점에서 dc 이득이 매우 작고 위상 마진 문제가 보이지 않는다는 것을 알 수 있다. 그렇지만 이 플롯은 교차점 주파수가 0.001Hz 미만이라서 전반적으로 아주 이상하게 보인다.

그림 4는 이 회로를 제어 시스템으로 나타낸 것을 보여준다. LTC2063은 여타의 전압 피드백 연산 증폭기처럼 높은 dc 이득과 단일 극점으로 시작된다. 연산증폭기가 오차 신호를 획득하고 RGATE - CGATE 필터를 거쳐서 PMOS 게이트를 구동한다. CGATE와 PMOS 소스가 함께 연산 증폭기의 -IN 입력으로 연결된다. RGAIN이 이 노드에서 저(low) 임피던스 소스로 연결한다. 그림 4만으로도 RGATE가 RGAIN보다 훨씬 더 크다면 RGATE - CGATE 필터가 안정성 문제를 일으킬 것으로 보일 수 있다. 어쨌든, 이 시스템에서는 CGATE 전압이 RGAIN 전류에 직접적으로 영향을 미치고 연산 증폭기 출력 변화를 지체시킨다.

뉴빈은 RGATE와 CGATE가 왜 불안정성을 일으키지 않는지 자신이 생각하는 것을 말한다. “게이트 소스는 정전압입니다. 그렇다면 RGATE - CGATE 회로는 무관합니다. 게이트를 조절하기만 하면 소스가 추종할 것입니다. 소스 팔로어이기 때문입니다.”

경험 많은 동료인 구룩스는 말한다. “그렇지 않아. 그 말은 PMOS가 이 회로에서 이득 블록처럼 정상적으로 작동할 때만 해당될 수 있어.”

이에 뉴빈은 수학 공식을 떠올려 본다. PMOS 소스 대 PMOS 게이트의 동작을 직접적으로 모델링해보면 어떨까? 다시 말해서 V(VS)/V(VG)는 얼마인가? 뉴빈은 화이트 보드로 다가가서 다음과 같은 공식을 적어내려 간다...(중략)

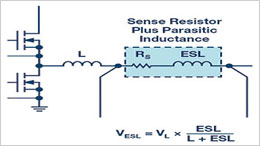

스위치 모드 전원장치의 전류 감지 - 제3부: 전류 감지 방법

조회수 15692회 / Henry Zhang 외 1인

스위치 모드 전원장치의 전류 감지 - 제1-2부: 기본 사항

조회수 8716회 / Henry Zhang 외 2인

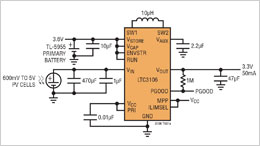

스타트/스톱 기능을 사용하는 자동차에서 인포테인먼트 시스템 구동 문제

조회수 8535회 / Bruce Haug

MOSFET 게이트 앞에 100Ω 저항을 사용하는 것이 꼭 필요할까?

조회수 12273회 / Aaron Schultz

항공우주 및 방위 산업의 과제와 해결책

조회수 7258회 / Steve Munns

무선 센서 노드를 배터리 없이 온도 차이를 이용해서 구동 ②

조회수 5832회 / Bruce Haug

Refulator™: 정밀 전압 레퍼런스이면서 200mA가 가능한 정확도 뛰어난 ...

조회수 5407회 / Michael B. Anderson

무선 센서 노드를 배터리 없이 온도 차이를 이용해서 구동 ①

조회수 5269회 / Bruce Haug

고신뢰성 전원 시스템 용으로 향상된 보호와 안전성 기능을 제공하는 IC...

조회수 5962회 / Steve Munns

PDF 다운로드

회원 정보 수정