연산 증폭기에서 잡음을 낮추기 위한 설계 도움말

글/Brian Black, Product Marketing Manager, Signal Conditioning Products,

Glen Brisebois, Senior Applications Engineer, Signal Conditioning Products, Linear Technology

실제적인 물리적 성질 때문에 정밀도, 제로 잡음, 무한한 개방 루프 이득, 슬루율, 이득-대역폭 곱이 완벽한 이상적인 연산 증폭기를 달성한다는 것은 불가능하다. 하지만 증폭기 제품이 세대를 거듭할수록 이전 제품보다 나아지고 있다는 것은 확실하다. 그렇다면 1/f 잡음이 낮은 연산 증폭기를 설계하려면 어떻게 해야 할 것인가?

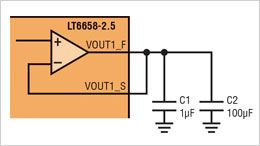

1985년에 Linear Technology의 George Erdi가 LT1028을 설계하였다. LT1028은 1kHz일 때 0.85nV/√Hz의 입력 전압 잡음 밀도와 35nVP-P의 0.1Hz~10Hz 입력 전압 잡음으로서 30년 넘게 저주파수에서 전압 잡음이 가장 낮은 연산 증폭기로 남아 있다. 그런데 올해 LT6018이라고 하는 새로운 증폭기가 등장함으로써 LT1028에 도전장을 내게 되었다. LT6018은 30nVP-P의 0.1Hz~10Hz 입력 전압 잡음과 1Hz의 1/f 코너 주파수를 달성한다. 다만 광대역 주파수의 특성은 1.2nV/√Hz이다. 그럼으로써 LT6018은 저주파 애플리케이션에서 더 낮은 잡음을 가능하게 하며, LT1028은 많은 광대역 애플리케이션에서 우수한 성능을 달성한다(그림 1).

...(중략)

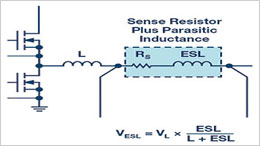

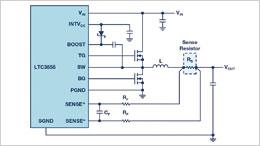

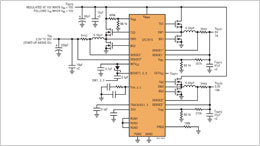

스위치 모드 전원장치의 전류 감지 - 제3부: 전류 감지 방법

조회수 15679회 / Henry Zhang 외 1인

스위치 모드 전원장치의 전류 감지 - 제1-2부: 기본 사항

조회수 8706회 / Henry Zhang 외 2인

스타트/스톱 기능을 사용하는 자동차에서 인포테인먼트 시스템 구동 문제

조회수 8531회 / Bruce Haug

MOSFET 게이트 앞에 100Ω 저항을 사용하는 것이 꼭 필요할까?

조회수 12257회 / Aaron Schultz

항공우주 및 방위 산업의 과제와 해결책

조회수 7249회 / Steve Munns

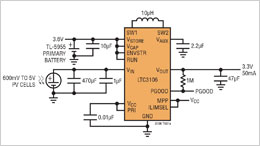

무선 센서 노드를 배터리 없이 온도 차이를 이용해서 구동 ②

조회수 5826회 / Bruce Haug

Refulator™: 정밀 전압 레퍼런스이면서 200mA가 가능한 정확도 뛰어난 ...

조회수 5400회 / Michael B. Anderson

무선 센서 노드를 배터리 없이 온도 차이를 이용해서 구동 ①

조회수 5264회 / Bruce Haug

고신뢰성 전원 시스템 용으로 향상된 보호와 안전성 기능을 제공하는 IC...

조회수 5955회 / Steve Munns

PDF 다운로드

회원 정보 수정