인텔 10나노미터 기술: 하이퍼스케일링을 활용하여 업계에서 가장 높은 로직 트랜지스터 밀도 제공

인텔의 10나노 프로세스는 3세대 핀펫 기술을 사용하여 다른 “10나노미터”기술보다 한 세대 앞선 것으로 평가됩니다. 인텔의 10나노미터 기술기반 하이퍼 스케일링을 사용하면 멀티 패터닝 의 가치를 극대화할 수 있어 인텔은 트랜지스터를 낮은 비용으로 보다 더 작게 생산할 수 있으므로 무어의 법칙에서 파생되는 경제적인 이점을 지속적으로 누릴 수 있습니다. 인텔의 10나노미터 공정기술은 클라이언트, 서버 및 기타 산업을 위한 인텔의 모든 제품을 제조하는데 사용됩니다.

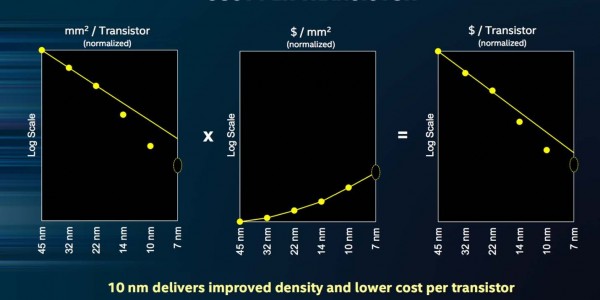

트랜지스터당 비용

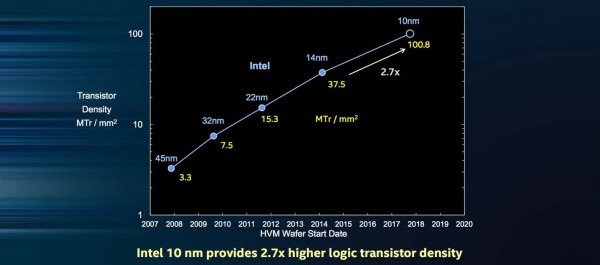

인텔 10나노미터 공정의 최소 게이트 피치는 70나노미터에서 54나노미터로 감소하였으며 최소 메탈 피치는 52나노미터에서 36나노미터로 감소되었습니다. 치수가 작아졌기 때문에 1나노미터당 100.8메가 트랜지스터의 로직 트랙지스터 밀도를 실현시킬 수 있었습니다. 이는 인텔의 이전 14나노미터 기술보다 2.7배 높으며 다른업계의 10나노미터 기술보다 약 2배 높은 것으로 평가받고 있습니다.

10나노미터 하이퍼스케일링

로직 트랜지스터 밀도

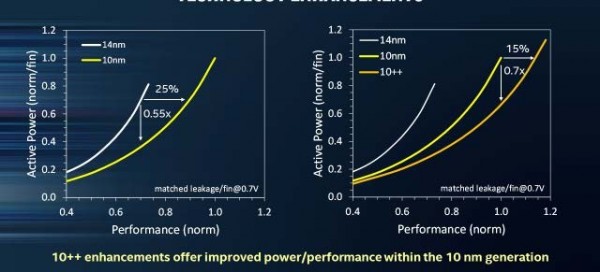

인텔의 10나노미터 공정은 이전 14나노미터 기술보다 25%향상된 성능과 45% 낮은 전력을 필요로 합니다. 10나노미터 공정을 향상시킨 10++공정은 추가적으로 10%의 성능향상 및 30%의 필요전력 감소를 실현시킵니다.

기술 향상

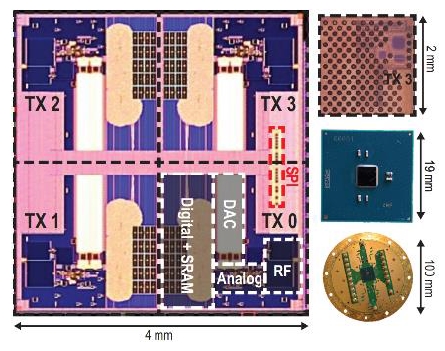

인텔 커스텀 파운드리는 10GP(범용) 및 10HPM(고성능 모바일)의 두가지 설계 플랫폼을 기반으로 고객에게 인텔 10나노미터 공정을 제공합니다. 본 플랫폼에는 IP포트폴리오를 위한 광범위한 실리콘 검증, ARM라이브러리 및 POP키트, 완전히 통합된 턴키 파운드리 서비스 및 지원이 포함되어 있습니다.

[인터뷰] 최원혁 인텔코리아 상무 / 인텔 Ultra, AI PC 시대 열었다

조회수 338회 / intel

인텔 선임 연구과학자.jpg)

코가 없는 컴퓨터 칩이 냄새를 맡는 방법

조회수 14278회 / Intel

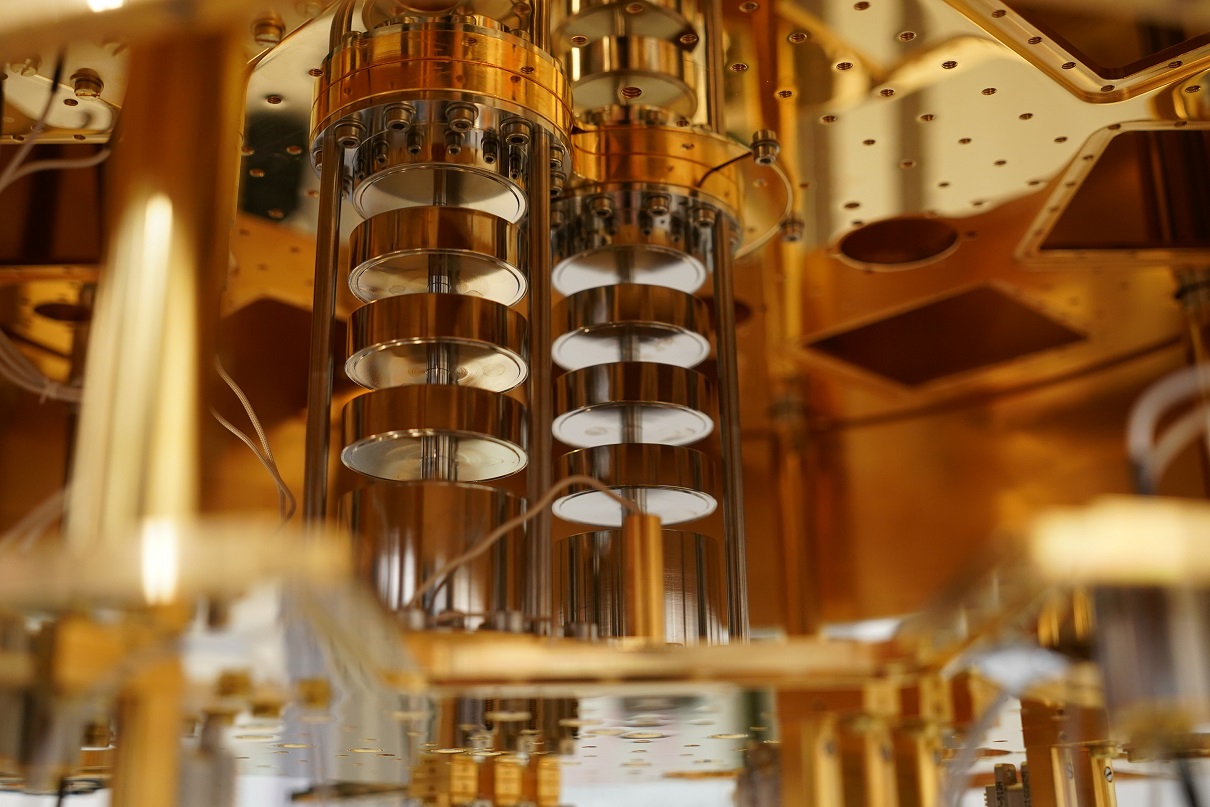

양자 확장성을 구현하는 인텔 "호스 리지"

조회수 1361회 / Intel

인텔, 엣지 AI 시장 개화를 앞당긴다 :

‘엣지 AI 포럼’을 통해 차별...

조회수 1457회 / Intel

Intel, 양자컴퓨터 실용화를 향한 여정은 이제부터 시작

조회수 1139회 / 인텔

양자 컴퓨팅 상용화로의 경주는 마라톤이다

조회수 1130회 / Intel

컴퓨팅의 다음 세대를 견인할 혁신적인 5가지 인텔 플랫폼

조회수 1659회 / Intel

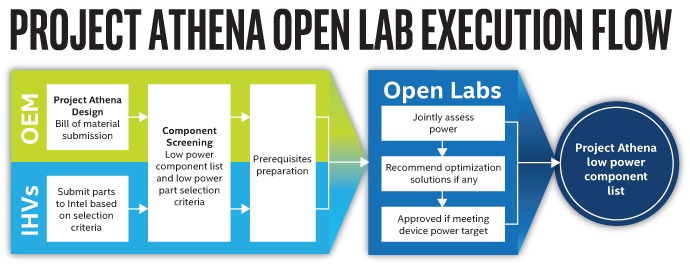

인텔, 노트북 부품 최적화를 위한 생태계 통합 확장하는 아테나 프로젝...

조회수 1854회 / Intel

인텔, 새로운 인텔® v프로™ 플랫폼 발표로 모바일 중심 시대 IT 및 직원...

조회수 2392회 / Stephanie Hallford

PDF 다운로드

회원 정보 수정