SiC MOSFET 전력 모듈의 병렬화

글/Andre Lenze, David Levett, Ziqing Zheng, Krzysztof Mainka, 인피니언 테크놀로지스

머리말

전력 반도체 병렬화에는 다양한 방법이 있을 수 있다. 가장 흔히 사용되는 방법은, 전력 모듈 내부에 칩 차원에서 병렬화를 해서 더 높은 전류 정격을 제공하는 것이다. 칩은 제한된 전류 정격으로만 설계할 수 있기 때문에, 필요로 하는 더 높은 전류 정격을 달성하기 위해서는 여러개의 칩을 병렬화해야 한다. 병렬화는 모듈 차원에서도 가능하다. 예를 들어서 6스위치 모듈의 3개 레그를 병렬로 연결해서 개별 레그 전류 정격의 3배로 하프 브리지 모듈을 달성할 수도 있다. TO-247 같은 여러 개의 개별 패키지나 모듈을 다 함께 스위칭하는 방법도 있을 수 있다. 이 글에서는 이 후자의 방법에 초점을 맞춰서 살펴보려고 한다.

IGBT 전력 모듈을 병렬화하기 위해서는 전원 레이아웃, 게이트 드라이버 설계, 열 밸런싱, 통계 분석, 자기장 효과 같은 것들에 대해서 전문성을 필요로 하며 약간의 직관력도 필요하다. SiC 전력 반도체 병렬화는 더욱 만만치 않은 과제이다. 스위칭 속도가 빨라지면 타이밍과 인덕턴스가 더 중요해지기 때문이다. 이 글에서는 여러개의 SiC MOSFET 모듈을 병렬화하기 위해서 어떤 기술적 과제들을 해결해야 할지 알아본다.

SiC 모듈 병렬화를 하는 이유

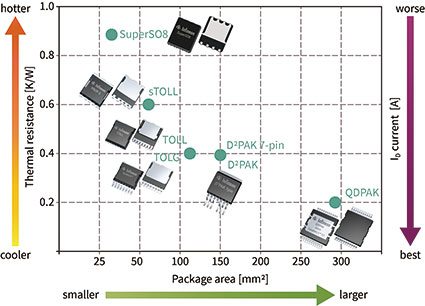

그렇다면 모듈 병렬화가 왜 필요할까? 2개 200A 모듈을 병렬화해서 400A 모듈을 달성하는 것이 어떤 점에서 이득일까? 그냥 하나의 400A 모듈을 사용하면 되지 않을까? 상업용으로 1200V 대로 IGBT 모듈은 3600A에 이르기까지 다양한 전류 정격과 다양한 패키지로 출시되어 있다. 그런데 SiC MOSFET은 높은 전류(400A 이상)로 선택폭이 제한적이다. 산업표준 패키지나 다중 소스를 사용해야 하는 경우에는 더 그렇다. 뿐만 아니라 크기가 더 작은 패키지는 크기가 크면서 생산 수량이 적은 패키지보다 더 낮은 비용으로 대량 생산할 수 있다.

하지만 모듈 병렬화의 더 큰 이유는 기술적인 것들이며, 다음과 같은 이유에서 IGBT를 사용할 때보다 SiC MOSFET을 사용할 때 병렬화가 더 중요해진다:

• 여러 개의 패키지를 사용하면 히트싱크 위로 분산시킬 수 있고 냉각을 향상시킬 수 있다. 그러므로 비싼 SiC MOSFET 모듈보다 더 높은 전류를 제공할 수 있다.

• 크기가 더 큰 패키지는 전원 루프와 게이트 드라이버 회로로 인덕턴스를 높인다. 이것은 물리적인 거리와 더 높은 전류를 전달하기 위해서 사용되는 스크류 단자 접속 때문이다.

• 다수의 칩을 사용하면 내부적으로 대칭적 레이아웃과 모든 칩들로 게이트 인덕턴스 균등화가 중요한데, 단자 옵션이 제한적인 패키지는 이러한 최적화가 어렵다.

• 크기가 더 작은 패키지를 사용하면 더 빠른 스위칭 속도와 그러므로 더 낮은 스위칭 손실이 가능하고 턴오프 시에 전압 오버슈트를 낮출 수 있다.

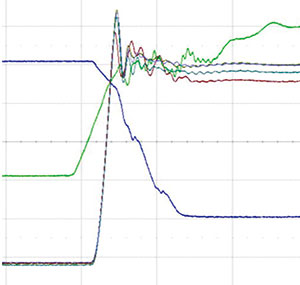

그림 1에서는 동일한 6mΩ 칩셋을 하나는 PCB 기반 모듈로 또 하나는 62mm 모듈로 패키징한 것을 보여준다. 62mm 모듈이 PCB 기반 로우프로파일 패키지에 비해서 루프 인덕턴스도 두 배 이상이고 스위칭 손실도 2배 이상이라는 것을 알 수 있다.

[그림 1] SiC MOSFET을 채택한 PCB 기반 패키지와 스크류 단자 기반 패키지 비교

IGBT와 SiC MOSFET의 병렬화 차이점

빠른 스위칭 속도에도 불구하고 SiC MOSFET 병렬화가 IGBT에 비해서 다음과 같은 점들에서 유리하다:

• SiC MOSFET은 Si IGBT의 VCEsat 특성에 비해서 RDS(on) 양의 온도 계수가 더 높다. 이 점이 정적 전류 공유 시에 부궤환으로서 동작한다. 어느 한 디바이스가 더 많은 전류를 취하면, 이 칩이나 모듈이 더 뜨거워져서 RDS(on)을 올리고 그러므로 전류를 낮춘다. 이와 같은 부궤환에 의해서 열 불균형을 감소시킨다.

• Si IGBT는 온도가 상승하는 것에 따라서 스위칭 손실이 크게 증가하고, 이것은 온도 불균형에 대해서 정궤환으로서 동작한다. 칩이 뜨거워지면 손실이 증가하고, 그래서 더 뜨거워진다. SiC MOSFET은 온도에 대해서 스위칭 손실이 아주 조금만 증가하므로 이 효과를 크게 줄일 수 있다.

• SiC MOSFET은 트랜스컨덕턴스 곡선이 더 매끄럽다. 다시 말해서 게이트 임계 구역에서 동작할 때 게이트 전압으로 작은 변화가 동급의 Si IGBT에 비해서 드레인 전류로 영향을 더 적게 미친다. 그러므로 동적 전류 공유에 도움이 된다.

• 인피니언의 트렌치 게이트 디바이스에 대한 통계 분석을 보면, 파라미터 분포에 있어서 RDS(on)이 더 높은 모듈이 스위칭 손실이 더 낮다는 것을 알 수 있다. 이것은 부품 대 부품으로 손실을 매칭시키기 위해서 도움이 된다.

테스트 플랫폼을 사용한 사례

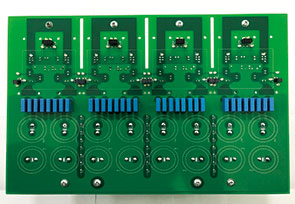

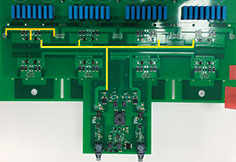

그림 2는 여러개의 SiC MOSFET 모듈을 병렬로 동작할 때 성능을 알아보기 위해서 설계한 테스트 플랫폼을 보여준다. 4개 6mΩ 1200V SiC MOSFET 하프 브리지 모듈을 병렬로 연결한 전원 PCB이다. 이 디자인 플랫폼을 예로 들어서 다음과 같은 측면들을 살펴보도록 하겠다.

[그림 2] 병렬화 테스트 플랫폼

모듈 내부 레이아웃

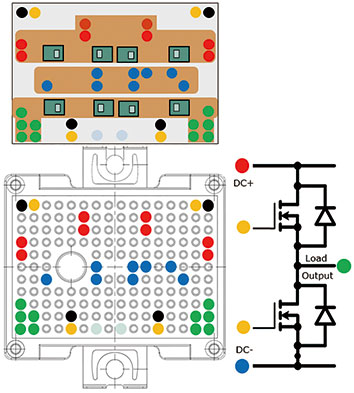

병렬화를 위해서 가장 먼저 고려해야 할 것은 모듈 내부에서의 전원 및 게이트 레이아웃이다. 그림 3에서는 다중의 칩을 병렬화할 때 전원 및 게이트 드라이버 레이아웃을 균등하고 대칭적이도록 하기 위해서 내부적 칩 레이아웃과 모듈 핀아웃을 어떻게 설계해야 할지 보여준다. 또 한편으로 이 레이아웃은 스위칭 루프 인덕턴스를 낮게 유지한다.

대체적으로 핀 그리드 어레이 방식의 PCB 기반 모듈이 레이아웃을 좀더 유연하게 최적화할 수 있다.

[그림 3] 위는 내부적 칩과 DCB 레이아웃이고, 아래는 모듈 핀아웃과 하프 브리지 토폴로지 회로도를 보여준다. 어떻게 대칭적이며 인덕턴스가 낮은 레이아웃을 달성할 수 있는지 보여준다.

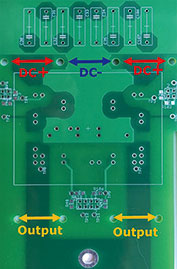

전원 PCB 레이아웃

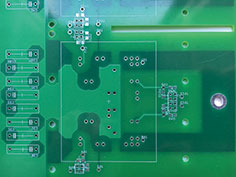

그림 3에서 보듯이 전원 레이아웃은 모듈의 양쪽 절반들로 대칭적이다. 이러한 대칭성을 이루기 위해서 그림 4에서 보는 전원 레이아웃은 나비의 날개처럼 중심선을 따라서 대칭적이다. 이렇게 함으로써 모듈 내부에서 칩들 간에 전류 공유를 균등하게 할 수 있다. 4개 모듈 각각으로도 정확하게 동일한 레이아웃을 사용해서 모듈들 사이에 전류 공유를 균등하게 했다. 외부적 스위칭 루프 인덕턴스를 낮게 유지하는 것도 중요하다. 이것은 다중의 PCB 구리 플레인을 사용해서 DC+ 및 DC- 버스 배선을 겹치게 하고 로컬 디커플링 커패시터를 사용해서 달성할 수 있다.

[그림 4] 전원 스테이지 PCB 레이아웃

게이트 드라이버 회로 설계

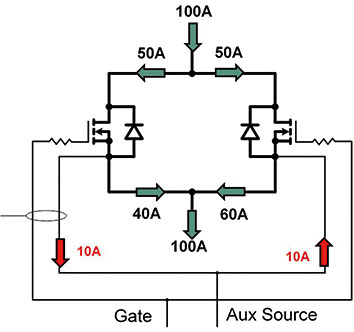

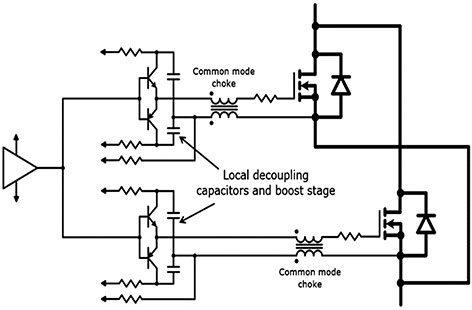

4개 모듈 모두가 공통적인 게이트 드라이버 회로를 사용하고 다중의 게이트 배선을 사용할 때는 보조 소스 배선으로 전류가 흐르는 것을 낮추는 것이 중요하다. 그림 5는 2개 모듈만 표시한 것으로서, 보조 소스 배선이 어떻게 메인 전류 경로와 함께 자연스럽게 병렬적인 전도 경로를 형성하는지 보여준다. 이와 같은 보조 소스 병렬 경로로 일부 전자가 흐를 수 있다. 이러한 전자를 “틴에이저 전자”라고 한다. 다른 전자들과 다른 경로를 취하려고 하기 때문이다. 이 전류가 충분히 크면 게이트 발진을 일으킬 수 있으며 심하면 모듈 내부적 보조 본드 와이어를 개방시킬 수도 있다.

[그림 5] 공통적 보조 소스 배선을 사용할 때 전류 흐름 경로

그림 6의 회로를 사용해서 이와 같은 원치 않는 순환 전류를 낮출 수 있다. 이 회로는 공통 모드 초크를 사용하고 있다. 이 초크가 정상적 게이트 전류에 대해서는 낮은 임피던스를 나타낸다. 그러면 입력과 출력 전류가 동일하다. 하지만 원치 않는 전원 전류에 대해서는 높은 임피던스를 나타내고 소스 배선으로만 흐른다. 공통 모드 초크와 함께, 디바이스 게이트 배선의 각기 쌍으로 각기 로컬 부스트 스테이지를 사용하고 있다. 이것은 소스 배선으로 저항을 가능하게 한다. 하지만 로컬 커패시터를 사용함으로써 이 경로로 어떠한 전류 흐름이 게이트 파형에 영향을 미치지 않는다. 단순히 소스 저항만 사용하면, 이 소스 저항으로 어떠한 전류 흐름이 게이트 소스 전압으로 영향을 미치고, 그러면 직접적 제어 능력을 낮추고 게이트 발진 가능성을 높일 수 있다.

[그림 6] 게이트 드라이버 회로

게이트 드라이버 PCB 레이아웃

그림 3에서 본 6mΩ 모듈은 듀얼 게이트 소스 핀과 듀얼 전원 드레인 및 소스 배선을 사용해서 인덕턴스를 낮추고 모듈 내부에서 SiC MOSFET 칩들 사이에 전류 공유를 향상시킨다. 게이트 레이아웃과 관련해서 가장 먼저 할 일은, 양쪽 게이트 소스 배선 쌍으로 대칭적인 레이아웃을 달성하는 것이다. 그림 7에서 보는 것과 같이, 전원 PCB 위로 메자닌 게이트 드라이버 PCB를 탑재해서 이러한 대칭성을 달성할 수 있다.

[그림 7] 게이트 드라이버 PCB의 메자닌 구조

그 다음으로 할 일은, 4개 모듈의 게이트들이 동일한 시간에 턴온 및 턴오프하도록 하는 것이다. 그림 8에서 노란색 선으로 표시된 “트리” 구조는 비슷한 길이의 인덕턴스가 낮은 게이트/소스 트레이스 쌍을 사용해서 이것을 달성한다. 또한 그림 8의 왼쪽에 주황색 선으로 표시된 것처럼, 각기 게이트/소스 배선 쌍으로 로컬 부스트 스테이지 역시도 레이아웃이 대칭적이다. 측정 결과를 보면, 스위칭 시에 게이트들 사이의 최악 상황 타이밍 스큐가 5ns 미만이라는 것을 알 수 있다.

[그림 8] 게이트 드라이버 PCB 트리 구조 레이아웃

테스트

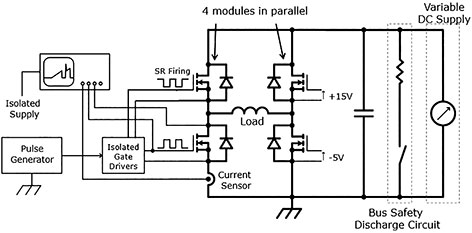

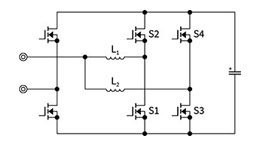

그림 9는 이중 펄스 테스트(DPT) 셋업을 보여준다. 하프 브리지로 구성된 토폴로지를 사용해서 전류가 흐르게 하고 자기장이 최종 애플리케이션과 일치하게 해서 전류 공유를 측정한다. 또한 시스템 데드 타임 요구를 충족하는 데드 타임을 사용해서 테스트 대상 상보형 디바이스로 동기 정류 스위칭 펄스를 발생시킬 수 있어야 한다.

[그림 9] 이중 펄스 테스트(DPT) 배선도

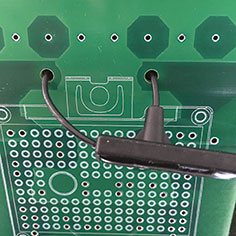

드레인 및 소스 전류를 측정하기 위해서, DC 버스 PCB 트레이스의 양쪽에 구멍을 내서 로고스키 코일을 사용할 수 있도록 했다. 그림 10은 이것을 보여주는 것으로서, DC- 버스 전류(하측 스위치 소스 전류)와 DC+ 버스 전류(상측 스위치 드레인 전류)를 측정할 수 있다. 또한 두 셋의 모듈 출력 핀들 사이에 출력 전류 평형을 측정할 수 있게 했다. 그림 11은 로고스키 코일을 사용해서 DC- 버스 전류를 측정하는 것을 보여준다.

[그림 10] 전원 모듈 PCB 레이아웃과 전류 검출 구멍

[그림 11] 로고스키 코일을 사용해서 하측 스위치 소스 전류 측정

정적 전류 공유

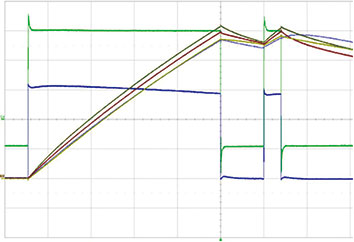

그림 12는 DPT로 측정된 4개 하측 디바이스의 소스 전류를 보여준다. 첫 번째 펄스 후에 동기 정류를 사용해서 상측 SiC MOSFET을 턴온하고 데드 타임이 이어진다. 두 번째 펄스 후에는 동기 정류를 사용하지 않는다. 그러므로 전류가 상측 바디 다이오드로 프리휠링할 수 있다. 매칭된 4개 모듈의 전류 공유는 ±3퍼센트로 측정되었다. 두 번째 펄스 후에는 전류 공유가 나빠진다는 것을 알 수 있다. 이 때는 MOSFET이 게이팅하지 않고 바디 다이오드만 전류를 전도한다.

[그림 12] 4개 병렬화 모듈의 DPT 전류 파형(50?s/div 및 50A/div). 녹색 선은 Vgs이고(5V/div), 파란색 선은 Vds이다(100V/div).

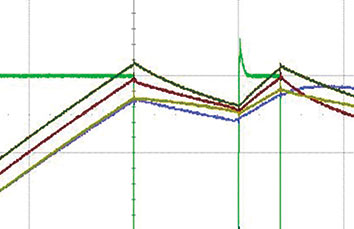

이 테스트는 RDS(on) 차이가 2퍼센트 이내이도록 선택된 모듈들로 실시한 것이다. RDS(on) 차이가 7퍼센트인 모듈들에 대해서도 테스트를 실시했는데, 전류 공유가 ±4퍼센트로서 조금밖에 나빠지지 않았다. 높은 온도로 상측 디바이스를 스위칭하면서도 테스트를 실시했는데, 마찬가지로 우수한 성능을 나타냈다. 그림 13은 그림 12의 전류 파형을 확대해서 보여준다.

[그림 13] 4개 병렬화 모듈의 DPT 전류 파형(50?s/div 및 50A/div)

동적 전류 공유

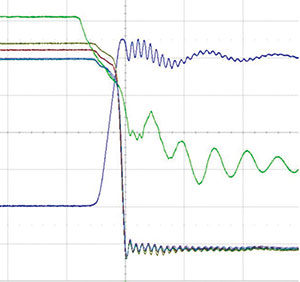

그림 14와 그림 15는 하측 디바이스들의 턴온 및 턴오프 파형을 보여주는 것으로서, 동적 공유가 우수하다는 것을 알 수 있다. 전류 발진이 관찰되지 않는데, 이것은 이 디바이스들이 턴온 및 턴오프 시에 전류 공유를 잘 한다는 것을 나타낸다. 다른 온도, 상측 디바이스, 7퍼센트 RDS(on) 차이로도 테스트를 실시했는데, 결과는 비슷하게 측정되었다.

[그림 14] 4개 병렬화 모듈의 DPT 턴오프 파형(200ns/div 및 50A/div). 녹색 선은 Vgs이고(5V/div), 파란색 선은 Vds이다(100V/div).

[그림 15] 4개 병렬화 모듈의 DPT 턴온 파형(200ns/div 및 50A/div). 녹색 선은 Vgs이고(5V/div), 파란색 선은 Vds이다(100V/div).

시험실에서가 아닌 양산 제품으로 전류 공유

시험실에서 소수의 샘플로는 전류 공유가 매우 우수한 것으로 확인되었다. 그렇다면 이 디자인을 양산에 착수했을 때 임의적으로 선택한 모듈들로 전류 공유는 어떨 것인가?

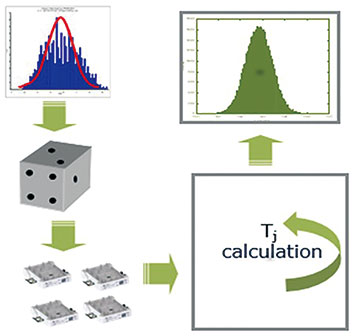

이를 위해서는 몬테 카를로 분석이라고 하는 기법을 사용할 수 있다. 이 용어는 유명한 몬테 카를로 카지노에서 따온 것이다. 그림 16은 이 분석 기법의 블록 다이어그램을 보여준다. RDS(on)과 스위칭 손실 값의 통계 분포로부터 임의적으로 4개 모듈을 선택한다. 각기 모듈의 파라미터들을 사용해서 각기 모듈로 전류와 접합부 온도를 계산할 수 있다. RDS(on)과 스위칭 손실은 온도에 대해서 종속적이므로, 반복을 통해서 각기 모듈의 최종적인 전류와 접합부 온도를 계산할 수 있다. 예를 들어서 임의적으로 선택한 5만 셋의 모듈에 대해서 이 과정을 반복하고 Tj의 정규 분포를 계산할 수 있다. 이 경우에 결과는 ±7C의 ±3시그마 편차였다. 이 계산에서 또 한 가지 알 수 있는 점은, RDS(on)과 스위칭 손실 Etot가 상관관계라는 점이다. RDS(on)이 높을수록 Etot 값이 높은 것으로 나타났다.

[그림 16] 몬테 카플로 분석 플로우 차트

맺음말

이 글에서는 4개 모듈을 병렬화했을 때 정적 및 동적 동작 조건으로 전류 공유가 우수하고 몬테 카를로 분석으로 양산 부품으로도 마찬가지로 우수한 전류 공유를 달성한다는 것을 확인했다. 전력 반도체를 병렬화할 때는 게이트 드라이버 보조 순환 전류에 주의를 기울여야 한다. 또한 엔지니어에게 무엇보다도 중요한 설계 원칙은 대칭성을 달성하는 것이다.

참고 문헌

•Infineon AN 2017-41. Evaluation Board for CoolSiC™ Easy1B half-bridge modules.

•Infineon AN 2017-04. Advanced Gate Drive Options for Silicon- Carbide (SiC) MOSFETs using EiceDRIVER™.

•Infineon AN2014-12. EiceDRIVER™ 1EDI Compact Family. Technical description.

•Infineon AN2018-09. Guidelines for CoolSiC™ MOSFET gate drive voltage window

•Infineon AN2017-14. Evaluation Board EVAL-1EDI20H12AH-SIC.

•Infineon AN2007-04. How to calculate and minimize the dead time requirement for IGBT’s properly.

•Infineon AN2017-46. CoolSiC™ 1200 V SiC MOSFET Application Note

CoolSiC™의 잠재력 최대한 활용: EiceDRIVER™ 기술이 전기차의 진보 가속화

조회수 206회 / M. Ippisch 외 1인

스마트 홈과 스마트 빌딩: 연결성과 효율

조회수 548회 / 인피니언 테크놀로지스

스마트 헬스 기기를 구현하는 반도체와 소프트웨어 솔루션

조회수 669회 / 인피니언

인피니언은 더 집중했다 “미래 세대를 위한 과감한 투자 결정”

조회수 1001회 /

혁신적인 실리콘 솔루션을 사용해서 최대의 PFC 효율 달성

조회수 777회 / Rafael Garcia

와이드 밴드갭 반도체, 최신 통신 SMPS의 설계 과제를 충족하는 방법

조회수 969회 / Francesco Di Domenico

안전한 MOSFET 동작을 위한 설계 가이드라인

조회수 3828회 / Susheel Badha 외 1인

[신년 인터뷰] “2021년 인피니언은 새로운 반열에 올라섰습니다”

조회수 1481회 / 라인하드 플로스

IoT 애플리케이션을 위한 인피니언의 솔루션

조회수 1013회 / 인피니언

PDF 다운로드

회원 정보 수정