업계의 새로운 기준이 될 OptiMOS™ 소스 다운 전력 MOSFET

글/Bastian Lang, Product Marketing Manager, 인피니언 테크놀로지스

최종 애플리케이션의 에너지 효율, 전력 밀도, 견고성, 수명을 향상시키기 위해서는 열 관리가 중요하다. 실리콘 기술이 발전하면서 주요 성능 파라미터들이 지속적으로 향상되어 왔으나, 패키지 디자인은 그러하지 못했다. 그런데 이제 인피니언이 새로운 소스 다운(Source-Down) 패키지를 도입하고 이 패키지를 적용한 새로운 제품군을 출시함으로써 업계의 새로운 기준을 제시하게 되었다.

드레인 다운 대 소스 다운

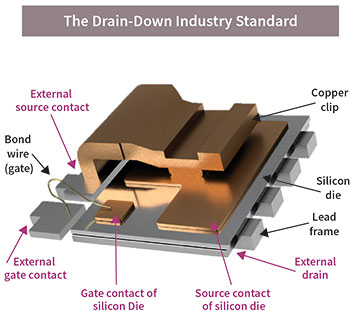

그림 1의 왼쪽 그림은 PQFN 3.3 x 3.3mm 패키지로 최신 수직 트렌치 전력 MOSFET의 내부 구조를 보여준다. 이 아키텍처에서는 리드 프레임이 토대를 이룬다. 하단부의 드레인 연결부가 아래로 향하게 해서 박막 실리콘 다이를 얹는다. 수직 트렌치 MOSFET에서는 전류가 수직으로 흘러서 전기적 연결을 한다. n-채널 전력 MOSFET의 동적 트렌치는 통상적으로 상단부인 소스 측에 자리잡는다. 실리콘 다이의 소스 연결부는 구리 클립을 사용해서 형성되고, 이것이 실리콘 다이의 상단부와 리드 프레임 부분을 연결한다. 게이트 연결부 역시 동적 트렌치 측에 자리잡으며 통상적으로 본드 와이어를 사용해서 리드 프레임으로 연결된다. 이렇게 해서 모든 3개의 전기적 연결부를 리드 프레임으로 연결하고, MOSFET을 PCB로 탑재한다.

[그림 1] PQFN 3.3 x 3.3mm 드레인 다운 전력 MOSFET(왼쪽)과 PQFN 3.3 x 3.3mm 소스 다운 전력 MOSFET(오른쪽)의 내부 구조

소스 다운 컨셉

이 새로운 접근법은 단순하면서도 혁신적이다. MOSFET 패키지 안에서 실리콘 다이의 위아래를 뒤집은 것이다. 그러므로 드레인 전위가 아니라 소스 전위가 리드 프레임으로 연결된다. 그림 1의 오른쪽은 새로운 소스 다운 패키지의 구조를 보여준다. 실리콘 다이의 게이트 연결부와 소스 연결부를 리드 프레임 상에 바로 형성한다. (다이 상단으로부터) 드레인의 전기적 연결은 매우 큰 구리 클립을 사용해서 이루어진다.

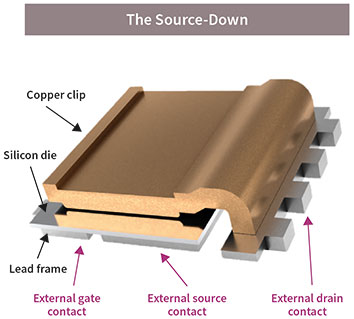

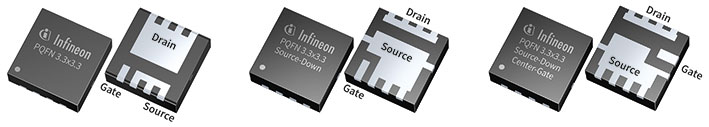

그림 2는 PQFN 3.3 x 3.3mm OptiMOS™ MOSFET 제품군의 다양한 풋프린트를 비교해서 보여준다. 드레인, 소스, 게이트의 전기적 연결이 위치가 여전히 동일하므로 손쉽게 바로 교체할 수 있다.

새로운 소스 다운 기술을 사용해서 두 가지 새로운 풋프린트를 제공한다. 소스 다운 표준 게이트(그림 2b)와 소스 다운 센터 게이트(그림 2c)이다.

[그림 2] (a) 표준적 PQFN 3.3 x 3.3mm, (b) 새로운 소스 다운 PQFN 3.3 x 3.3mm, (c) 새로운 소스 다운 센터 게이트 PQFN 3.3 x 3.3mm 패키지 풋프린트

소스 다운 패키지의 이점

이들 새로운 풋프린트는 다음과 같은 이점을 제공한다:

1) RDS(on) 향상

2) 열 저항 감소

3) 열 관리 향상

RDS(on): 다이를 위아래를 뒤집음으로써 표준 드레인 다운 디바이스의 구조적 한계점들을 극복한다. 훨씬 더 큰 다이를 사용할 수 있고, RDS(on)을 30%까지 낮출 수 있다. 낮아진 RDS(on)은 해당 애플리케이션의 I2R 손실을 낮추고 전력 밀도를 높이는 것으로 이어진다.

열 관리: 열 관리는 전력 반도체 디자인에서 무엇보다도 중요하게 고려해야 할 요소이다. 열을 통제함으로써 최종 디바이스 수명을 길게 하고 전력 밀도를 높일 수 있다. 소스 다운 패키지는 다양한 측면에서 열을 낮출 수 있다. RDS(on)을 크게 낮추는 것이 열에 영향을 미친다. 디바이스의 손실을 낮추고, 결과적으로 디바이스 온도를 낮춘다. 수직형 전력 MOSFET의 동적 트렌치는 실리콘 다이의 소스 측에 자리잡는다. 이 부위에서 동작 시에 대부분의 손실이 발생되고 이러한 손실은 열로 이어진다. 기존의 드레인 다운 디바이스는 이러한 열을 실리콘에서 드레인 측으로 전달하고 드레인 측에서 리드 프레임으로 그리고 PCB로 전달해야 한다.

그런데 소스 다운 디바이스는 다이의 위아래를 뒤집으로써 실리콘 다이의 이러한 동적 트렌치가 곧바로 구리 리드 프레임과 맞닿는다. 그러므로 이러한 트렌치에서 발생된 열을 리드 프레임을 거쳐서 곧바로 PCB로 전도시킬 수 있다. 그러므로 이 새로운 구조는 Rthjc를 1.8K/W에서 1.4K/W로 22퍼센트 낮출 수 있다.

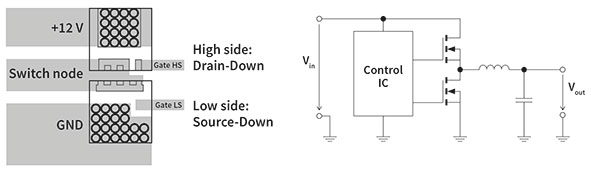

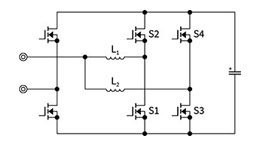

소스 다운 패키지는 하프 브리지나 풀 브리지 구성으로 몇 가지 장점을 들 수 있다. PCB의 구리 영역과 MOSFET의 열 패드를 연결하면 MOSFET으로 발생된 손실을 소산시키는 데 매우 유용하다. 그림 3a는 널리 사용되는 동기 벅 컨버터의 회로도를 보여준다. 상측 FET의 드레인 전위는 입력 전압으로 연결하고, 하측 FET의 소스 접점은 GND 전위로 연결한다. 상측 디바이스의 소스 전위를 하측 MOSFET의 드레인으로 연결해서 스위치 노드를 형성한다. 하프 브리지의 하측으로 드레인 다운 디바이스를 사용하면 열 패드가 스위치 노드 영역으로 연결될 것이다. 스위치 노드 전위는 변조 파형이므로 VIN과 GND 전위 사이에서 널뛰기한다. 시스템으로 유입되는 노이즈를 줄이기 위해서는 이 영역을 최소화해야 하는데, 그러면 하측 MOSFET의 열 관리 능력을 제한한다. 소스 다운 패키지는 이 문제를 극복할 수 있다. 하측 MOSFET의 열 패드가 접지 전위로 연결되기 때문이다. 접지 영역은 대체로 넓게 하므로 소스 다운 디바이스의 큰 열 패드와 함께 히트싱크로서 활용할 수 있다. 또한 디바이스 바로 하단으로 GND 전위로 열 비아를 손쉽게 사용할 수 있다. 그림 3b는 PCB 레이아웃 예를 보여준다. +12V와 GND의 두 전위가 널뛰기하지 않고 안정적일 것이다.

이러한 점들을 종합했을 때 새로운 소스 다운 패키지는 다음과 같은 세 가지 특징에 의해서 우수한 열 관리를 달성할 수 있다:

- RDS(on) 크게 감소

- Rthjc 22% 감소

- 레이아웃 최적화

[그림 3] (a) 하프 브리지 MOSFET 구성을 사용해서 구현된 동기 벅 컨버터 회로도, (b) 하프 브리지 MOSFET 구성으로 드레인 다운(상측)과 소스 다운(하측) 디바이스를 사용한 레이아웃 예

병렬 동작

OR-ing이나 배터리 보호 같은 애플리케이션은 정적으로 높은 전류를 처리해야 한다. 그러므로 시스템에서 손실을 제한하고 온도를 허용 가능한 수준으로 유지하기 위해서 극히 낮은 온(on) 상태 저항이 중요하다. 극히 낮은 RDS(on)을 달성하기 위해서는 다중의 MOSFET을 병렬로 연결할 수 있다. 센터 게이트 패키지는 드레인과 소스 접점 사이에 연면거리가 넓으므로, 비아를 통해서 배선하고 보드 상의 다른 레이어로 연결하는 것이 아니라, 단일 PCB 레이어로 다중 디바이스의 게이트들을 연결할 수 있다.

애플리케이션 차원의 이점

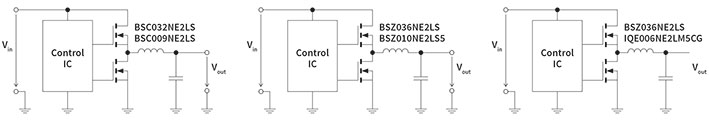

실제 사례를 통해서 새로운 소스 다운 패키지가 어떻게 유리한지 살펴보자. 그림 4는 현재 출시되어 있는 최상급의 디바이스들을 사용해서 벅 컨버터를 설계한 것을 보여준다. (a)는 PQFN 5 x 6mm 솔루션을 사용하고, (b)는 최신의 PQFN 3.3 x 3.3mm 디바이스를 사용하고, (c)는 소스 다운 솔루션을 사용한 것이다.

[그림 4] (a) PQFN 5 x 6mm 솔루션, (b) 최신의 PQFN 3.3 x 3.3mm, (c) 소스 다운 솔루션 사용

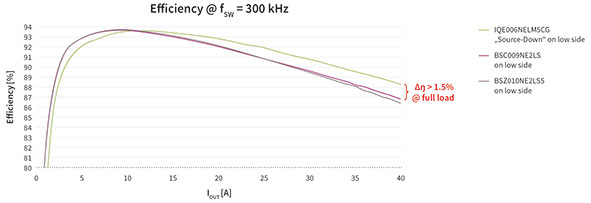

그림 5는 이 애플리케이션에서의 효율을 보여준다. 소스 다운 솔루션이 다른 두 솔루션보다 우수하다는 것을 알 수 있다. 예를 들어서 풀부하로 1.5퍼센트의 효율 향상이 가능하다. 풀부하로 효율을 향상시킴으로써 최종 애플리케이션에서 더 높은 전력 밀도를 달성할 수 있다. 효율과 함께, 정적 스위치로서 디바이스의 열 성능도 분석했다. 혁신적인 소스 다운 패키지를 적용함으로써, PQFN 3.3 x 3.3mm 풋프린트로 훨씬 더 큰 실리콘 다이를 하우징할 수 있고 RDS(on)을 크게 향상시킬 수 있다. 뿐만 아니라 Rthjc도 개선되므로 소스 다운 디바이스는 통상적인 풋프린트 디바이스들보다 훨씬 낮은 온도로 동작할 수 있다. 20A 정전류로 최신 PQFN 3.3 x 3.3mm 솔루션보다 10℃ 더 낮게 동작할 수 있다.

[그림 5] 그림 4에서 설명한 다양한 MOSFET 구성의 시스템 효율

업계의 새로운 기준 제시

전력 MOSFET에 소스 다운 패키지를 적용함으로써 레이아웃과 관련된 제약들을 극복할 수 있다. 디바이스의 전기적 및 열 성능 파라미터를 향상시킬 뿐만 아니라 시스템 설계에 있어서 새로운 차원의 유연성을 가능하게 한다. 새로운 혁신적인 패키지를 적용해서 한계를 극복하고 이전에 달성할 수 없던 수준의 애플리케이션 성능을 달성할 수 있다.

CoolSiC™의 잠재력 최대한 활용: EiceDRIVER™ 기술이 전기차의 진보 가속화

조회수 206회 / M. Ippisch 외 1인

스마트 홈과 스마트 빌딩: 연결성과 효율

조회수 548회 / 인피니언 테크놀로지스

스마트 헬스 기기를 구현하는 반도체와 소프트웨어 솔루션

조회수 674회 / 인피니언

인피니언은 더 집중했다 “미래 세대를 위한 과감한 투자 결정”

조회수 1001회 /

혁신적인 실리콘 솔루션을 사용해서 최대의 PFC 효율 달성

조회수 777회 / Rafael Garcia

와이드 밴드갭 반도체, 최신 통신 SMPS의 설계 과제를 충족하는 방법

조회수 970회 / Francesco Di Domenico

안전한 MOSFET 동작을 위한 설계 가이드라인

조회수 3829회 / Susheel Badha 외 1인

[신년 인터뷰] “2021년 인피니언은 새로운 반열에 올라섰습니다”

조회수 1481회 / 라인하드 플로스

IoT 애플리케이션을 위한 인피니언의 솔루션

조회수 1014회 / 인피니언

PDF 다운로드

회원 정보 수정